# Synthesis of Machine Code: Algorithms and Applications

By

#### Venkatesh Srinivasan

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

(Computer Sciences)

at the

UNIVERSITY OF WISCONSIN-MADISON

2017

Date of final oral examination: 02/28/2017

The dissertation is approved by the following members of the Final Oral Committee:

Thomas Reps, Professor, Computer Sciences

Somesh Jha, Professor, Computer Sciences

Benjamin Liblit, Associate Professor, Computer Sciences

Aws Albarghouthi, Assistant Professor, Computer Sciences

Parameswaran Ramanathan, Professor, Electrical and Computer Engineering

Dedicated to my Amma and Appa

# Acknowledgments

My years in graduate school have been the most enlightening, transformative, and adventurous years of my life. I am indebted to so many people for having supported me along the way. This dissertation would not have been possible without them; I would like to express my sincere gratitude to all of them.

First and foremost, I would like to thank Prof. Thomas Reps, my advisor, for his patience, guidance, and support over the course of my graduate studies. Tom was my ideal advisor: he gave me the time to discover my interests, the freedom to choose my projects, the expertise to tackle difficult problems, and the motivation to successfully complete papers. He refined my taste in research: he taught me how to identify important problems, craft elegant solutions, and write succinct papers. The spectrum of things I learned from Tom spans all the way from excellent editing skills to quirky idioms.<sup>1</sup> Tom: you inspired me to be a good researcher, and I assure you that I will sincerely strive to be one.

I would like to thank the members of my committee: Prof. Somesh Jha, Prof. Benjamin Liblit, Prof. Aws Albarghouthi, and Prof. Parameswaran Ramanathan, for their insightful discussions and comments that helped me vastly improve this dissertation.

I would like to thank the late Prof. Susan Horwitz for introducing me to the amazing world of PL research through her CS 701 course. Without her and her offering of CS 701, I would have never gotten the opportunity to work with Tom, and this dissertation would not have existed today.

I would also like to thank Prof. Murali Krishna Ramanathan for being my mentor over the course of my Ph.D. When I was on the verge of quitting, Murali gave me the motivation to toughen up and persist, as well as practical tips to keep progressing in research.

I would like to thank Tushar Sharma and Ara Vartanian for being stellar collaborators. Tushar and Ara shaped my half-baked ideas into elegant solutions with their expertise, and helped me finish the projects in time.

I could not have finished the implementation of my tools without the immense help provided by the folks at GrammaTech. Junghee Lim, Suan Yong, Brian Alliet, and Tom

<sup>&</sup>lt;sup>1</sup>There were countless times when Tom alerted me before I was about to throw the baby out along with the bath water, or when I was circling the wagons and shooting inward.

Johnson have promptly answered my millions of questions over the last five years. I would also like to thank Alexey Loginov and David Melski for their helpful comments during the design phases of my tools.

I would like to thank Peter Ohmann for being a superb peer over the course of my Ph.D. Peter was always there by my side, eager to help me; whether it was discussing potential research ideas or "channeling his inner Somesh" (asking difficult big-picture questions) to prepare me for conference talks and exams. I would like to thank my big brother in the group, Tushar Sharma, for always looking out for me, especially during my initial years. I would like to thank my wonderful office mate, Jason Breck, for patiently listening to all the boring unsolicited advice I've been showering upon him for the last three years. I would like to thank the present and past members of the PL group, especially Drew Davidson, Bill Harris, Evan Driscoll, Aditya Thakur, Alisa Maas, and Stephen Lee, for attending my practice talks, and providing useful suggestions for improving my talks.

I would like to thank my friends for bringing fun, excitement, and happiness into my boring and monotonous life. I would like to thank Karthik anna and Madhu for being close by me through good times, and even closer during tough ones; Ramki for being my best mate, my pillar of strength, and my trusted source of cringeworthy dad jokes for the past three years; Srinath for being the sane, logical, and dependable friend in my otherwise insane circle of friends; Ashwin and Smrithi for making sure I have some fun in between projects; Hari for being my therapist, and patiently listening to my countless whines and complaints; Divy for being an amazing roommate and friend; Thanu anna for being my coffee-break pal and job-search counselor; my "kids" (Nivetha, Kausik, and Anshul) for making me sometimes feel young and carefree; Andrea for being my party companion, and teaching me some essential life skills; Srikant, Arvind, Naveen, Sanath, and Venkatanathan for being awesome friends.

I would like to thank my cousin Madhusudhan and his wife Melissa for taking care of me when I arrived as a clueless twenty-one-year-old in the U.S., and providing moral support through some testing times. My stays at their place were the rare instances of my feeling at home in the U.S.

I would like to thank my grandparents for being an integral part of my life and childhood. I would like to thank my *paati* for her abundant affection. She taught me the values of patience and sacrifice, and I hope I can one day be the strong-willed person that she is. I would like to thank my late *thatha* for making my education his number-one priority, and providing all the support and encouragement I needed to excel in my studies. I would also like to thank my *mama* (uncle) and *mami* (aunt) for their love and support, and for taking care of my parents while I was away.

I don't think a few words in the acknowledgements section of this dissertation are even remotely enough to covey my gratitude towards my parents. I have the best parents a son could possibly ask for: they showered me with love, taught me important values, provided me ample support and encouragement, nurtured me to carve out my own identity, and helped me cross extremely difficult times. They strived to provide me the best possible environment to grow up in; even if it meant that they had to fight against all odds and make countless sacrifices. I would like to thank my amma for her unconditional love and unfaltering support. She fostered my curiosity and creativity in so many ways, from doing flame-test experiments (for salt analysis) with me in our kitchen to teaching me the basics of Carnatic music and embroidery. She showed me how one can achieve anything one aims for with diligence and determination. I would like to thank my appa for being my rock: he was always there for me by my side to offer his support. Observing him as I grew up, I learned what it meant to always be there for one's family. My parents often tell me that they are blessed to have a son like me. However, I think I am twice as blessed to have parents like them. *Amma* and *appa*: thank you for everything. I humbly dedicate this dissertation to you.

I would like to end this section with the following verses my *appa* taught me when I was ten. These verses have given me hope during times when I thought I had none.

विना वेङ्कटेशं न नाथो न नाथः सदा वेङ्कटेशं स्मरामि स्मरामि । हरे वेङ्कटेश प्रसीद प्रसीद प्रियं वेङ्कटेश प्रयच्छ प्रयच्छ ॥

This dissertation is supported, in part, by a gift from Rajiv and Ritu Batra; by DARPA under cooperative agreement HR0011-12-2-0012; by AFRL under DARPA MUSE award FA8750-14-2- 0270, DARPA STAC award FA8750-15-C-0082, and DARPA CRASH award FA8650-10-C-7088; by NSF under grant CCF-0904371; and by the UW-Madison Office of the Vice Chancellor for Research and Graduate Education with funding from the Wisconsin Alumni Research Foundation. Any opinions, findings, and conclusions or recommendations expressed in this dissertation are those of the author, and do not necessarily reflect the views of the sponsoring agencies. The author's advisor Thomas Reps has an ownership interest in GrammaTech, Inc., which has licensed elements of the technology reported in this dissertation.

# Contents

| Contents |             |                                                        |      |  |  |  |

|----------|-------------|--------------------------------------------------------|------|--|--|--|

| Li       | st of       | Figures, Tables, and Listings                          | viii |  |  |  |

| A        | bstra       | ct                                                     | xii  |  |  |  |

| 1        | Intr<br>1.1 | roduction Algorithms for Machine-Code Synthesis 2      | 1    |  |  |  |

|          | 1.2         | Binary Rewriting via Synthesis 4                       |      |  |  |  |

| 2        | Bac         | Background 9                                           |      |  |  |  |

|          | 2.1         | IA-32 Primer 9                                         |      |  |  |  |

|          |             | 2.1.1 Syntax 9                                         |      |  |  |  |

|          |             | 2.1.2 Semantics <i>10</i>                              |      |  |  |  |

|          | 2.2         | Quantifier-Free Bit-Vector (QFBV) Logic Formulas 11    |      |  |  |  |

|          |             | 2.2.1 Syntax <i>11</i>                                 |      |  |  |  |

|          |             | 2.2.2 Semantics 13                                     |      |  |  |  |

|          |             | Part I Algorithms                                      |      |  |  |  |

| 3        | Syn         | thesis of Machine Code from Semantics                  | 15   |  |  |  |

|          | 3.1         | Overview 16                                            |      |  |  |  |

|          |             | 3.1.1 The Role of Templatized Instruction-Sequences 20 |      |  |  |  |

|          | 3.2         | Algorithm 20                                           |      |  |  |  |

|          |             | 3.2.1 Synthesis Loop 20                                |      |  |  |  |

|          |             | 3.2.2 Pruning the Synthesis Search-Space 26            |      |  |  |  |

|          |             | 3.2.3 Divide-and-Conquer 29                            |      |  |  |  |

|          |             | 3.2.4 Correctness 33                                   |      |  |  |  |

|          |             | 3.2.5 Variations on the Basic Algorithm 34             |      |  |  |  |

|          | 3.3         | Implementation 36                                      |      |  |  |  |

|          |             |                                                        |      |  |  |  |

|   | 3.4  | Experiments 37                                     |    |  |  |  |  |

|---|------|----------------------------------------------------|----|--|--|--|--|

|   | 3.5  | Related Work 40                                    |    |  |  |  |  |

| 1 | Sno  | ading-un Machina-Coda Synthasis                    | 43 |  |  |  |  |

| 4 | 4.1  | Speeding-up Machine-Code Synthesis 4.1 Overview 44 |    |  |  |  |  |

|   | 7.1  | 4.1.1 Limitations of the McSynth Algorithm 45      |    |  |  |  |  |

|   |      | 4.1.2 Overview of McSynth++ 46                     |    |  |  |  |  |

|   | 4.2  | Algorithm 51                                       |    |  |  |  |  |

|   | 1.2  | 4.2.1 Divide Phase 51                              |    |  |  |  |  |

|   |      | 4.2.2 Conquer Phase 55                             |    |  |  |  |  |

|   |      | 4.2.3 Pragmatics 57                                |    |  |  |  |  |

|   |      | 4.2.4 Correctness 58                               |    |  |  |  |  |

|   | 4.3  | Implementation 59                                  |    |  |  |  |  |

|   | 4.4  | Experiments 59                                     |    |  |  |  |  |

|   | 4.5  | Related Work 63                                    |    |  |  |  |  |

|   | 1.0  |                                                    |    |  |  |  |  |

| 5 | Mo   | del-Assisted Machine-Code Synthesis                | 65 |  |  |  |  |

|   | 5.1  | Overview 67                                        |    |  |  |  |  |

|   |      | 5.1.1 Limitations of McSynth++ 67                  |    |  |  |  |  |

|   |      | 5.1.2 Overview of McSynth-ML 69                    |    |  |  |  |  |

|   | 5.2  | Algorithm 73                                       |    |  |  |  |  |

|   |      | 5.2.1 Training Phase 73                            |    |  |  |  |  |

|   |      | 5.2.2 Synthesis Phase 74                           |    |  |  |  |  |

|   |      | 5.2.3 Correctness 77                               |    |  |  |  |  |

|   |      | 5.2.4 Threats to Validity 78                       |    |  |  |  |  |

|   | 5.3  | Implementation 79                                  |    |  |  |  |  |

|   | 5.4  | Experiments 79                                     |    |  |  |  |  |

|   | 5.5  | 5 Related Work 83                                  |    |  |  |  |  |

|   |      |                                                    |    |  |  |  |  |

|   |      | Part II Applications                               |    |  |  |  |  |

| 6 | Parl | tial Evaluation of Machine Code                    | 87 |  |  |  |  |

| U | 6.1  | Background 89                                      | 07 |  |  |  |  |

|   | J.1  | 6.1.1 Partial Evaluation 90                        |    |  |  |  |  |

|   |      | 6.1.2 Slicing 92                                   |    |  |  |  |  |

|   | 6.2  | Overview 92                                        |    |  |  |  |  |

|   | 6.3  | Algorithm 100                                      |    |  |  |  |  |

|   |      | ()                                                 |    |  |  |  |  |

|    |                  | 6.3.1 Pre-processing: Decoupling Instructions 100           |     |

|----|------------------|-------------------------------------------------------------|-----|

|    |                  | 6.3.2 Intraprocedural Partial Evaluation 101                |     |

|    |                  | 6.3.3 Interprocedural Partial Evaluation 108                |     |

|    |                  | 6.3.4 Correctness 110                                       |     |

|    |                  | 6.3.5 Threats to Validity 112                               |     |

|    | 6.4              | Implementation 113                                          |     |

|    | 6.5              | Experiments 115                                             |     |

|    |                  | 6.5.1 Optimization via Specialization 115                   |     |

|    |                  | 6.5.2 Component Extraction 116                              |     |

|    | 6.6              | Related Work 118                                            |     |

| 7  | Δn               | Improved Algorithm for Slicing Machine Code                 | 120 |

| ,  | 7.1              | Background 122                                              | 120 |

|    | 7.1              | 7.1.1 Other platforms for machine-code slicing. <i>125</i>  |     |

|    | 7.2              | Overview 125                                                |     |

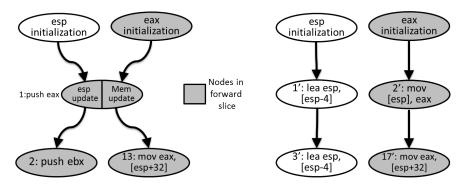

|    |                  | 7.2.1 Granularity Issue in Machine-Code Slicing 126         |     |

|    |                  | 7.2.2 Improved Machine-Code Slicing in McSlice 128          |     |

|    | 7.3              | Algorithm 132                                               |     |

|    |                  | 7.3.1 Construction of μ-SDG and Slicing 132                 |     |

|    |                  | 7.3.2 Reconstituting an Executable Machine-Code Program 137 |     |

|    | 7.4              | Implementation 140                                          |     |

|    | 7.5              | Experiments 141                                             |     |

|    |                  | 7.5.1 Extracting Executable Components from Binaries 144    |     |

|    | 7.6              | Related Work 144                                            |     |

| 3  | Con              | aclusion and Future Directions                              | 146 |

| A  | App              | pendix                                                      | 151 |

| Bi | Sibliography 163 |                                                             |     |

|    |                  |                                                             |     |

# List of Figures, Tables, and Listings

| Figure 2 | 2.1  | Some common IA-32 instructions                                                                                                                                            | 9  |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2 | 2.2  | Valuation functions for instructions in Fig. 2.1                                                                                                                          | 10 |

| Figure   | 2.3  | Syntax of L[IA-32]                                                                                                                                                        | 11 |

| Figure   | 3.1  | Master-slave architecture of McSynth                                                                                                                                      | 16 |

| Listing  | 3.2  | Strawman algorithm to synthesize instructions from a QFBV formula $\;\;$ .                                                                                                | 21 |

| Listing  | 3.3  | Algorithm SimplifyWithTest                                                                                                                                                | 25 |

| Listing  | 3.4  | Algorithm CEGIS                                                                                                                                                           | 26 |

| Listing  | 3.5  | Algorithm McSynthSlave                                                                                                                                                    | 27 |

| Figure   | 3.6  | Depiction of the set $I^{\#}$                                                                                                                                             | 29 |

| Listing  | 3.8  | Algorithm McSynthMaster                                                                                                                                                   | 30 |

| Listing  | 3.9  | Algorithm IsFlowDependent                                                                                                                                                 | 31 |

| Listing  | 3.10 | Algorithm EnumerateSplits                                                                                                                                                 | 32 |

| Listing  | 3.11 | Algorithm McSynth                                                                                                                                                         | 33 |

| Listing  | 3.14 | Algorithm Biased McSynth                                                                                                                                                  | 35 |

| Figure   | 3.15 | Comparison of synthesis time and search-space size with and without footprint-                                                                                            |    |

|          |      | based search-space pruning                                                                                                                                                | 37 |

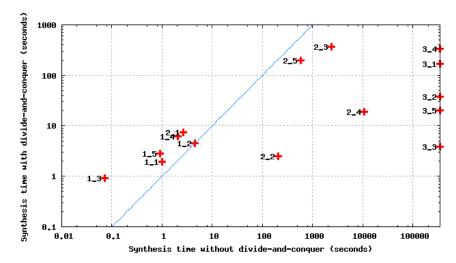

| Figure   | 3.16 | Synthesis times using the divide-and-conquer strategy                                                                                                                     | 38 |

| Figure   | 3.17 | Synthesis times with and without divide-and-conquer                                                                                                                       | 39 |

| Table :  | 3.18 | Comparison of the lengths of synthesized and original instruction-sequences                                                                                               | 40 |

| Listing  | 4.1  | Algorithm ImprovedIsFlowDependent                                                                                                                                         | 52 |

| Listing  | 4.2  | $Algorithm \ McSynth + + Master \ \dots $                           | 53 |

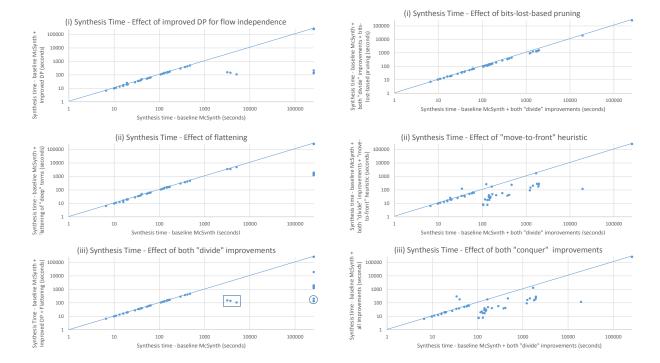

| Figure 4 | 4.5  | $Synthesis\ times\ obtained\ via\ improvements\ to\ the\ "divide"\ phase\ in\ McSynth++$                                                                                  |    |

|          |      | for the corpus of 50 QFBV formulas                                                                                                                                        | 61 |

| Figure 4 | 4.6  | Synthesis times obtained via improvements to the "conquer" phase in Mc-                                                                                                   |    |

|          |      | $Synth + + \text{ for the corpus of 50 QFBV formulas.} \dots \dots$ | 61 |

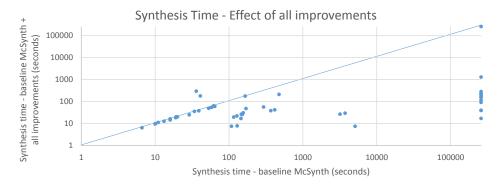

| Figure 4 | 4.7  | Effect of all improvements in McSynth++ for the corpus of 50 QFBV formulas.                                                                                               | 62 |

| Table   | 4.8  | Comparison of residual-code-synthesis time using McSynth and McSynth++,                                                                |     |

|---------|------|----------------------------------------------------------------------------------------------------------------------------------------|-----|

|         |      | respectively, in WiPEr                                                                                                                 | 63  |

| Listing | 5.1  | Algorithm TrainModels                                                                                                                  | 74  |

| Listing | 5.2  | Algorithm TruncateInstrPool                                                                                                            | 75  |

| Listing | 5.3  | Algorithm McSynthMLSlave                                                                                                               | 76  |

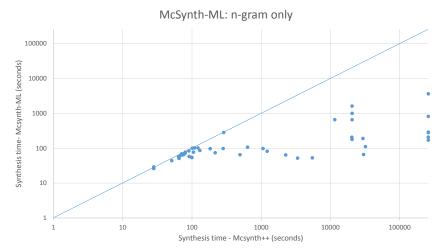

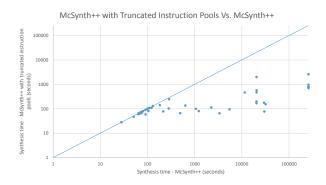

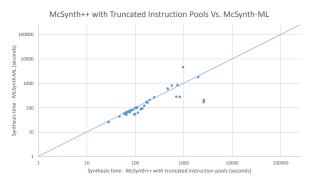

| Figure  | 5.6  | Effect of only the n-gram model assisting McSynth-ML's best-first search for the                                                       |     |

|         |      | corpus of 50 QFBV formulas                                                                                                             | 80  |

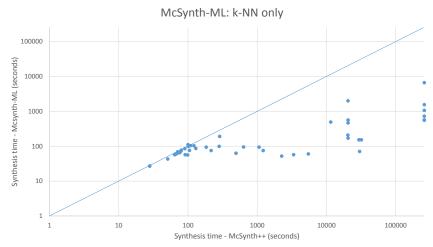

| Figure  | 5.7  | Effect of only k-NN regression assisting McSynth-ML's best-first search for the                                                        |     |

|         |      | corpus of 50 QFBV formulas                                                                                                             | 81  |

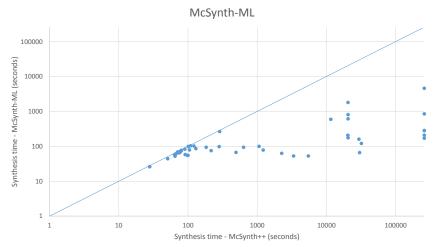

| Figure  | 5.8  | Effect of both models assisting McSynth-ML's best-first search for the corpus of                                                       |     |

|         |      | 50 QFBV formulas                                                                                                                       | 81  |

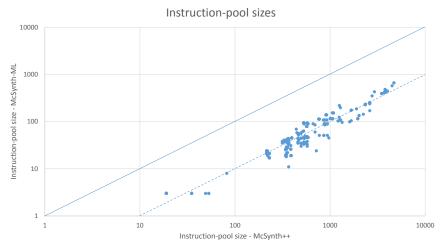

| Figure  | 5.9  | Reduction in instruction-pool sizes caused by McSynth-ML's k-NN-based trun-                                                            |     |

|         |      | cation                                                                                                                                 | 82  |

| Figure  | 5.10 | $ Effect \ of \ k-NN-based \ instruction-pool \ truncation \ on \ McSynth++ \ for \ the \ corpus$                                      |     |

|         |      | of 50 QFBV formulas                                                                                                                    | 83  |

| Figure  | 5.11 | $Comparison \ of \ McSynth-ML \ against \ McSynth++ \ with \ truncated \ instruction$                                                  |     |

|         |      | pools                                                                                                                                  | 83  |

| Figure  | 6.1  | Input power program—computes $(a+b)^n$                                                                                                 | 90  |

| Figure  | 6.2  | Residual power <sub>R</sub> program—computes $(a+1)^4$                                                                                 | 90  |

| Figure  | 6.3  | Example program foo to illustrate lifting                                                                                              | 91  |

| Figure  | 6.4  | Residual foo_r program                                                                                                                 | 91  |

| Figure  | 6.5  | Input sum program, which computes $a + b[n]$                                                                                           | 93  |

| Figure  | 6.6  | SDG snippet to illustrate decoupling                                                                                                   | 94  |

| Figure  | 6.7  | Rewritten program sum'                                                                                                                 | 94  |

| Figure  | 6.8  | Residual program $sum_1$                                                                                                               | 97  |

| Figure  | 6.9  | Residual program $sum_2$                                                                                                               | 98  |

| Listing | 6.10 | Instruction Decoupling (Pre-processing step)                                                                                           | 100 |

| Listing | 6.11 | BTA algorithm in WiPEr                                                                                                                 | 101 |

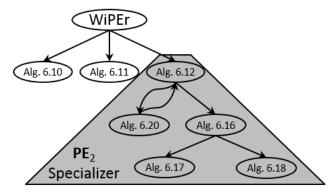

| Listing | 6.12 | WiPEr's specialization loop - IntraPE                                                                                                  | 102 |

| Listing | 6.13 | $specialize_1 \ldots \ldots \ldots \ldots$                                                                                             | 103 |

| Figure  | 6.14 | Call graph depicting the organization of WiPEr                                                                                         | 104 |

| Figure  | 6.15 | Code snippet, and residual program to illustrate specialize $\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | 105 |

| Listing | 6.16 | $specialize_2 \ldots \ldots \ldots \ldots$                                                                                             | 106 |

| Listing | 6.17 | $eval_2  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                              | 106 |

| Listing | 6.18 | reduce <sub>2</sub>                                                                                                                    | 106 |

| Figure  | 6.19 | Code snippet to illustrate issues related to interprocedural BTA                             |

|---------|------|----------------------------------------------------------------------------------------------|

| Listing | 6.20 | specializeFn                                                                                 |

| Figure  | 6.23 | Code snippet to illustrate variable alignment                                                |

| Table   | 6.24 | Characteristics of applications for optimization via specialization                          |

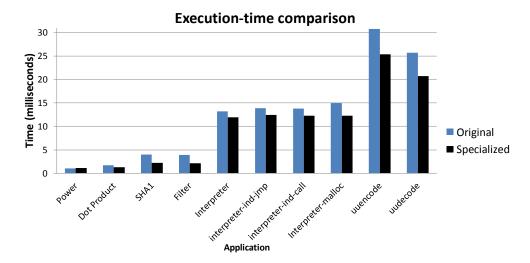

| Figure  | 6.25 | Comparison of the execution times of the original and specialized binaries. $$ . $$ . $$ 115 |

| Table   | 6.26 | Characteristics of applications for component extraction                                     |

| Table   | 6.27 | Comparison of sizes and number of procedures in original binary and extracted                |

|         |      | component                                                                                    |

| Figure  | 7.1  | VSA state before each instruction in a small code snippet, and the USE# and                  |

|         |      | KILL <sup>#</sup> sets for each instruction                                                  |

| Figure  | 7.2  | TSL specification for the instruction add eax, ebx                                           |

| Figure  | 7.3  | BIL code for add eax, ebx [24]. BIL is the UAL used in BAP                                   |

| Figure  | 7.4  | Source code for the diff program, and the backward slice with respect to the                 |

|         |      | return value of main                                                                         |

| Figure  | 7.5  | Assembly listing for diff with the imprecise backward slice computed by                      |

|         |      | CodeSurfer/x86                                                                               |

| Figure  | 7.6  | Source code for the square program, and the forward slice with respect to a 127              |

| Figure  | 7.7  | Assembly listing for square with the imprecise forward slice computed by                     |

|         |      | CodeSurfer/x86                                                                               |

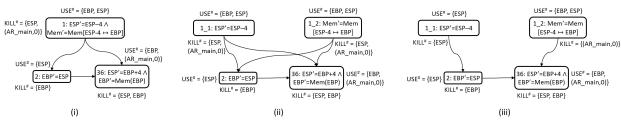

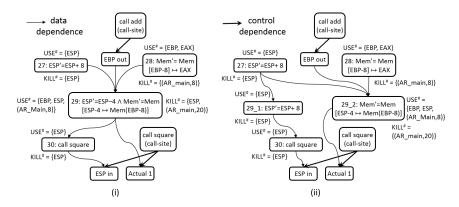

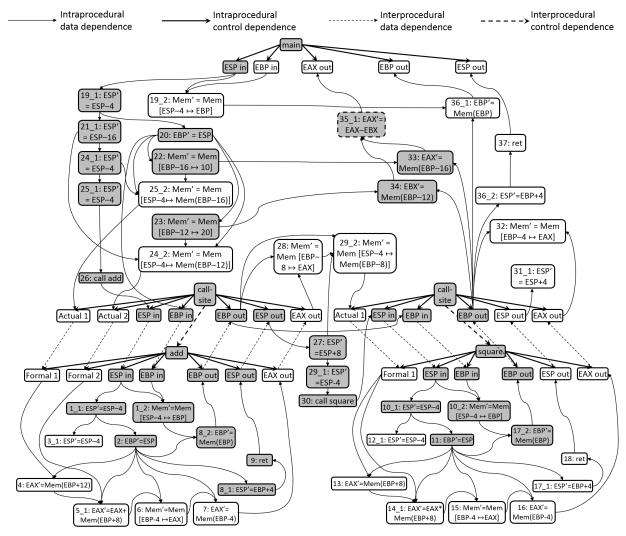

| Figure  |      | SDG snippet illustrating the construction of $\mu$ -SDG                                      |

| Figure  | 7.9  | SDG snippet illustrating the construction of $\mu$ -SDG                                      |

| Figure  | 7.10 | Microcode slice over the $\mu$ -SDG for the diff program. The slicing criterion is           |

|         |      | node 35, which is indicated by the dashed box                                                |

| Figure  | 7.11 | Code generated by McSlice from the microcode backward slice for diff. High-                  |

|         |      | lighted instructions are created by machine-code synthesis                                   |

| Figure  | 7.12 | Microcode slice over the $\mu$ -SDG for the square program. The slicing criterion is         |

|         |      | node 12, which is indicated by the dashed box                                                |

| _       |      | Algorithm SplitNode                                                                          |

| Listing | 7.14 | Algorithm for $\mu$ -SDG construction used in McSlice                                        |

| Figure  | 7.15 | Code snippet, and its corresponding SDG and $\mu\text{-SDG}$ snippets to illustrate          |

|         |      | removal of data-dependence edges via reaching-definitions analysis 136                       |

| _       |      | Example program to illustrate the parameter-mismatch problem in slicing 137                  |

| Figure  | 7.17 | Machine code generated from the microcode slice shown in Fig. 7.10 by a naïve                |

|         |      | method                                                                                       |

| Listing | 7.18 | Algorithm used by McSlice for generating machine code from a mi-           |

|---------|------|----------------------------------------------------------------------------|

|         |      | crocode slice                                                              |

| Table   | 7.19 | Characteristics of applications in our test suite                          |

| Figure  | 7.20 | Comparison of sizes of slices computed by CodeSurfer/x86 and McSlice (log- |

|         |      | scale)                                                                     |

| Figure  | 7.21 | Split of partial and entire instructions in slices computed by McSlice 143 |

| Table   | 7.22 | Comparison of sizes of original binary and extracted component             |

| Figure  | A.1  | Abstract syntax of TinyIA32                                                |

# **Abstract**

The analysis of binaries has gotten an increasing amount of attention from the academic community in the last decade. The results of binary analysis have been predominantly used to answer questions about the properties of binaries. Another potential use of analysis results is to rewrite the binary via semantic transformations. Semantics-based binary-rewriting tools become particularly important when one wishes to modify the functionality of the binary, and the source code and/or compiler toolchain for the binary is unavailable. Semantics-based binary rewriting can be done for the purposes of binary optimization (offline optimization, superoptimization), software reuse (partial evaluation, slicing, binary translation), or software security (binary obfuscation, de-obfuscation).

This dissertation proposes various algorithms for synthesizing a machine-code implementation from a semantic specification of the desired behavior, and describes how one can use a machine-code synthesizer to build different semantics-based binary-rewriting tools.

The first part of this dissertation introduces the problem of machine-code synthesis, proposes a framework for semantics-based binary rewriting via machine-code synthesis, and presents several algorithms for machine-code synthesis. A key challenge in synthesizing machine code is the enormous size of the synthesis search-space. Instruction sets like Intel's IA-32 have around 43,000 unique instruction schemas; this huge instruction pool, along with the exponential cost inherent in enumerative synthesis, results in an enormous search space for the synthesizer: even for relatively small specifications, a naïve synthesizer might take several days to find an implementation. We have developed a suite of techniques—ranging from pruning heuristics to machine learning—that assist an enumerative synthesizer in combating the enormous search space, and speeding up synthesis from the order of days to the order of seconds.

The second part of this dissertation describes how one can instantiate the aforementioned synthesizer-equipped framework to create different semantics-based binary rewriters. In particular, we have instantiated the framework to create two tools that rewrite binaries for purposes of software reuse: a novel machine-code partial evaluator, and an improved machine-code slicer. Among other potential uses, these tools can be used to either modify or extract a component from a binary that lacks source code.

1

# Introduction

The analysis of binaries has gotten an increasing amount of attention from the research community in the last decade (e.g., see references in [88, §7], [14, §1], [23, §1]). This research has led to the development of several tools that analyze binaries, and answer questions about their properties. These tools include static-analysis platforms [15, 23, 88], symbolic-execution engines [39, 72], and verifiers [82, 95]. However, when it comes to binary *rewriting*, the suite of state-of-the-art tools is limited to superoptimizers [16, 76], patching tools [63, 77], and de-obfuscators [27, 81, 99]. Currently, there are no tools that can rewrite binaries via *semantic transformations*, e.g., partial evaluators, slicers, program-repair tools, etc. Semantics-based binary-rewriting tools become particularly important when one wishes to modify the functionality of the binary, and the source code and/or compiler toolchain for the binary is unavailable.

To rewrite a binary based on semantic criteria, an important primitive to have is a machine-code synthesizer—a tool that emits machine-code instructions<sup>1</sup> belonging to a specific instruction-set architecture (ISA) for the transformed program semantics.

**Framework 1.1.** A machine-code synthesizer allows us to create multiple semantics-based binary-rewriting tools that use the following recipe:

- 1. Convert instructions in the binary to a semantic representation, e.g., a quantifier-free bit-vector (QFBV) logic formula.

- 2. Use binary-analysis results to transform QFBV formulas.

- 3. Use the synthesizer to produce an instruction sequence that implements each transformed formula.

One simple tool that could be created using Framework 1.1 is an offline binary-optimizer to improve unoptimized binaries. Analyses like value-set analysis (VSA) [14] and def-use analysis (DUA) [53] could be used in Step 2 to optimize QFBV formulas using information about constants, live registers and flags, etc. One can create different binary-rewriting tools

$<sup>^{1}</sup>$ We use the term "machine code" to refer generically to low-level code, and do not distinguish between actual machine-code bits/bytes and the assembly code to which it is disassembled.

by instantiating Framework 1.1 with different binary analyses and formula-transformation mechanisms.

This dissertation advances the state-of-the-art in binary rewriting by applying programsynthesis techniques to binary analysis and rewriting. In particular, the goals of this dissertation are to

- develop algorithms that synthesize machine-code implementations from specifications, and

- instantiate Framework 1.1 to create binary-rewriting tools that can be used to either modify or extract a reusable component from a binary (for purposes of software reuse).

Each of the aforementioned goals is described in the rest of this section.

# 1.1 Algorithms for Machine-Code Synthesis

Machine-code synthesis is the problem of synthesizing an instruction sequence that implements a semantic specification of the desired behavior, often given as a QFBV formula. Currently, there are no tools that perform machine-code synthesis for a full ISA. Existing approaches either (i) work on small bit-vector languages that do not have all the features of an ISA [41], or (ii) superoptimize instruction sequences [16]. A peephole-superoptimizer has the following type:

$Superoptimize: InstrSequence \rightarrow InstrSequence$

A machine-code synthesizer has the following type:

$Synthesize: QFBVFormula \rightarrow InstrSequence$

Because an instruction sequence can be converted to a QFBV formula via symbolic execution, a machine-code synthesizer can be used for superoptimization; however, the converse is not possible. (See the paragraph titled "Superoptimization" in §3.5.)

A key challenge in synthesizing machine code is the enormous size of the synthesis search-space. Instruction sets like Intel's IA-32 have around 43,000 unique instruction schemas; this huge instruction pool, along with the exponential cost inherent in enumerative synthesis, results in an enormous search space for the synthesizer: even for relatively small specifications, a naïve synthesizer might take several days to find an implementation. The

first part of this dissertation describes how we addressed this challenge while designing an algorithm for machine-code synthesis and making subsequent improvements to the algorithm. The techniques we developed to combat the size of the synthesis search-space are not restricted to machine code in particular, and can be applied to other program synthesizers as well.

**Base algorithm.** We developed an enumerative machine-code synthesizer called McSynth [90], which is parameterized by the ISA of the target instruction-sequence, and is easily adaptable to work on other semantic representations, such as a Universal Assembly Language (UAL) [23]. McSynth uses (i) a *divide-and-conquer* strategy to split the input formula into several independent smaller sub-formulas, (ii) *footprint-based* search-space pruning heuristics to prune away candidates during synthesis, and (iii) a novel instantiation of the *counterexample-guided inductive synthesis* (*CEGIS*) framework as the core synthesis loop. Experiments with the IA-32 instruction set showed that McSynth is 3 to 5 orders of magnitude faster than a baseline enumerative synthesizer.

**Optimizations.** McSynth brought down synthesis time from days to hours, but it was still not fast enough: McSynth times out for several larger QFBV formulas; even for smaller formulas, McSynth takes several minutes to find an implementation. Consequently, if a binary-rewriter client supplies a formula as input to McSynth, the client has to wait several minutes or hours before McSynth finds an implementation. This delay might not be tolerable for a client that has to invoke the synthesizer multiple times to rewrite an entire binary (e.g., a machine-code partial evaluator). We made several improvements to the synthesis algorithm used in McSynth, and developed McSynth++ [92], which is an improved version of McSynth. In addition to a novel *bits-lost-based* pruning heuristic, the improvements incorporate a number of ideas known from the literature, which we adapted in novel ways for the purpose of speeding up machine-code synthesis. Experiments for IA-32 showed that the improvements enable synthesis of code for 12 out of 14 formulas on which McSynth times out, speeding up the synthesis time by at least 1981X, and for the remaining formulas, speeds up synthesis by 3X.

**Model-assisted synthesis.** McSynth and McSynth++ perform a linear search over the space of instruction sequences, i.e., after exhausting all one-instruction sequences, they search through all two-instruction sequences, and so on (modulo pruning). One can see that this search strategy is not very efficient because not all k-instruction sequences are equally likely to implement the input specification. (For example, if the specification computes the

sum of the contents of two registers, then an instruction that performs integer multiplication is clearly not relevant.) We converted the linear search in McSynth++ into a *best-first search* over the space of instruction sequences, and developed McSynth-ML [93], which is a model-assisted version of McSynth++. The cost heuristic for the best-first search comes from two models built from a corpus of equivalent 〈QFBV-formula, instruction-sequence〉 pairs. (Note that it is straightforward to build such a corpus by harvesting several instruction sequences from binaries, and converting them into QFBV formulas via symbolic execution.) One model is a *language model*, which favors useful instruction sequences (i.e., instruction sequences that occur more frequently in the corpus). The other model correlates features of instruction sequences with features of QFBV formulas, and favors instruction sequences that are more likely to implement the input formula. Experiments for IA-32 showed that McSynth-ML enables synthesis of code for 6 out of 50 formulas on which McSynth++ times out, speeding up the synthesis time by at least 549X, and for the remaining formulas, speeds up synthesis by 4.55X.

In summary, the first part of this dissertation introduces the problem of machine-code synthesis, and describes a suite of approaches—ranging from pruning heuristics to machine learning—that assist an enumerative synthesizer to combat the enormous search space, and quickly find a machine-code implementation for a given specification.

# 1.2 Binary Rewriting via Synthesis

Our principal motivation for developing algorithms for machine-code synthesis is to develop a general framework for semantics-based binary rewriting (Framework 1.1), and subsequently instantiate Framework 1.1 to create binary-rewriting tools that can be used to either modify or extract a component from a binary. Existing tools can de-obfuscate [27, 81, 99], superoptimize [16, 76], or harden [6, 33, 83] binaries, but they cannot extract a component from a binary. To this end, we developed two binary-rewriting tools by instantiating Framework 1.1: a novel machine-code partial evaluator, and an improved machine-code slicer. Apart from component extraction, these tools have other potential applications (see below). In the remainder of this sub-section, we describe the tools in greater detail.

**Machine-code partial evaluation** *Partial evaluation* [48] is a program-specialization framework that can be used to specialize a program P with respect to some of its inputs to produce a version of P that is specialized/optimized for those inputs. For example, partially evalu-

ating the power program with the value 2 for the exponent produces an optimized square program. Currently, there are no tools that can partially evaluate machine code.

We developed the first machine-code partial evaluator.<sup>2</sup> The partial evaluator WiPEr [89] performs off-line partial evaluation of binaries. WiPEr's algorithm follows the classical two-phase approach of *binding-time analysis* (*BTA*) followed by *specialization*. WiPEr's specializer specializes an explicit representation of the semantics of an instruction, and emits residual code via machine-code synthesis. Moreover, to create code that allows the stack and heap to be at different positions at run-time than at specialization-time, the specializer represents specialization-time addresses using symbolic constants, and uses a symbolic state for specialization. WiPEr can be used to specialize binaries with respect to commonly used inputs to produce faster binaries (e.g., a file-write routine optimized for a certain file descriptor), as well as to extract an executable component from a bloated binary (e.g., extract compress from the gzip binary).

**Machine-code slicing.** One of the most useful primitives in program analysis is *slicing* [46, 98]. A slice consists of the set of program points that affect (or are affected by) a given program point called the *slicing criterion*. Slicing has many applications, and is used extensively in program analysis and software-engineering tools. A machine-code slicer is often used as a key primitive in several binary analysis and rewriting tools. Improvements in machine-code slicing could significantly increase the precision and/or performance of several existing tools, such as partial evaluators [89], taint trackers [22], and fault localizers [100]. Moreover, a machine-code slicer could be used as a black box to build new binary analysis and rewriting tools.

However, it is not easy to create a machine-code slicer that exhibits a high level of precision. Most instructions in instruction sets such as Intel's IA-32 and ARM are *multi-assignments*: they have several inputs and several outputs (registers, flags, and memory locations). This aspect of the instruction set introduces a *granularity* issue during slicing: there are often instructions at which we would like the slice to include only a subset of the instruction's semantics, whereas the slice is forced to include the entire instruction. Moreover, small amounts of such local imprecision can be amplified via cascade effects. Consequently, the slice computed by state-of-the-art tools is very imprecise, often including essentially the entire program.

We developed a tool called McSlice [91] that slices machine code more accurately. To counter the granularity issue, McSlice performs slicing at the microcode level, instead of the instruction level, and obtains a more precise microcode slice. McSlice uses QFBV formulas

<sup>&</sup>lt;sup>2</sup>Confirmed by personal communication with Neil Jones, Robert Glück, and Saumya Debray.

to represent microcode. To reconstitute a machine-code program from a microcode slice, McSlice uses machine-code synthesis.

The granularity issue in machine-code slicing has been addressed in prior work by Bernat et al. in the context of instrumenting x86 binaries [18]. To address the granularity issue and compute precise slices, Bernat et al. use special-case *instruction splitting*: each node in the *system-dependence graph* (SDG)<sup>3</sup> corresponding to an instruction that performs multiple operations is split into multiple nodes, each of which performs a single operation. In contrast, McSlice splits multi-operation instruction nodes into microcode nodes, and performs slicing on a microcode-level SDG. Each microcode node represents a single microcode update, specified by a QFBV formula. Splitting instruction nodes based on microcode has the following advantages over the approach used by Bernat et al.:

- Special-case instruction splitting is tied to a specific ISA and binary-analysis platform: one needs to specify the target single-operation nodes that should be created for each multi-operation instruction in a new ISA, and this mapping is tailored for a specific binary-analysis platform. However, QFBV-based microcode slicing in McSlice is not tied to a specific binary-analysis platform or ISA. (See §7.2.2.)

- If a client of the slicer wishes to render a backward slice as an executable machine-code program, then one needs to provide the slicer—as an additional input—a mapping from each single-operation node to an equivalent instruction-sequence in the target ISA. Again, this mapping needs to be supplied for each binary-analysis platform and target ISA. In contrast, McSlice obtains instruction sequences from microcode nodes automatically via machine-code synthesis.

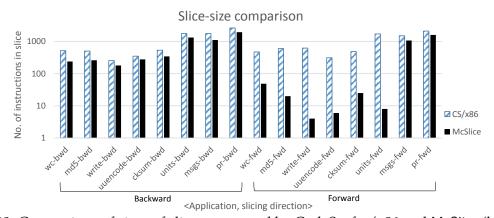

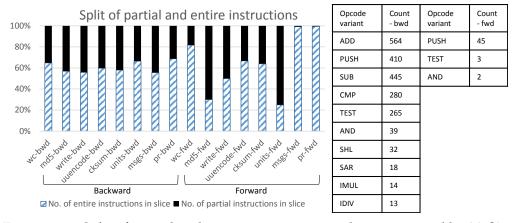

Experiments on IA-32 binaries of FreeBSD utilities show that, in comparison to slices computed by a state-of-the-art tool (CodeSurfer/x86), McSlice reduces the size of backward slices by 33%, and forward slices by 70%. The backwards executable-slicing functionality of McSlice can also be used to extract executable components from binaries (e.g., extract a line-count program from the wc binary).

In summary, the second part of this dissertation describes two instantiations of Framework 1.1—a machine-code partial evaluator and a machine-code slicer—that can be used to extract an executable component from a binary for purposes of software reuse. Note that one can potentially instantiate Framework 1.1 to also create other semantics-based binary-rewriting tools.

<sup>&</sup>lt;sup>3</sup>The system-dependence graph is an intermediate representation used for slicing. See Chapter 7.

#### **Contributions**

The contributions of this dissertation include the following:

- 1. We have created the first machine-code synthesizer that works on the integer subset of a full ISA (Chapter 3).

- 2. We have proposed a general framework for semantics-based binary rewriting. Our framework can be used to create novel binary-rewriting tools, and also to improve existing tools.

- 3. We have proposed several optimizations for speeding up machine-code synthesis. Our optimizations speeds up our baseline synthesis algorithm by several orders of magnitude. Our optimizations are not restricted to machine code in particular, and can be used to speed up other program synthesizers as well (Chapter 4).

- 4. We have created the first low-level-code synthesizer that uses machine learning to assist synthesis (Chapter 5).

- 5. We have created the first machine-code partial evaluator, which can be used to optimize binaries with respect to common inputs, and to extract components from bloated binaries (Chapter 6).

- 6. Our machine-code slicing algorithm significantly improves slicing accuracy with respect to state-of-the-art tools. Our slicer can be used to extract components from binaries, and also to aid other binary analyses, for example, by excluding from consideration portions of the binary that are irrelevant to the analysis (Chapter 7).

The dissertation also makes the following more general contributions that go beyond the realms of binary analysis and rewriting:

- 1. We have proposed a divide-and-conquer approach to enumerative program synthesis that facilitates breaking a larger synthesis task into a sequence of independent smaller sub-tasks.

- 2. We have proposed lightweight pruning strategies that use abstractions/overapproximations of enumerated candidates to rapidly prune away useless candidates during synthesis.

- 3. Our model-assisted synthesis algorithm is the first program-synthesis technique to use models learned from *both* specifications *and* implementations to assist the synthesis search.

- 4. We have shown, via program synthesis, how one can reconstitute a program that is at a higher level from an intermediate representation (IR) that is at a lower level. (We have demonstrated this synthesis-based approach to program reconstitution in the context of partial evaluation and slicing.) This approach to program reconstitution becomes particularly useful when translation from low-level IR fragments to high-level code constructs is not straightforward, and the search space of high-level code constructs is enormous.

- 5. We have proposed a symbolic approach to program specialization. This approach to specialization becomes particularly useful when the specializer wants to treat certain inputs as static inputs, but somehow suppress their residuation.

The remaining chapters expand on these contributions. Chapter 2 presents background material required for the remainder of the thesis. Chapter 8 presents conclusions and opportunities for future work.

2

# Background

This chapter presents a primer on Intel's IA-32 ISA (§2.1), and a logic in which specifications and semantics of instruction sequences are expressed (§2.2).

#### **2.1 IA-32 Primer**

IA-32 is the 32-bit subset of Intel's x86 ISA. This section briefly describes the syntax and concrete operational semantics of IA-32 instructions.

### **2.1.1** Syntax

IA-32 has some general-purpose registers (EAX, EBX, etc.), and some special-purpose registers: ESP is the stack pointer, EBP is the frame pointer, and EIP is the program counter. Some common IA-32 instructions are given in Fig. 2.1. The push instruction pushes an

```

1: push ebp 3: sub esp, 16 5: lea eax, [esp+4] 7: jmp 1000

2: mov ebp, esp 4: mov [esp], 1 6: cmp eax, ebx 8: jz 1000

```

Figure 2.1: Some common IA-32 instructions.

operand on top of the stack; the IA-32 stack grows upwards. In many instructions with more than one operand, the operand on the left is the destination. For example, instruction 2 in Fig. 2.1 copies a 32-bit value from ESP to EBP, and instruction 3 decrements ESP by 16 (and sets flags suitably). An exception is the cmp instruction, in which both operands are source operands; for example, instruction 6 in Fig. 2.1 compares the values in registers EAX and EBX. Square brackets denote memory operands; for example, instruction 4 in Fig. 2.1 writes the value 1 in the memory location pointed to by ESP. An exception is the lea instruction, in which square brackets denote "the effective address of." For example, instruction 5 in Fig. 2.1 loads the effective address of ESP + 4 in the EAX register. The effective address is computed as base + index \*scale + offset, where base and index are registers, and scale and offset are integers. The jmp instruction (instruction 7 in Fig. 2.1) jumps to the operand target-address unconditionally, while the jz instruction (instruction 8 in Fig. 2.1) jumps to the operand target-address only if the zero flag (ZF) is set.

```

\begin{tabular}{l} $\Im[\mbox{push ebp}]$ $\sigma \equiv let $\sigma' = update_{reg}(\sigma, [\mbox{esp}]], access_{reg}(\sigma, [\mbox{esp}]]) - 4)$ \\ $in update_{mem}(\sigma', access_{reg}(\sigma', [\mbox{esp}]]), access_{reg}(\sigma, [\mbox{ebp}]])$ \\ $\Im[\mbox{mov ebp, esp}]$ $\sigma \equiv update_{reg}(\sigma, [\mbox{ebp}]], access_{reg}(\sigma, [\mbox{esp}]])$ \\ $\Im[\mbox{sub esp, 16}]$ $\sigma \equiv let $\sigma' = update_{reg}(\sigma, [\mbox{esp}]], access_{reg}(\sigma, [\mbox{esp}]]) - 16)$ \\ $in update_{flag}(\sigma', [\mbox{ZF}]], access_{reg}(\sigma', [\mbox{esp}]]) - 16)$ \\ $\Im[\mbox{mov [esp], 1}]$ $\sigma \equiv update_{mem}(\sigma, access_{reg}(\sigma, [\mbox{esp}]]), 1)$ \\ $\Im[\mbox{lea eax, [esp+4]}]$ $\sigma \equiv update_{reg}(\sigma, [\mbox{eax}]], access_{reg}(\sigma, [\mbox{esp}]]) + 4)$ \\ $\Im[\mbox{cmp eax, ebx}]$ $\sigma \equiv update_{flag}(\sigma, [\mbox{ZF}]], (access_{reg}(\sigma, [\mbox{eax}]]) - access_{reg}(\sigma, [\mbox{ebx}]]) = 0)$ \\ $\Im[\mbox{jmp 1000}]$ $\sigma \equiv update_{reg}(\sigma, [\mbox{eip}]], access_{flag}(\sigma, ZF)?1000: access_{reg}(\sigma, [\mbox{eip}]]) + 4)$ \\ $\text{Figure 2.2: Valuation functions for instructions in Fig. 2.1.} \end{tabular}

```

#### 2.1.2 Semantics

The primitive domains of the IA-32 semantics include 32-bit integers, Booleans, registers, and flags. The primitive domains and their operators are given below. Note that the domains and their elements are in boldface to distinguish them from their syntactic counterparts in the logic that will be defined in §2.2.

$$i \in INT = \mathbb{Z}_{32}$$

$b \in BOOL = \{True, False\}$

$r \in Register = \{EAX, ESP, ...\}$   $f \in Flag = \{CF, SF, ...\}$

$op \in ArithOp = \{+, -, ...\}$   $bop \in BoolOp = \{\land, \lor, ...\}$

$rop \in RelOp = \{=, \neq, <, ...\}$   $cop \in CondOp = \{?:\}$

Store is a compound domain that denotes an IA-32 state. (In all chapters except Chapter 6, the term "state" will be used to refer to an IA-32 Store.) Store is a triple consisting of three maps: a register map, a flag map, and a memory map. Store has operators to access and update the maps. The Store domain is defined below.

$$\sigma \in \mathit{Store} = \mathit{RegMap} \times \mathit{FlagMap} \times \mathit{MemMap}$$

$$\mathit{RegMap} : \mathit{Register} \rightarrow \mathit{INT} \quad \mathit{FlagMap} : \mathit{Flag} \rightarrow \mathit{BOOL} \quad \mathit{MemMap} : \mathit{INT} \rightarrow \mathit{INT}$$

The valuation function  $\mathfrak{I}[\cdot]$  has the type  $\mathfrak{I}$ : Instruction  $\to$  *Store*  $\to$  *Store*, where Instruction is the type for a syntactic instruction.  $\mathfrak{I}$  takes an instruction  $\mathfrak{i}$  and a pre-state, and returns a post-state that reflects the updates made by the execution of  $\mathfrak{i}$ . The valuation functions for the instructions in Fig. 2.1 are given in Fig. 2.2. In the valuation functions, the overloaded function  $[\![\cdot]\!]$  returns primitive semantic objects for their syntactic counterparts.

```

T \in Term, \ \varphi \in Formula, \ FE \in FuncExpr

c \in Int32 = \{..., -1, 0, 1, ...\} \quad b \in Bool = \{True, False\}

I_{Int32} \in Int32Id = \{EAX, ESP, EBP, ..., m, n, ...\}

I_{Bool} \in BoolId = \{CF, SF, ..., x, y, ...\} \quad F \in FuncId = \{Mem\}

op \in BinOp = \{+, -, ...\} \quad bop \in BoolOp = \{\land, \lor, ...\} \quad rop \in RelOp = \{=, \neq, <, >, ...\}

T ::= c \mid I_{Int32} \mid T_1 \ op \ T_2 \mid ite(\varphi, T_1, T_2) \mid F(T_1)

\varphi ::= b \mid I_{Bool} \mid T_1 \ rop \ T_2 \mid \neg \varphi_1 \mid \varphi_1 \ bop \ \varphi_2 \mid F = FE

FE ::= F \mid FE_1[T_1 \mapsto T_2]

Figure 2.3: Syntax of L[IA-32].

```

Instructions 1 through 6 in Fig. 2.1 also increment the program counter EIP by the length of the instruction. For brevity, we do not show this increment explicitly in Fig. 2.2. We also do not show all the flags updates done by the cmp and sub instructions.

# 2.2 Quantifier-Free Bit-Vector (QFBV) Logic Formulas

Input specifications to a machine-code synthesizer can be expressed formally by QFBV formulas. In this section, we describe the syntax and semantics of such formulas.

## **2.2.1** Syntax

Consider a quantifier-free bit-vector logic L over finite vocabularies of constant symbols and function symbols. We will be dealing with a specific instantiation of L, denoted by L[IA-32]. (L can also be instantiated for other ISAs.) In L[IA-32], some constants represent IA-32's registers (EAX, ESP, EBP, etc.), some represent flags (CF, SF, etc.), and some are free constants (m, n, x, y, etc.). L[IA-32] has only one function symbol "Mem," which denotes memory. The syntax of L[IA-32] is defined in Fig. 2.3. A term of the form  $ite(\varphi, T_1, T_2)$  represents an if-then-else expression. A FuncExpr of the form  $FE[T_1 \mapsto T_2]$  denotes a function-update expression.

To write formulas that express state transitions, all *Int32Ids*, *BoolIds*, and *FuncIds* can be qualified by primes (e.g., *Mem'*). The QFBV formula for a specification is a restricted 2-vocabulary formula that specifies a state transformation. It has the form

$$\bigwedge_{m}(I'_{m}=T_{m}) \wedge \bigwedge_{n}(J'_{n}=\varphi_{n}) \wedge Mem' = FE, \tag{2.1}$$

where  $I'_m$  and  $J'_n$  range over the constant symbols for registers and flags, respectively. The primed vocabulary is the post-state vocabulary, and the unprimed vocabulary is the prestate vocabulary. For example, the QFBV formula for the specification "push the 32-bit value in the frame-pointer register EBP onto the stack" is given below.

$$ESP' = ESP - 4 \land Mem' = Mem[ESP - 4 \mapsto EBP]$$

(2.2)

In this section, and in the rest of the dissertation, we will show only the portions of QFBV formulas that express how the state is *modified*. QFBV formulas actually contain identity conjuncts of the form I' = I, J' = J, and Mem' = Mem for constants and functions that are *unmodified*. Because we do not want the synthesizer output to be restricted to an instruction sequence that is located at a specific address, specifications do not contain conjuncts of the form EIP' = T. (Recall that EIP is the program counter for IA-32.)

**Expressing semantics of instruction sequences.** In addition to input specifications, one can use L[IA-32] formulas to express the semantics of instruction sequences. The function  $\langle\langle \cdot \rangle\rangle$  encodes a given IA-32 instruction sequence as a QFBV formula. The QFBV formulas for the instructions in Fig. 2.1 are given below. Note that the formulas given below are merely QFBV transcriptions of the valuation functions given in Fig. 2.2.

```

\langle\!\langle \text{push ebp} \rangle\!\rangle \equiv ESP' = ESP - 4 \land Mem' = Mem[ESP - 4 \mapsto EBP]   \langle\!\langle \text{mov ebp, esp} \rangle\!\rangle \equiv EBP' = ESP   \langle\!\langle \text{sub esp, 16} \rangle\!\rangle \equiv ESP' = ESP - 16 \land ZF' = (ESP - 16 = 0)   \langle\!\langle \text{mov [esp], 1} \rangle\!\rangle \equiv Mem' = Mem[ESP \mapsto 1]   \langle\!\langle \text{lea eax, [esp+4]} \rangle\!\rangle \equiv EAX' = ESP + 4   \langle\!\langle \text{cmp eax, ebx} \rangle\!\rangle \equiv ZF' = (EAX - EBX = 0)   \langle\!\langle \text{jmp 1000} \rangle\!\rangle \equiv EIP' = 1000   \langle\!\langle \text{jz 1000} \rangle\!\rangle \equiv EIP' = ite(ZF, 1000, EIP + 4)

```

While others have created such encodings by hand (e.g., [74]), the tools described in this dissertation use a method that takes a specification of the concrete operational semantics of IA-32 instructions and creates a QFBV encoder automatically. The method reinterprets each semantic operator as a QFBV formula-constructor or term-constructor (see [54]).

Certain IA-32 string instructions contain an implicit "microcode loop", e.g., instructions with the rep prefix, which perform an *a priori* unbounded amount of work determined by the value in the ECX register at the start of the instruction. In other applications that use

the infrastructure on which our tools are built, this implicit microcode loop is converted into an explicit loop whose body is an instruction that performs the actions performed by the body of the microcode loop. (More details about this conversion is available elsewhere [54, §6].) However, the semantics of such instructions cannot be expressed as a single QFBV formula. Because of this expressibility limitation, the synthesis algorithms described in this dissertation do not try to synthesize instructions that use the rep prefix.

#### 2.2.2 Semantics

QFBV formulas in L[IA-32] are interpreted as follows: elements of Int32, Bool, BinOp, RelOp, and BoolOp are interpreted in the standard way. An unprimed (primed) constant symbol is interpreted as the value of the corresponding register or flag from the pre-state (post-state). An unprimed (primed) Mem symbol is interpreted as the memory array from the pre-state (post-state). (To simplify the presentation, we pretend that each memory location holds a 32-bit integer; however in our tools, memory is addressed at the level of individual bytes.) The meaning of a QFBV formula in L[IA-32] is a set of machine-state pairs ( $\langle pre\text{-state}, post\text{-state} \rangle$ ) that satisfy the formula. Recall that an IA-32 machine-state is a triple of the form:

where RegMap, FlagMap, and MemMap map each register, flag, and memory location in the state, respectively, to a value. A  $\langle pre\text{-state} \rangle$  pair that satisfies Eqn. (2.2) is

$$\begin{split} \sigma &\equiv \langle [ESP \mapsto 100] [EBP \mapsto 200], \, [\,], \, [\,] \rangle \\ \sigma' &\equiv \langle [ESP \mapsto 96] [EBP \mapsto 200], \, [\,], \, [96 \mapsto 200] \rangle. \end{split}$$

By convention, all locations for which the range value is not shown explicitly in a state have the value 0.

# Part I

# Algorithms

# 3 Synthesis of Machine Code from Semantics

This chapter presents (i) a technique to synthesize a straight-line machine-code instruction sequence from a semantic specification of the desired behavior, given as a QFBV formula, and (ii) a tool called McSynth that implements the aforementioned technique. The synthesized instruction-sequence implements the input QFBV formula (i.e., is equivalent to the QFBV formula). McSynth is parameterized by the ISA of the target instruction-sequence, and is easily adaptable to work on other semantic representations, such as a Universal Assembly Language (UAL) [23].

The synthesis algorithm used in McSynth is the baseline machine-code-synthesis algorithm presented in this dissertation. Successive chapters explore improvements to this baseline algorithm.

#### **Contributions**

The contributions of this chapter include the following:

- Our machine-code-synthesis technique is the first of its kind to be applied to the integer subset of a full ISA.

- The core synthesis loop of our technique is a new instantiation of the *counterexample-guided inductive synthesis* (CEGIS) framework (§3.2.1).

- We have developed *footprint-based* pruning heuristics to prune away useless candidates, and reduce the synthesis search-space (§3.2.2).

- To counter the exponential cost of enumerative strategies, we have developed a *divide-and-conquer* strategy to divide a QFBV formula into independent sub-formulas, and synthesize instructions for the sub-formulas (§3.2.3). This strategy has been shown to reduce the synthesis time by several orders of magnitude.

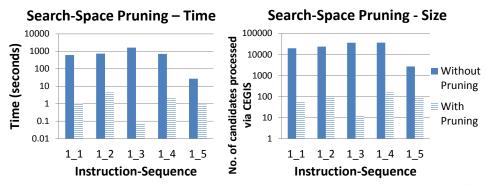

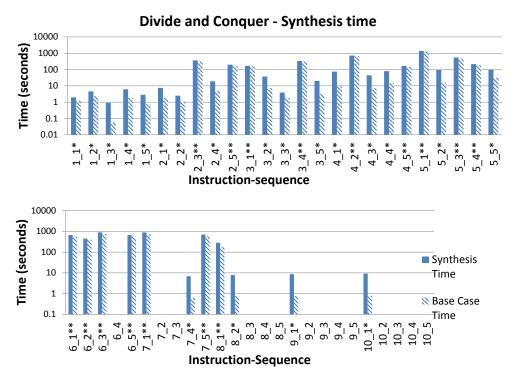

Our methods have been implemented in McSynth, a machine-code synthesizer for Intel's IA-32 ISA. We tested McSynth on QFBV formulas obtained from basic blocks in the SPECINT 2006 benchmark suite. We found that, on an average, McSynth's footprint-based search-space-pruning heuristic reduces the synthesis time by a factor of 473, and McSynth's divide-and-conquer strategy reduces synthesis time by a further 3 to 5 orders of magnitude (§3.4).

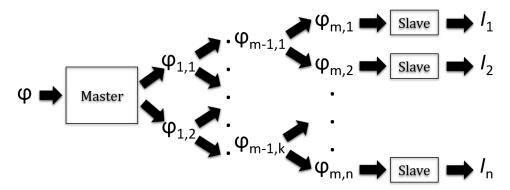

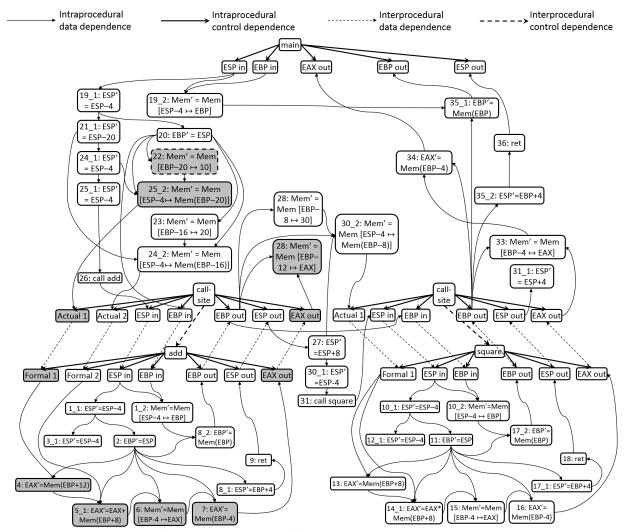

Figure 3.1: Master-slave architecture of McSynth.

In comparison to the x86 peephole superoptimizer [16] (the only tool whose search space is comparable to that of McSynth), which takes several hours to synthesize an instruction sequence of length up to 3, McSynth can synthesize certain instruction sequences of length up to 10 in a few minutes. We have also built an IA-32 partial evaluator (Chapter 6), and an IA-32 slicer (Chapter 7) as clients of McSynth.

### 3.1 Overview

McSynth uses enumerative strategies for synthesis. However, an ISA like IA-32 has around 43,000 unique instruction schemas, which, when combined with the exponential cost inherent in enumeration, results in an enormous search space for synthesis. McSynth attempts to cope with the enormous search space using a *master-slave* architecture. The design of McSynth is depicted in Fig. 3.1. Given a QFBV formula  $\varphi$ , McSynth synthesizes an instruction sequence for  $\varphi$  in the following way:

- 1. The master uses a divide-and-conquer strategy to split  $\varphi$  into independent subformulas, and hands over each sub-formula to a slave synthesizer.

- 2. The slave uses enumeration, along with an instantiation of the CEGIS framework and footprint-based search-space pruning heuristics to synthesize code for a sub-formula.

- 3. If a slave times out, the master uses an alternative split. (For example in Fig. 3.1, if synthesis of code for  $\phi_{m,1}$  times out, the master tries out an alternative split for  $\phi_{m-1,1}$ .) If all candidate splits for a sub-formula time out, the master hands over the entire sub-formula to a slave. (For example in Fig. 3.1, if all candidate splits of  $\phi_{m-1,1}$  time out, the master supplies  $\phi_{m-1,1}$  as an input to a slave.)

4. The master concatenates the results produced by the slaves, and returns the final instruction sequence.

In the remainder of this section, we present an example to illustrate McSynth's algorithm. In procedure calls, a common idiom in the prologue of the callee is to save the frame pointer of the caller, and initialize its own frame pointer. A QFBV formula  $\phi$  for this idiom is

$$\varphi \equiv ESP' = ESP - 4 \land EBP' = ESP - 4 \land Mem' = Mem[ESP - 4 \mapsto EBP]. \tag{3.1}$$

A naïve enumerative synthesizer will take a few days to find an implementation for  $\varphi$ . Using  $\varphi$  as a running example, we will first illustrate how McSynth's master works. We will then illustrate how the slave works.

#### Master

The divide-and-conquer strategy tries to split the updates in  $\varphi$  across a sequence of subformulas  $\langle \varphi_1, \varphi_2, ..., \varphi_k \rangle$  such that if one were to synthesize an instruction sequence  $I_i$  for each  $\varphi_i$  *independently*, and concatenate the synthesized instruction-sequences in the same order, the result will be equivalent to  $\varphi$ . Such a split is called a *legal* split. A sufficient condition for a legal split is *flow independence*—if we can split the updates in  $\varphi$  across the sequence  $\langle \varphi_1, \varphi_2, ..., \varphi_k \rangle$  such that there is no flow dependence from  $\varphi_i$  to any successor sub-formula  $\varphi_j$  (i < j), the split is legal. The reason for this sufficiency is as follows: because  $I_j$  is equivalent to some sub-formula  $\varphi_j$  of  $\varphi$ , and  $I_j$  does not read any of the locations that could be modified by any predecessor instruction-sequence  $I_i$  (i < j),  $I_1; I_2; ...; I_k$  performs the same state transformations as  $\varphi$ .

McSynth uses the following one-sided decision procedure to check if a split  $\langle \phi_1, \phi_2, ..., \phi_k \rangle$  is flow-independent. The decision procedure returns MAYBE if either (or both) of the following conditions hold:

C1:  $\phi_j$  might use a register or flag, and a predecessor sub-formula  $\phi_i$  (i < j) might modify the same register or flag

C2:  $\varphi_j$  might use *some* memory location, and a predecessor sub-formula  $\varphi_i$  (i < j) might modify *some* memory location

If neither of the conditions hold, the decision procedure returns NO (meaning the split is flow-independent). One can see that the one-sided decision procedure is very conservative

in the way it handles flow dependences through memory. This limitation is addressed in Chapter 4.

One possible way to split  $\varphi$  is as  $\langle \varphi_1, \varphi_2, \varphi_3 \rangle$ , where

$$\varphi_1 \equiv ESP' = ESP - 4$$

$\varphi_2 \equiv EBP' = ESP - 4$   $\varphi_3 \equiv Mem' = Mem[ESP - 4 \mapsto EBP].$

However, McSynth's decision procedure returns MAYBE for the split because  $\varphi_2$  and  $\varphi_3$  both use *ESP*, which is killed by  $\varphi_1$ . Consequently McSynth discards this split.

Another possible way to split  $\varphi$  is as  $\langle \varphi_1, \varphi_2, \varphi_3 \rangle$ , where

$$\varphi_1 \equiv Mem' = Mem[ESP - 4 \mapsto EBP]$$

$\varphi_2 \equiv EBP' = ESP - 4$   $\varphi_3 \equiv ESP' = ESP - 4$ .

This split does not introduce any extraneous flow dependences, and consequently, McSynth's decision procedure returns NO for this split (meaning that the split is flow-independent). McSynth's master supplies the sub-formulas  $\varphi_1$ ,  $\varphi_2$ , and  $\varphi_3$ , respectively, to slave synthesizers.

#### Slave

Given a sub-formula  $\phi_i$  and—for pragmatic reasons—a timeout value, McSynth's slave synthesizer either synthesizes an instruction sequence that implements  $\phi_i$ , or returns FAIL if it could not find such an instruction sequence before the timeout expires. The slave synthesizes an instruction sequence for  $\phi_i$  using the following method:

- 1. The slave enumerates *templatized* instruction-sequences of increasing length. A templatized instruction-sequence is a sequence of instructions with template operands (or holes) instead of one or more constant values.

- 2. The slave attempts to find an instantiation of a candidate templatized instruction-sequence that is logically equivalent to  $\varphi_i$  using CEGIS. If an instantiation is found, the slave returns it. Otherwise, the next templatized sequence is considered.

- 3. The slave uses heuristics based on the *footprints* of QFBV formulas (see below) to prune away useless candidates during enumeration.

In the remainder of this section, we illustrate the working of a slave synthesizer using  $\phi_2$  as an example.

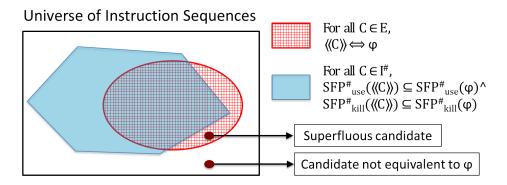

The slave starts enumerating templatized one-instruction sequences. To prune away candidates during enumeration, McSynth uses an overapproximation of locations that

could potentially be touched by a formula. We define the *abstract semantic use-footprint* SFP $^{\#}_{USE}$  (*kill-footprint* SFP $^{\#}_{KILL}$ ) as an overapproximation of the locations used (modified) by a formula. Concretely, an abstract semantic-footprint of a formula  $\phi$  is a subset of the set of constant symbols in  $\phi$  (except symbolic constants) and a special symbol "*Mem*," which denotes the entire memory. The symbols in SFP $^{\#}_{KILL}$  are primed.

Let us assume that the first candidate enumerated by the slave is  $C_1 \equiv \text{``mov eax}$ ,  $\langle \text{Imm32} \rangle$ ." The formula  $\psi_1$  for  $C_1$  is EAX' = m. The abstract semantic footprints for  $\phi_2$  and  $\psi_1$ , respectively, are given below.

$$\begin{aligned} & SFP^{\#}_{USE}(\phi_1) = \{ESP\} \quad SFP^{\#}_{KILL}(\phi_1) = \{EBP'\} \\ & SFP^{\#}_{USE}(\psi_1) = \{\} \quad SFP^{\#}_{KILL}(\psi_1) = \{EAX'\} \end{aligned}$$

One can see that the abstract semantic KILL-footprint of  $\psi_1$  is outside that of  $\phi_2$ , and thus  $C_1$  can never implement  $\phi_2$  without possibly modifying a value in a location that is otherwise unmodified by  $\phi_2$ . Therefore, the slave prunes away  $C_1$  because it is a *useless candidate*. Moreover, regardless of the instruction sequence that is appended to  $C_1$ , the resulting instruction sequence would always be discarded at this step. We call instruction sequences such as  $C_1$  *useless prefixes*. By discarding useless prefixes, any future candidate enumerated by the slave has only *useful prefixes* as its prefix.

Suppose that the next candidate is  $C_2 \equiv \text{``mov ebp'}$ , [esp]." The formula  $\psi_2$  for  $C_2$  is EBP' = Mem(ESP). The abstract semantic footprints for  $\psi_2$  are given below.

$$SFP^{\#}_{USE}(\psi_1) = \{ESP, Mem\} \quad SFP^{\#}_{KILL}(\psi_1) = \{EBP'\}$$

The abstract semantic USE-footprint of  $\psi_2$  is outside that of  $\varphi_2$  because  $\psi_2$  might use some memory location, but  $\varphi_2$  does not use any memory location. Therefore, the slave also prunes away the useless candidate  $C_2$ .

Suppose that the next candidate is  $C_3 \equiv \text{``mov ebp'}$ ,  $\langle \text{Imm32} \rangle$ ." The formula  $\psi_3$  for  $C_3$  is EBP' = m. The abstract semantic USE/KILL-footprints of  $\psi_3$  are within those of  $\phi_2$ . So the slave uses a CEGIS-based loop to check if there exists an instantiation of the candidate that implements  $\phi_2$ . The CEGIS loop says that no such instantiation exists, and so the slave discards  $C_3$ .

The slave eventually enumerates the candidate  $C_4 \equiv$  "lea ebp, [esp- $\langle \text{Imm32} \rangle$ ] The CEGIS loop returns the instantiation "lea ebp, [esp-4]" of  $C_4$  as the synthesized code for  $\phi_2$ .

In a similar manner, the slave synthesizes the instruction sequences "mov [esp-4], ebp" and "lea esp, [esp-4]" for  $\phi_1$  and  $\phi_2$ , respectively. McSynth concatenates the results pro-

duced by the slaves and returns "mov [esp-4], ebp; lea ebp, [esp-4]; lea esp, [esp-4]" as the implementation. McSynth completes the overall synthesis task in a few seconds; that is a *four-orders-of-magnitude speedup* compared to a naïve enumerative synthesizer.

### 3.1.1 The Role of Templatized Instruction-Sequences