# APPROACHES TO INTERPROCEDURAL REGISTER ALLOCATION

Steven M. Kurlander

Technical Report #1294

January 1996

# APPROACHES TO INTERPROCEDURAL REGISTER ALLOCATION

Ву

Steven M. Kurlander

A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

Doctor of Philosophy (Computer Sciences)

at the

UNIVERSITY OF WISCONSIN - MADISON

1996

### Abstract

The goal of interprocedural register allocation is to minimize execution time by selecting the registers to assign to each procedure and the registers to spill across calls. To generate an allocation, an interprocedural register allocator may consider the frequency of procedure calls and the register needs of each procedure.

Past interprocedural register allocators have applied heuristics to generate an interprocedural register allocation. This thesis presents models of interprocedural register allocation and algorithms to find a minimum cost allocation. We model both the benefit of allocating registers to procedures and the cost of register loads and stores across calls.

This thesis presents two approaches for finding an interprocedural register allocation of locals. The first approach models the benefit of allocating registers to procedures. To find an allocation, the interprocedural register allocator recursively simplifies a call graph. We add a heuristic that spills registers across calls to assign additional registers to procedures.

Our next approach solves a network flow problem to find an interprocedural register allocation of locals. With this approach we model both the benefit of allocating registers to procedures and the cost of spilling registers across calls. This interprocedural register allocator finds minimum cost allocations in polynomial time. Also, this allocator is fast in practice and can generate significant improvements in execution-time.

We extend our network flow approach to interprocedural register allocation to allocate registers to globals. Two models are presented for interprocedural register allocation of globals. The first model assumes globals are allocated registers across all procedures in the call graph, and the second divides the call graph into regions, in which globals can be spilled from registers within each region.

# Acknowledgements

I am grateful to my advisor Charles Fischer. Through his more than four years of tutelage, I have learned the skills necessary for research.

Harish Patil's perpetual optimism has been very much appreciated through the ups and downs of graduate school. His insightful remarks improved my work. I enjoyed lively discussions with T. N. Vijaykumar. My thesis benefited from his extensive knowledge of Computer Architecture.

When beginning my research, Lorenz Huelsbergen and Todd Proebsting displayed the effort needed to be a successful graduate student.

I would like to thank Robert Meyer and Armand Zakarian for answering my questions on network flow optimization problems. Armand Zakarian wrote the network flow problem solver used in this thesis.

Questions and comments by Satish Chandra, Susan Horwitz, Jim Larus, and Thomas Reps improved the content of my work.

# Contents

| A            | bstra        | ct                                                |                                                                       | ii  |  |

|--------------|--------------|---------------------------------------------------|-----------------------------------------------------------------------|-----|--|

| $\mathbf{A}$ | ckno         | wledge                                            | ements                                                                | iii |  |

| 1            | Introduction |                                                   |                                                                       |     |  |

|              | 1.1          | Contr                                             | ibutions                                                              | 2   |  |

|              |              | 1.1.1                                             | A DAG-Based Approach to Interprocedural Register Allocation           | 2   |  |

|              |              | 1.1.2                                             | A Network Flow Approach to Interprocedural Register Allocation .      | 2   |  |

|              | 1.2          | A Cor                                             | mparison of Intraprocedural and Interprocedural Register Allocation . | 3   |  |

|              | 1.3          | Conte                                             | xt for Interprocedural Register Allocation                            | 6   |  |

|              | 1.4          | Thesis                                            | S Overview                                                            | 7   |  |

| 2            | Rel          | ated V                                            | Vork                                                                  | 8   |  |

|              | 2.1          | Archit                                            | sectural Support to Avoid Saving and Restoring Registers Across Calls | 8   |  |

|              | 2.2          | 2 Software Support for Interprocedural Allocation |                                                                       |     |  |

|              |              | 2.2.1                                             | Wall's Approach                                                       | 10  |  |

|              |              | 2.2.2                                             | Steenkiste and Hennessy's Approach                                    | 11  |  |

|              |              | 2.2.3                                             | Chow's Approach                                                       | 12  |  |

|              |              | 2.2.4                                             | Santhanam and Odnert's Approach                                       | 13  |  |

|              |              | 2.2.5                                             | Conclusions                                                           | 14  |  |

| 3            | АΙ           | AG-B                                              | Based Approach                                                        | 16  |  |

|              | 3 1          | Mode                                              | ling Interprocedural Register Allocation                              | 16  |  |

|   | 3.2 | Minimum Cost Allocation for Call Trees                    | 17       |

|---|-----|-----------------------------------------------------------|----------|

|   |     | 3.2.1 Measuring Cost                                      | 17       |

|   |     | 3.2.2 Generating an allocation                            | 18       |

|   |     | 3.2.3 Complexity                                          | 19       |

|   |     | 3.2.4 Example                                             | 9        |

|   | 3.3 | Minimum Cost Interprocedural Register Allocation for DAGs | 21       |

|   | 3.4 | Shortening the Search Space                               | 22       |

|   |     | 3.4.1 Finding the Maximum Bound                           | 23       |

|   |     | 3.4.2 Finding the Minimum Bound                           | 25       |

|   | 3.5 | Level-n Shared Nodes                                      | 26       |

|   | 3.6 | Complexity                                                | 28       |

|   | 3.7 | Register Spilling                                         | 28       |

|   | 3.8 | Implementation                                            | 28       |

|   | 3.9 | Conclusions                                               | 31       |

| 4 | ΔΝ  | Network Flow Approach 3                                   | 32       |

| - | 4.1 |                                                           | 33       |

|   | 4.1 | 1 3                                                       | 34       |

|   |     |                                                           | 35       |

|   |     | *                                                         | 36       |

|   |     |                                                           | 37       |

|   |     |                                                           | 10       |

|   | 1.0 | •                                                         |          |

|   | 4.2 |                                                           | 11       |

|   |     |                                                           | 15<br>10 |

|   |     |                                                           | 18       |

|   | 4.3 | Complexity                                                | 19       |

|   |     |                                                           | -0       |

|   | 4.4 | Liveness                                                  | 50       |

|   | 4.5 | Liveness       5         Library Routines       5         | 50       |

|   |     | Liveness                                                  |          |

|   | 4.8                  | Conclu  | usions                                                           | 61  |

|---|----------------------|---------|------------------------------------------------------------------|-----|

| 5 | $\operatorname{Pro}$ | of of C | Correctness                                                      | 62  |

|   | 5.1                  | Mappi   | ing Solutions between $P(k,G)$ and $Q(k,G)$                      | 65  |

|   | 5.2                  | Maxin   | nal Solutions in $P(k,G)$ and $Q(k,G)$                           | 69  |

|   | 5.3                  | Mappi   | ing solutions between $P^*(k,G)$ and $Q^*(k,G)$                  | 77  |

| 6 | Maj                  | pping   | to Minimum Cost Flow Problem                                     | 79  |

| 7 | Allo                 | ocating | g Registers to Globals                                           | 84  |

|   | 7.1                  | NP-Co   | omplete                                                          | 85  |

|   | 7.2                  | Wall's  | Model of Interprocedural Allocation of Globals                   | 87  |

|   |                      | 7.2.1   | Incorporating Wall's Approach                                    | 88  |

|   |                      | 7.2.2   | Implementation                                                   | 92  |

|   | 7.3                  | A Moi   | re Precise Model                                                 | 95  |

|   |                      | 7.3.1   | Webs                                                             | 95  |

|   |                      | 7.3.2   | Refining Webs                                                    | 96  |

|   |                      | 7.3.3   | Generating an Allocation with Global Candidates                  | 97  |

|   |                      | 7.3.4   | Choosing a Set of Disjoint Webs for each Iteration               | 99  |

|   |                      | 7.3.5   | Modeling Interprocedural Register Allocation of Globals          | 100 |

|   |                      | 7.3.6   | Dual Minimum Cost Flow Problem for Interprocedural Register Al-  |     |

|   |                      |         | location of Globals                                              | 108 |

|   |                      | 7.3.7   | Mapping between the dual minimum cost flow problem and interpro- |     |

|   |                      |         | cedural register allocation of globals                           | 116 |

|   |                      | 7.3.8   | Example                                                          | 130 |

|   |                      | 7.3.9   | Implementation                                                   | 130 |

|   | 7.4                  | Concl   | usions                                                           | 133 |

| 8 | Fut                  | ure W   | ork                                                              | 135 |

### Chapter 1

### Introduction

An *intra*procedural register allocator performs register allocation individually on each procedure. Common policy in current compilers using only intraprocedural register allocation is to spill a register at a call site if the register might be used by both the caller and callee. To avoid spilling a register around a call, an intraprocedural register allocator may choose not to allocate a register across a call.

An *inter*procedural register allocator, given the register needs of each procedure and the frequency of each call, can improve upon an intraprocedural register allocation. For example, an interprocedural register allocation can allocate different registers to a caller and callee to try to avoid register spilling across the call. Also, given an estimate of the procedure call frequencies, an interprocedural register allocator can try to spill registers across infrequent calls.

To estimate the register needs of each procedure, we generate an intraprocedural register allocation. An intraprocedural register allocator may assign registers to live ranges, whose interference relation can be non-transitive [Cha82]. The interference relation for interprocedural register allocation is transitive. When finding an interprocedural register allocation with no register spilling across calls, if procedure P calls Q, then we assign different registers to P and Q. If procedure Q calls R, then we assign different registers to P, Q, and R.

#### 1.1 Contributions

This thesis presents two approaches for finding a minimum cost interprocedural register allocation. In both approaches we model the benefit associated with allocating varying numbers of registers to each procedure. In the second approach we also model the cost of spilling registers across calls.

#### 1.1.1 A DAG-Based Approach to Interprocedural Register Allocation

We refer to the first technique as a *DAG-based* approach to finding an interprocedural register allocation. Computing a minimum cost allocation involves recursively simplifying a DAG, while searching the solution space. This approach, which is discussed in Chapter 3, models only a save-free allocation (no register spilling along the call edges). By not spilling registers around calls, some locals that are frequently referenced may not be allocated registers. We choose to add a simple heuristic as a postpass to introduce register spilling.

Though this algorithm is interesting, the worst-case time complexity of our DAG-based approach is exponential. We are able to find interprocedural register allocations for only a few of the SPEC92 benchmarks.

#### 1.1.2 A Network Flow Approach to Interprocedural Register Allocation

Our next approach, which we discuss in Chapter 4, computes an interprocedural register allocation using network flows. This approach is more general than our DAG-based approach, as it allows us to model more aspects of interprocedural register allocation and can be solved in polynomial time. First, we present a dual network flow problem that finds a minimum cost save-free interprocedural register allocation. Next, we extend our model of interprocedural register allocation to include register spilling, and revise our network flow formulation.

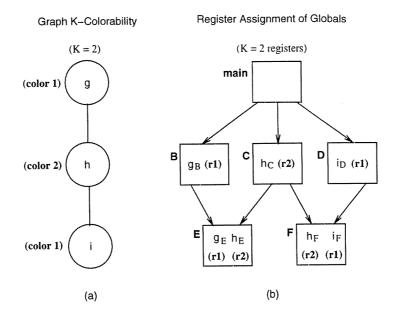

Our last addition to the network flow-based approach involves modeling register allocation of globals. Wall[Wal86] proposes allocating registers to globals throughout the entire call graph. Wall's model is simple to add to our existing solution for interprocedural register allocation of locals with spilling. Santhanam and Odnert[SO90] propose allocating registers

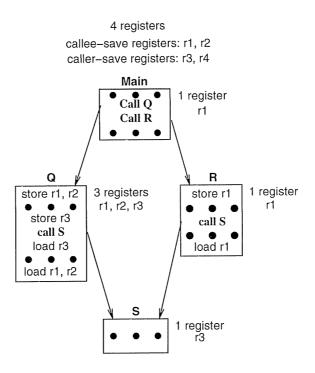

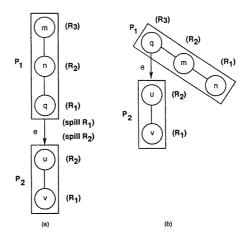

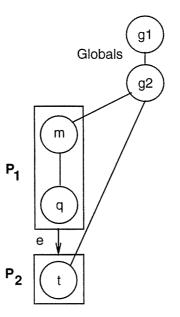

Figure 1.1: Call graph with an intraprocedural register allocation with 4 available registers.

to globals over an entire subgraph of the call graph. We further refine their approach by allowing register-allocated globals to be spilled within a subgraph. This allows sharing of registers between locals and globals in a subgraph.

## 1.2 A Comparison of Intraprocedural and Interprocedural Register Allocation

By convention some compilers, using *intra*procedural register allocation, designate certain registers to be saved by either the caller or callee in a procedure call [CHKW86]. Often callee-save registers contain variables that are live across a procedure call. Callee-save registers are saved only once on entrance to a procedure and reloaded upon return from the procedure, instead of spilling the register around each call. Caller-save registers are spilled if they are live across calls. These registers usually contain values not live across calls to avoid a store before a call and a reload after the call.

Figure 1.1 presents a call graph in which there are four available registers. Registers

r1 and r2 are callee-save registers and r3 and r4 are caller-save registers. The registers referenced by a procedure are shown to the procedure's right. In the call from procedure Main to procedure Q, Main, the caller, does not have any caller-save registers live across the call. However, Q, the callee, references two callee-save registers, r1 and r2 and, therefore, saves these registers on entrance to Q and reloads them upon returning from Q. In the call from procedure Q to procedure S, caller-save register r3 is live across the call to S. This register is saved and restored around the call. If Q called S multiple times, then a calling convention in which r3 is a callee-save register would result in a better register allocation. In this case r3 would be saved on entrance to Q and reloaded upon returning from Q. Thus, a compiler restricted by a fixed spilling convention may find it has too few caller or callee-save registers.

In the call from Q to S, S is the callee and references r3, which is a caller-save register. Thus, r3 is not spilled on entry to S. In the call from procedure Main to procedure R, R, the callee, references callee-save register r1. Thus, R saves r1 on entry to R and restores r1 upon return.

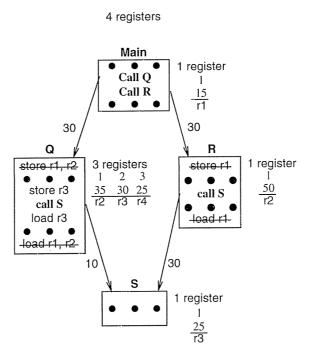

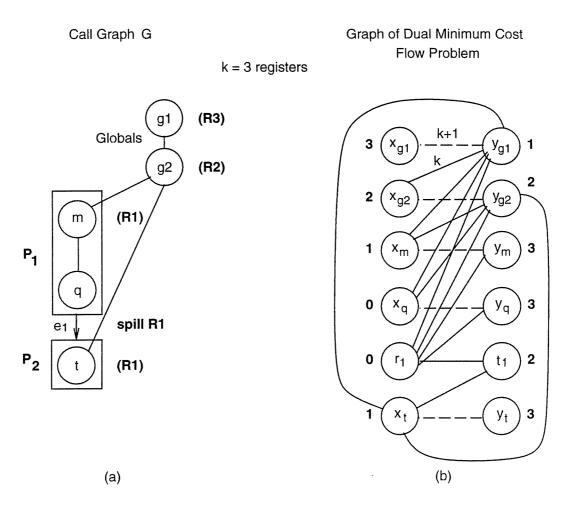

Figure 1.2 shows an interprocedural register allocation on the call graph of Figure 1.1. Next to each procedure is a table showing the benefit of allocating each additional register to a procedure. For example, procedure Q can productively use three registers. The benefit of allocating the first register is 35. The additional benefit of allocating a second register is only 30. Allocating a third register to Q adds a benefit of 25. A benefit can be an estimate on the number of dynamic loads and stores removed by allocating an additional register to a procedure. To estimate the register needs of each procedure, an intraprocedural register allocation can be performed on each procedure before an interprocedural register allocation.

The number next to each call edge is the frequency of the call. We model register spilling along the call edges. The cost of spilling a register around a call is a function of the call's frequency.

Assume each procedure is given its desired number of registers. The registers assigned to each procedure are shown below the benefits. With an intraprocedural register allocation, there can be a path through the program's execution where some registers are never

Figure 1.2: Call graph with an interprocedural register allocation with four available registers. The additional benefit for allocating each register to a procedure is shown. The number next to a call edge represents the frequency of the call.

referenced, while others are referenced and spilled multiple times. With an interprocedural register allocation, in some cases we can avoid these spills by allocating one of the unreferenced registers.

In an interprocedural register allocation, a register must be spilled only if there is a call path between two procedures and both procedures are assigned that register. By assigning register r1 in procedure Main and registers r2, r3, and r4 in Q, as shown in Figure 1.2, we can avoid the save and restore of r1 and r2 present in the intraprocedural register allocation of Q. Similarly, by assigning r2 to procedure R, the save and restore of r1 in R can be avoided.

If there is no call path between two procedures, these procedures can be assigned the same register. For example, both Q and R are assigned register r2.

An interprocedural register allocator can consider call frequency to determine where to spill a register. For example, five registers are needed along the path from Main to Q to S in the call graph, but there are only four available registers. An interprocedural register allocator can choose to spill a register along the call edge from Q to S, which has a frequency of 10, instead of the call from Main to Q, which has a frequency of 30.

Assume the cost of spilling a register around a call is twice the frequency of the call (one for a store and one for a load). In this case, an interprocedural register allocator could choose to avoid spilling the register around the call from Q to S, and not allocate a register to procedure Main. The benefit of this allocation is an improvement of 5 over the previous allocation, since the cost of the save/restore is 20 and the benefit of allocating a register to Main is only 15. We assume each procedure may always access a few temporary registers. The variable in Main that would have been assigned the extra register could be assigned a temporary register instead.

#### 1.3 Context for Interprocedural Register Allocation

To perform interprocedural register allocation, our approach requires a measure of the register needs of each procedure and the cost of spilling registers across calls. The register needs

of a procedure can be estimated by the number of register references from an intraprocedural register allocation. A profile can be used to compute the number of dynamic register references in a procedure and the frequency of each call. We assume the cost of spilling a register across a call is twice the frequency of the call (one for a load and one for a store).

Given the information of the register usage and call frequency, we generate an interprocedural register allocation. In our approach, we recompile the code with this additional information. However, one could also perform interprocedural register allocation at link time [Wal86].

Since library routines are pre-compiled, we assume a fixed calling convention across calls to these routines. In this thesis, we examine the benefit of including library routines in the interprocedural register allocation. We also assume a fixed calling convention across indirect calls, since we do not know the frequency in which the caller invokes the callee.

#### 1.4 Thesis Overview

In Chapter 2 we present architectural and software approaches to interprocedural register allocation. Chapter 3 presents our DAG-based approach to solving the interprocedural register allocation problem. With this approach we recursively simplify the call graph. Our second approach, which is discussed in Chapter 4, finds an interprocedural register allocation by solving a dual network flow problem. In Chapter 5, we prove the correctness of our network flow approach. To solve the dual network flow problem, we transform it into a primal network flow problem. Chapter 6 discusses this transformation. We extend our network flow-based interprocedural register allocator to include register allocation of globals in Chapter 7.

### Chapter 2

## Related Work

In this chapter, we present previous work related to interprocedural register allocation. First, we present architectural solutions and then we present software solutions.

## 2.1 Architectural Support to Avoid Saving and Restoring Registers Across Calls

Architectural solutions have been proposed to reduce or eliminate saving and restoring of registers across procedures calls [Moo85] [BDM87] [Hen84]. However, there are drawbacks to each of these approaches.

The architecture of the Symbolics 3600 is a modern implementation of a stack-based architecture [Moo85]. The instruction set includes 0-address instructions, in which an instruction pops all of its operands from the top of the stack, and 1-address instructions, in which one operand can be accessed from within the stack, but the other operands are accessed from the top of the stack. The few virtual-memory pages corresponding to the top of the stack are kept in a stack buffer, a fast-access memory. If at a procedure call, there is insufficient space for the next stack frame, pages containing older frames are spilled to memory, allowing the next frame to be added. Since operands are referenced off of the stack, interprocedural register allocation is not applicable.

A register-based machine has advantages over this stack-based approach. For example,

the operands in a stack-based machine can be less easily accessible than in a register-based machine. If an instruction in a stack-based machine references two operands, neither of which are at the top of the stack, an instruction is needed to move an operand to the top of the stack. A register-based machine can be more flexible, as an instruction can usually access its operands from among several registers.

A motivation in the design of the CRISP architecture [BDM87] [DM82] was to avoid register saves and restores around procedure calls. CRISP uses a stack cache, which is a set of registers containing the top elements of the stack, which can be accessed efficiently. The stack cache is addressable like memory. This means that aliased variables that cannot be kept in registers can be kept in the stack cache.

Instruction operands of the form "stack pointer plus offset" are computed before the instruction is stored in the instruction cache, saving a pipeline stage. One drawback of this approach is that a context switch causes the stack cache to be flushed to memory. A large stack cache can lead to a longer context switch.

Register windows [Hen84] [HP90] [Pat85] is an approach that tries to avoid saving registers across procedure calls. At each procedure invocation, the callee receives a bank (window) of registers. To allow for parameter passing, the caller's window can overlap with the callee's window. Register windows can be implemented as a circular buffer to give the perception of an unlimited number of register banks. Window overflow occurs when the buffer is full at a procedure call. The registers in a window are spilled to make room for the caller's registers. A drawback of implementing register windows is the additional cost and complexity. In addition, procedures need different numbers of registers. Wall found that a fixed-size register window can be inappropriate [Wal88].

#### 2.2 Software Support for Interprocedural Allocation

In this section we examine software solutions to interprocedural register allocation. This research is motivated by Wall's seminal work on global register allocation at link time [Wal86].

#### 2.2.1 Wall's Approach

Link time allocation allows for information to be used for interprocedural register allocation that otherwise is unavailable under separate compilation. First, the frequently referenced variables can be allocated registers, since the frequency of variable references in all procedures can be estimated at link time. Second, variables that are simultaneously live can be determined from the call graph (which can be constructed when all procedures are available). Assume procedure A calls B. Locals in A that are live across the call to B must have their registers saved if their registers are to be assigned to the locals in B.

To support register allocation at link time, the compiler annotates the object code in each module. For each procedure, the compiler generates a list of locals, the procedure call frequency, and frequency of variable references. To estimate the frequency a variable is referenced, the number of times in which a variable is referenced in a procedure is multiplied times the estimated frequency in which the procedure is called. To compute the estimated frequency in which a procedure is called, Wall adds the number of calls of the procedure, weighting calls in loops by a factor of 10.

Once an estimate on the number of references for each variable is known, Wall assigns each variable to a group, such that all the variables in a group can be assigned the same register. Each global variable is allocated to a singleton group. A frequency is computed for each group based on the frequencies of its elements. The groups with the largest frequencies are assigned registers.

Wall found substantial improvements in the execution of six benchmarks, as shown in Figure 2.1. Each improvement is over an *intra*procedural register allocation. Wall's machine had 64 registers of which 52 were available to his allocator. The first column (register allocation) refers to interprocedural register allocation with compile-time estimates. A procedure can allocate at most one local variable to each group, which is comprised of variables that will be assigned the same register. The second column (with coloring) refers to allowing a group entry to include multiple variables with non-intersecting live ranges from a single procedure—these candidates in a procedure can be assigned the same register. Graph coloring is used to select candidates with non-intersecting live ranges. The third

| Benchmarks | register   | with     | with    | with |

|------------|------------|----------|---------|------|

|            | allocation | coloring | profile | both |

| Livermore  | 18%        | 18%      | 19%     | 19%  |

| Whetstone  | 10%        | 10%      | 10%     | 10%  |

| Linpack    | 13%        | 13%      | 13%     | 13%  |

| Stanford   | 25%        | 25%      | 27%     | 28%  |

| Simulator  | 12%        | 14%      | 15%     | 16%  |

| Verifier   | 10%        | 15%      | 16%     | 19%  |

Figure 2.1: Percentage improvement in speed with 52 registers al located to variables

column (with profile) refers to global register allocation using estimates from a profile of the program. The last column (with both) refers to using profiling and graph coloring.

Wall allows register spilling only across indirect and recursive calls. Our model of interprocedural register allocation with spilling subsumes Wall's model, as we allow register spills across all calls. Walls' allocator may not find the best allocation with respect to his model, since he allows infrequently referenced locals to be grouped together with frequently referenced locals. Our interprocedural register allocator with spilling finds allocations of minimum cost.

Wall [Wal88] compares the performance of register windows to link time allocation. For the register window approach, global variables were not kept in registers. A motivation for register windows is to avoid the interprocedural analysis needed to keep globals in registers. At link time the non-aliased global variables are known and can safely be allocated registers. Profile-based link time allocation performed better than register windows by approximately 5.4%, assuming that register windows does not increase the cycle time of a processor. The link time allocator uses procedure-call frequencies as well as frequencies of variable references. Register-windows can benefit from knowledge of the latter, as it uses the profile only to determine the most frequently referenced locals. Wall found the main advantage of the link time scheme is its ability to keep globals in registers.

#### 2.2.2 Steenkiste and Hennessy's Approach

Steenkiste and Hennessy [SH89] designed an interprocedural register allocator for LISP programs. Their algorithm allocates registers to locals in a bottom-up fashion over the call

graph. They found that LISP programs spend a large amount of time in procedures near the bottom of the call graph (leaf procedures). Since these procedures are executed most often, they are allocated registers first. Also, since they observed that the call graph is wider near the bottom, a local near the bottom of the call graph may tend to have fewer conflicts with other variables and, therefore, be easier to keep in a register than one near the top. When possible a procedure is allocated registers not used by descendants of the procedure in the call graph. Otherwise, registers are spilled across a call if they are used by both the caller and a descendant of the caller in the call graph.

Unlike Wall's algorithm, Steenkiste's algorithm allows locals that are not live during a procedure call to be assigned registers used by procedures invoked during the call. Steenkiste finds that his interprocedural register allocation algorithm shows a 10% reduction in the number of executed instructions. Reasons given for a worse performance than Wall's algorithm include the fact that Wall had more registers available, allocated global variables to registers, and his test programs were not as recursive. Recursion makes interprocedural register allocation less effective because the registers used in a recursive procedure must be spilled to avoid being overwritten in the next invocation of the procedure. In fact, in Steenkiste's work, most of the remaining stack accesses after the register allocation were due to recursion rather than due to lack of registers.

Steenkiste and Hennessy's approach may spill registers across frequently executed routines in the internal part of the call graph. The approach to interprocedural register proposed in this thesis considers call frequencies. We are able to avoid spilling registers across frequently executed calls.

#### 2.2.3 Chow's Approach

Chow [Cho88] presents a one-pass algorithm for interprocedural register allocation. Similar to Steenkiste's algorithm, Chow's algorithm uses a bottom-up traversal over the call graph. However, Chow's algorithm deals with incomplete procedure information, which can result from separate compilation.

Chow divides registers into two sets, callee-save registers and caller-save registers. When allocating registers to a procedures whose caller (parent in the call graph) has been processed

or is unknown, Chow saves all callee-saved registers used by the current procedure and its descendants in the call graph. This allows the procedure's caller to use the callee-save registers without conflict. The caller in this case assumes that caller-saved registers are in use. Thus, it is better to use the caller-save registers before the callee-save registers near the bottom of the call graph, which is a common optimization for leaf procedures.

Chow's results, which are not as good as those of Steenkiste, range from an improvement of 0% to 12% over *intra*procedural register allocation. Chow found that some of the save/restore overhead is minimized in intraprocedural register allocation because the allocator has the choice of which variables to put in caller and callee-save registers. He also felt 20 general-purpose registers is insufficient to allocate registers to variables to avoid spilling. His algorithm does not use profile information, which can be helpful in choosing where to spill registers.

#### 2.2.4 Santhanam and Odnert's Approach

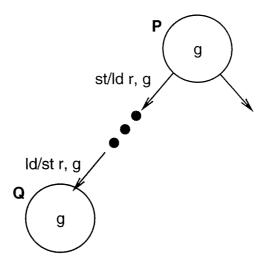

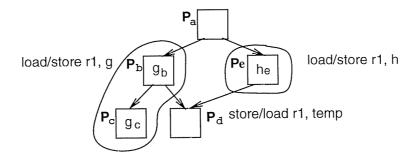

Santhanam and Odnert's approach to interprocedural register allocation [SO90] keeps global variables in registers throughout regions of the call graph. This improves upon Wall's approach in which once a global variable is assigned a register, the global variable keeps the register throughout the entire program. Santhanam and Odnert divide the references of each global variable into webs. A web is a minimal subgraph of the call graph such that neither an ancestor nor a descendant of a node in the subgraph references the global. The procedures covered by the web reference the global variable from a common register, thus avoiding loads and stores of the global within each procedure.

In this thesis, we generalize their notion of webs by allowing a register assigned to a global to be spilled within a web. The register may then be allocated to a local.

They also do interprocedural register allocation in *clusters* of frequently called procedures. The procedures in a cluster are dominated by a single procedure within the cluster, called the root node of the cluster. We refer to the root node of the current cluster as C. A cluster, however, can include the root nodes of other clusters, but no other nodes in those clusters. We refer to other cluster root nodes that are in the current cluster as O. A non-root node, therefore, is in the cluster that immediately dominates it.

The algorithm tries to place spill code for registers only at the entrance to a cluster (C), if the procedures represented by the nodes in the cluster are called more frequently than C. The algorithm visits each cluster using a bottom-up ordering, trying to allocate registers that have not been spilled by clusters O. This can allow spill code from cluster roots O in the current cluster to be moved to C, if the register is not referenced along paths between C and O (this idea is similar to moving code in a loop to the loop header). They add spill code at the root of the cluster for registers used in the current cluster.

Santhanam and Odnert find that spill code motion using clusters is not as effective as using webs to allocate registers to globals. Using a profiler they found that the combined benefit of spill code motion and allocating registers to globals is between 2% to 9% over interprocedural register allocation in their compiler.

The approach we propose in this thesis examines the *entire* call graph to generate a minimum cost allocation that spills registers as inexpensively as possible.

#### 2.2.5 Conclusions

As shown by Wall and suggested by Chow, a profile of a program can improve the allocation of an interprocedural register allocator. Comparing the impact of a real and estimated profile will be investigated in this thesis.

Wall's allocator spills registers only in the case of recursion and indirect calls. Since Steenkiste and Hennessy perform a bottom-up allocation of the call graph, their approach may introduce register spilling around frequently executed calls near the top of a call graph. Only Santhanam and Odnert considers call-frequency when choosing where to spill registers. However, they limit spill code motion to cluster roots. In this thesis, we present an allocator that examines the entire call graph to select the placement of spill code.

Work by Wall and Santhanam and Odnert reveals the importance of allocating registers to globals. In Wall's approach, globals allocated registers remain in those registers throughout the entire execution. Santhanam and Odnert allow globals to be allocated registers in procedures where they are not referenced, which can sometimes be profitable, as this would avoid reloading the value of the global into a register. However they do not consider the potential benefit of spilling a register-allocated global and allocating that register to a local.

This refinement will be investigated in this thesis.

\*

•

### Chapter 3

# A DAG-Based Approach

In this chapter, we present an algorithm for finding a save-free minimum cost interprocedural register allocation of local candidates. A save-free allocation does not spill registers across calls. First, we present our model for interprocedural register allocation. Then, we propose an algorithm for finding a save-free minimum cost interprocedural register allocation for call trees, which are call graphs whose structure is a tree. Next, we use the algorithm for call trees to find a save-free interprocedural register allocation for call graphs with shared procedures, which are procedures with more than one parent, only at the leaves. We then generalize our approach to allow for arbitrary acyclic call graphs. Recursive procedures, which represent cycles in the call graph, can be handled by replacing strongly connected components with a single node[SH89]. We also incorporate a heuristic for register spilling around calls to increase the number of candidates that are allocated registers.

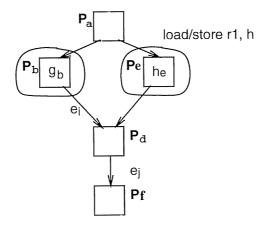

#### 3.1 Modeling Interprocedural Register Allocation

In the call graph each procedure  $P_i$  is represented by a node. Assume  $P_i$  has n children. The children of  $P_i$  are represented as  $P_{i_1}, \ldots, P_{i_n}$ . Calls between procedure  $P_i$  and  $P_{i_j}$  are represented as an edge between these nodes. The edge has a frequency  $Freq[P_i, P_{i_j}]$ , representing the number of times  $P_i$  calls  $P_{i_j}$  in the execution.  $Freq[P_i]$  is the total number of times  $P_i$  is called over the entire execution.

The algorithms discussed in this chapter assume a "cost" of executing instructions in

a procedure at varying register levels. We choose to represent this cost as the number of memory references, since the number of memory references varies directly with the number of available registers.  $Mem[P_i, r]$  is the expected number of dynamic memory references of procedure  $P_i$  given r registers to the procedure.

Function values for Mem have two interesting properties. The first is that  $Mem[P_i, r] \ge Mem[P_i, r+1]$ . This means that the cost of a procedure's execution does not increase as more registers are available to the procedure. We also assume that  $Mem[P_i, r-1] - Mem[P_i, r] \ge Mem[P_i, r] - Mem[P_i, r+1]$ ; that is, the benefit of allocating registers to a procedure is monotonically non-increasing. This means that allocating the  $r^{th}$  register does not result in a bigger benefit than allocating the  $r-1^{st}$  register (any reasonable register allocator will use each additional register to its best advantage).

The total cost of allocating r registers to procedure  $P_i$  and all of its descendants in the call graph is represented as  $Cost[P_i, r]$ . In our case,  $Cost[P_i, r]$  represents the total number of memory references, distributing r registers among  $P_i$  and all its descendants.

#### 3.2 Minimum Cost Allocation for Call Trees

This section presents an algorithm for finding a minimum cost allocation of procedures' local variables in a call tree. Since we are dealing with call trees each callee has only one caller. For each procedure in a call tree an equal number of registers will be allocated to the subtrees rooted at each of its children, since the procedures in one of its children's subtrees can never be simultaneously active with the procedures in another. Given R registers, no more than R registers can be allocated along any path from the root to a leaf in a call tree.

#### 3.2.1 Measuring Cost

Given a call tree with a frequency along each edge as determined by function Freq, a maximum number of available registers R, and a function Mem for each procedure at each register level, a Cost function will be defined and computed for the subtree rooted at each procedure for each register level. Based on this function a distribution of registers,  $n_p$  and  $n_c$ , will be computed for each procedure and its subtrees rooted at the children, respectively.

Apportioning r registers among  $P_k$  and its descendants, and assuming  $P_k$  has n children, we represent Cost as:

$$Cost[P_k, r] = \underbrace{MIN}_{n_p + n_c = r; \ n_p, n_c \ge 0}$$

$$Freq[P_k] * Mem[P_k, n_p] + \sum_{i=1}^{n} Cost[P_{k_i}, n_c].$$

The cost of  $P_k$  when allocated  $n_p$  registers  $(Mem[P_k, n_p])$  is multiplied by the frequency in which  $P_k$  is invoked  $(Freq[P_k])$  to give the cost of allocating  $n_p$  registers to  $P_k$  for the entire execution. We add this cost to the total cost of allocating  $n_c$  registers to the subtrees rooted at each child  $P_{k_i}$  of  $P_k$ .

This function defines the least cost of distributing r registers to the subtree rooted at  $P_k$  by considering all possible partitions of r registers to  $P_k$  and the subtrees rooted at its children. Inductively, we have computed a minimum cost allocation at each register level for subtrees rooted at  $P_{k_i}$ . If necessary, by trying all partitions of r registers between  $P_k$  and the subtrees rooted at its children, we can determine the minimum cost allocation of r registers for the subtree rooted at  $P_k$ .

#### 3.2.2 Generating an allocation

An allocation can be computed using dynamic programming. The algorithm maintains the least cost distribution of r registers,  $0 \le r \le R$ , between each procedure and its subtrees rooted at the children. We assign the value of  $n_p$  to a table entry indexed by  $\{P_k, r\}$  when  $Cost[P_k, r]$  is computed. This entry tells us how to distribute r registers between procedure  $P_k$  and its subtrees. Once the table entries have been determined at all register levels between 0 and R for all procedures, it is easy to find the number of registers to assign to each procedure. Given the number of registers available for a subtree whose root is  $P_k$ , we can determine, using the table, the number of registers to give to  $P_k$  and its subtrees. We can recursively walk down the call tree applying this information to each subtree. The recursion begins by using the table entry indexed by  $\{P_0, R\}$ , where  $P_0$  is the root of the call tree, to determine the number of registers to give to  $P_0$  and its subtrees.

#### 3.2.3 Complexity

This algorithm has a complexity of O(P), where P is the number of procedures. A naive implementation has a constant term of  $R^2$ , where R is the number of registers, since there are at most R+1 way of distributing r registers, where  $n_p+n_c=r$  and  $0 \le r \le R$ . However, because of the monotonicity property we can compute the distribution of r registers given the distribution of r-1 registers. We give the additional register to either the parent or its children, depending on which results in a greater benefit. Thus, the constant of  $R^2$  can be reduced to R.

#### **3.2.4** Example

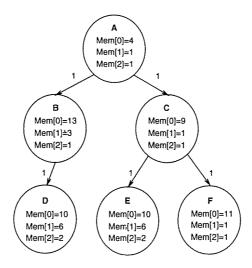

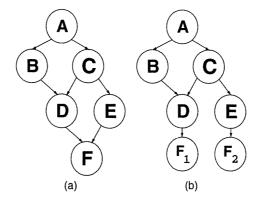

Figure 3.1 gives an example call tree. Assume there are only two registers available. The values of function Mem for each procedure at each register level are shown inside the nodes. Procedures A, C, and F have only one register candidate—there is no extra benefit for allocating a second register; that is, for each of these procedures Mem[1] = Mem[2]—whereas all other procedures have two register candidates. The frequencies, which are all 1, are shown along the edges of the call tree. The values of the cost function for each procedure at each register level is shown in Figure 3.2. Next to each entry  $Cost[P_k, j]$ , we display  $n_p$  p and  $n_c$  c, which are the distribution of the j registers—the parent is given  $n_p$  registers and the subtrees rooted at the children are given  $n_c$  registers.

Since the frequency along each incoming edge to a leaf is 1, the values of the cost functions for the leaves, shown in the uppermost table of Figure 3.2, correspond to the values of function Mem for each node. In the lower table, we have the cost functions and register distribution for the other nodes. For example, Cost[B,1], the cost of allocating 1 register to the subtree rooted at B, allocates the 1 register to B, because of the greater benefit,  $Freq[B]*(Mem[B,0]-Mem[B,1]) \ (=10) > Cost[D,0]-Cost[D,1] \ (=4)$ . Cost[B,2], however, allocates the second register to D, since Freq[B]\*(Mem[B,1]-Mem[B,2]) = 2 and Cost[D,0]-Cost[D,1] = 4. Cost[C,1] allocates its first register to E and E, since E and E are the final allocation assigns one

Figure 3.1: Example call tree to illustrate register allocation of locals.

|   | Cost Tables    | Alloc  | Cost Tables    | Alloc  | Cost Tables    | Alloc  |

|---|----------------|--------|----------------|--------|----------------|--------|

|   | Cost[D,0] = 10 | 0p, 0c | Cost[E,0] = 10 | 0p, 0c | Cost[F,0] = 11 | 0p, 0c |

|   | Cost[D,1] = 6  | 1p, 0c | Cost[E,1] = 6  | 1p, 0c | Cost[F,1] = 1  | 1p, 0c |

| - | Cost[D,2] = 2  | 2p, 0c | Cost[E,2] = 2  | 2p, 0c | Cost[F,2] = 1  | 1p, 0c |

| Cost Tables                    | Alloc  | Cost Tables                    | Alloc  |

|--------------------------------|--------|--------------------------------|--------|

| Cost[B,0] = 13 + 10 = 23       | 0p, 0c | Cost[C,0] = 9 + (10 + 11) = 30 | 0p, 0c |

| Cost[B,1] = 3 + 10 = 13        | 1p, 0c | Cost[C,1] = 9 + (6 + 1) = 16   | 0p, 1c |

| Cost[B,2] = 3 + 6 = 9          | 1p, 1c | Cost[C,2] = 1 + (6 + 1) = 8    | 1p, 1c |

| Cost[A,0] = 4 + (23 + 30) = 57 | 0p, 0c |                                |        |

| Cost[A,1] = 4 + (13 + 16) = 33 | 0p, 1c |                                |        |

| Cost[A,2] = 4 + (9 + 8) = 21   | 0p, 2c |                                |        |

Figure 3.2: Example call tree and cost tables for each procedure.

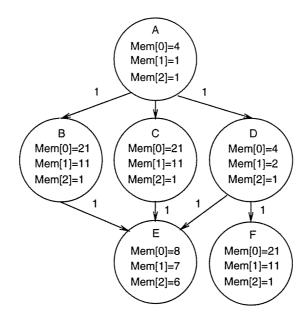

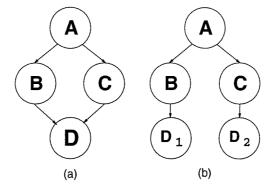

Figure 3.3: Children of a node can be allocated a different number of registers in a minimum cost register allocation of a DAG.

register to B, C, D, E, and F.

# 3.3 Minimum Cost Interprocedural Register Allocation for DAGs

Given R registers, an allocation for a DAG allows no more than R registers to be allocated along any path from the root to a leaf. Unlike in the call tree case, the number of registers allocated to each child of a procedure can differ in a minimum cost allocation of a DAG. For example, in Figure 3.3, the benefit of allocating two registers to B, C, or F is 20, since for each of these procedures, 1\*(Mem[0]-Mem[2])=20 (each of these procedures is called once). However, the benefit of allocating two registers to E is 3\*(Mem[0]-Mem[2])=6 (E is called three times). Assuming two registers are available, a minimum cost allocation of the DAG in Figure 3.3 assigns two registers to nodes B, C, and F, and 0 registers to the remaining nodes. D's child E is allocated 0 registers, but child F is allocated two registers. If neither B nor C called E, then this call graph would be a tree, and E, like its sibling F, would be allocated two registers.

To find an minimum cost solution for a DAG, the DAG is first simplified by collapsing subtrees into a singleton node using the register allocation algorithm described in Section 3.2.2. The *Cost* functions in the root nodes of these subtrees become *Mem* functions for the singleton nodes. After collapsing subtrees, the DAG can have shared nodes (more than one incident edge) at the leaves and possibly at the internal nodes. We call a shared leaf node a "level-1" node, and a shared node internal to the DAG a "level-i" node, if there are at most *i* shared nodes (including itself) along a path from it to a leaf.

Assume that after collapsing subtrees, a DAG's shared nodes are only at level-1 (shared nodes appear only as leaves of the DAG). We can split these shared nodes such that each parent has an edge incident on its own copy of the node. The DAG is now a tree. Assigning, in turn, each possible combination of register values to these copies, such that the copies of a shared node are allocated the same number of registers, we can find a solution using the allocation algorithm for trees.

To ensure that each copy of a shared node is allocated the same number of registers, r,  $0 \le r \le R$ , we can assign to each copy a cost of infinity below register level r, and a cost of b at register level r and above, where b is the cost of allocating r registers in the shared node. Each copy will allocate at least r registers, as there is an infinite decrease in cost between allocating r-1 and r registers. It is possible that more than r registers will be allocated to each copy if the registers beyond r cannot be profitably used elsewhere (there is no benefit, decrease in cost, in allocating more than r registers to each copy). However, a pass over the DAG after the allocation can limit the number of registers allocated to r.

If a DAG has i shared nodes at level-1, and there are R registers available, we would check no more than  $O((R+1)^i)$  combinations of register assignments. The allocation with the minimal cost is the best solution.

#### 3.4 Shortening the Search Space

Rather than checking all possible register values for each shared node (a potentially explosive process), we can shorten the search space using a branch and bound technique.

An important optimization involves tightening the bounds on the maximum and minimum number of registers that a shared node can have in a minimum cost solution for a DAG. Before computing the maximum and minimum bounds on the number of registers available to a shared node at level-1, we first precompute for each procedure  $P_k$  the expression

$$Mem'[P_k, j] = \sum_{i=1}^{n} Freq[P_i, P_k] * Mem[P_k, j]$$

for  $0 \leq j \leq R$ , where  $P_i$  is a parent of  $P_k$ ,  $Freq[P_i, P_k]$  is the frequency along the edge between  $P_i$  and  $P_k$ , and n is the number of  $P_k$ 's parents.  $Mem'[P_k, j]$  is the cost of executing  $P_k$  throughout the entire execution, assuming j registers are allocated in  $P_k$ . This has the effect of folding the call frequency of  $P_k$  into its cost function Mem'.

A call graph may contain transitive edges. A transitive edge connects two nodes, which are connected by a path that does not include this edge. Transitive edges affect the call frequency of a node, but do not further constrain the solution by affecting which registers can be shared among procedures. Since the call frequencies have been folded into the cost of allocating registers for each node, we can simply remove transitive edges from the call graph.

#### 3.4.1 Finding the Maximum Bound

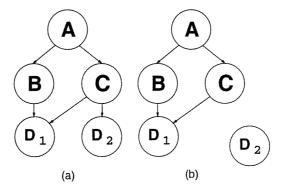

To find the maximum bound for a shared node at level-1, we split the shared node, such that each parent has its own copy (see Figure 3.4). We let each new leaf,  $D_1$  and  $D_2$  in Figure 3.4, have the same Mem' function as D in the original DAG. Using the register allocation algorithm for trees (using Mem' instead of Freq\*Mem), we compute the number of registers allocated to  $D_1$  and  $D_2$  (they need not be equal). Without loss of generality, assume  $D_1$  is allocated less than or equal to the number of registers allocated to  $D_2$ . Let r be the number of registers allocated to  $D_1$ . We now show that r is a maximum bound on the number of registers allocated to D in a minimum cost allocation.

We can add an edge between C and  $D_1$ , as shown in Figure 3.5(a). Since  $D_2$  is allocated at least as many registers as  $D_1$ , there are no more than R registers allocated along the path  $A-C-D_1$ . Because the edge does not affect the number of registers allocated to each

Figure 3.4: Splitting a shared leaf node.

Figure 3.5: Adding an edge between nodes C and  $D_1$ , and decreasing the number of registers allocated to  $D_2$  produces a DAG in which  $D_1$  has at least as many registers as D of the original DAG.

node, a minimum cost allocation of the tree before the edge is added is still a minimum cost allocation after the edge is added.

Now we decrease the benefit of allocating registers to  $D_2$ . Registers previously available to  $D_2$  may now be allocated to  $D_2$ 's ancestors. Since  $D_1$  was allocated less than or equal to the number of registers allocated to  $D_2$ , additional registers allocated to  $D_2$ 's ancestors may lead to fewer registers allocated to  $D_1$  (the number of registers allocated along each path from the root to a leaf cannot exceed R). The total number of registers allocated to  $D_1$ , however, will not exceed its original value of r. Decreasing the benefit of allocating registers to  $D_2$  has the effect of removing  $D_2$  from the DAG (Figure 3.5(b)). The DAG in Figure 3.5(b) now has the same structure as the DAG in Figure 3.4(a). The total number of registers allocated to  $D_1$  in Figure 3.4(a), r, is a maximum bound on the number of registers allocated to the shared node D.

#### 3.4.2 Finding the Minimum Bound

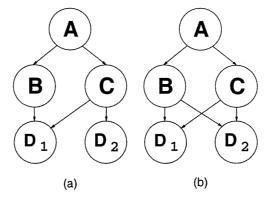

To compute the minimum bound for a shared node at level-1, we compute Mem' and split the shared node, such that each parent has its own copy, as was done for computing the maximum bound (Figure 3.4). However, the Mem' function for each copy is the function Mem' of D divided by p, where p is the number of parents of the shared node D. In our example, p is 2. Next, we find a solution for the tree in Figure 3.4(b). Without loss of generality, assume  $D_1$  has less than or equal to the number of registers available to  $D_2$ . Let the current number of registers allocated to  $D_1$  be r. We now show that r is a minimum bound on the number of registers allocated to D in a minimum cost allocation.

As in the case for finding the maximum solution, we add an edge between C and  $D_1$  (see Figure 3.6(a)). In our next step, we add an edge between B and  $D_2$  (see Figure 3.6(b)). The path  $A-B-D_2$  may allocate more than R registers, since  $D_2$  is allocated at least as many registers as  $D_1$ . If we remove registers from A or B, then  $D_1$  can be allocated more than r registers, bringing the number of registers allocated to  $D_1$  up to  $D_2$ 's level. If we remove registers from  $D_2$ , the number of registers available to  $D_2$  will not drop below  $D_1$ 's count;  $D_1$  and  $D_2$  have the same constraints with the other nodes, they will have the same number of registers. We can combine  $D_1$  and  $D_2$  into a single node transforming the DAG

Figure 3.6: Adding constraints between nodes C and  $D_1$ , and B and  $D_2$ .

Figure 3.7: We can combine nodes  $D_1$  and  $D_2$  to transform the DAG into the original DAG.

of Figure 3.6(b) into the original DAG of Figure 3.7. The sum of the Mem' functions of  $D_1$  and  $D_2$  equals that of D. Since the Mem' function of D is greater than that of  $D_1$  and the number of registers now allocated to  $D_1$  is greater than or equal to r, r is a minimum bound on the number of registers allocated to D.

#### 3.5 Level-n Shared Nodes

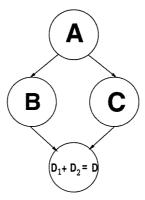

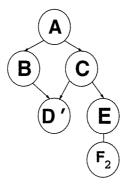

We can recursively apply the register allocation algorithm for DAGs with level-1 shared nodes to generate an allocation for DAGs with level-n shared nodes. Assume, for example, that we want to find an allocation for the DAG with the level-2 shared node (D) in Figure 3.8(a). We apply our algorithm for level-1 shared nodes to split the shared node F at level-1 into  $F_1$  and  $F_2$  (Figure 3.8(b)) to find minimum and maximum bounds on the number of registers to be allocated to F. Treating the level-2 shared node D as the root of

Figure 3.8: To find an allocation for the level-1 shared nodes we first split the level-1 shared nodes.

Figure 3.9: We collapse the subtree rooted at D into a new node D'. We then find the allocation for the new DAG, in which D' is a level-1 shared node.

a subtree, our allocator computes a cost function and allocation for the subtree rooted at D. We collapse the subtree rooted at D to form a new node D' (Figure 3.9).

If we can determine the minimum cost allocation for D', we can determine the allocation for each node within the corresponding subtree. D' can be treated as a level-1 shared node. We now have a new level-1 DAG for which we know how to generate its register allocation and, thus, we can determine the number of registers allocated to D'. Once we know the allocation for D', we can compute the allocation at the split nodes  $F_1$  and  $F_2$ .

Computing the cost of allocating registers within the minimum and maximum bounds is identical to the process outlined above.

#### 3.6 Complexity

The complexity of our algorithm is exponential in the worst case. As the height of the call graph increases by one, we may double the amount of work needed to find an allocation. This leads to an exponential worse case time complexity.

#### 3.7 Register Spilling

By using a save-free allocation we have avoided adding spill code around calls. Procedures, however, may need more registers than are allocated by a save-free register allocation. Our approach for adding register spilling allows procedures that can use additional registers to spill registers used by an ancestor or descendant in the call graph. Registers allocated save-free to an ancestor of a procedure p can be saved and restored on entrance and exit to p (treated as a callee-save register), and save-free registers used by a descendant of p can be saved and restored around calls in p (treated as a caller-save register). We choose to spill registers in which the least cost is incurred and only if it is profitable—the cost of the added spill to a procedure is less than the benefit of an additional register.

To choose between allocating a caller-save or callee-save register, we provide our algorithm with a function  $Live[P_k, r]$ , which equals one if the  $r^{th}$  register is live across a call in  $P_k$ , and zero otherwise. We compute the cost of spilling a callee-save register in procedure  $P_k$  as  $2*Freq[P_k]$ , where the value 2 represents the store and load added to spill the register upon entering and exiting the routine, and  $Freq[P_k]$  is the frequency in which  $P_k$  is called. Letting  $P_{k_i}$  be one of the n children of  $P_k$ , we compute the cost of a caller-save register r as  $2*Live[P_{k_i}, r]*\sum_{i=1}^n Freq[P_k, P_{k_i}]$ . The benefit of an additional register for procedure  $P_k$  over the current register level r is simply  $Mem[P_k, r] - Mem[P_k, r+1]$ .

#### 3.8 Implementation

We implemented our algorithm using gcc [Sta93] on a DECstation 5000/125 with a MIPS R3000 processor. To generate a call graph and cost functions for performing interprocedural register allocation, we modified gcc to write information for each procedure on register

| speedup over gcc -O2 |           |               |  |  |  |

|----------------------|-----------|---------------|--|--|--|

| benchmark            | save-free | with spilling |  |  |  |

| compress             | 0.1%      | 0.5%          |  |  |  |

| decompress           | -0.4%     | 1.2%          |  |  |  |

| ear                  | -0.4%     | 0.3%          |  |  |  |

| eqntott              | -0.2%     | 0.1%          |  |  |  |

| ora                  | 0.3%      | 1.0%          |  |  |  |

Figure 3.10: Speedups of interprocedural register allocations with and without register spilling over gcc at optimization level 2.

usage. In addition, Gcc was modified to assume that all live ranges are not spilled (split) because of calls, rather than using the usual caller-save/callee-save convention of the MIPS architecture. This gives our interprocedural register allocator a better estimate of the benefit of allocating save-free registers, which are not spilled across calls.

We weight register references in loops by  $10^d$ , where d is the loop's nesting level. To compute function  $Mem[P_k, r]$ , the number of memory references for procedure  $P_k$  given r registers, we compute the total number of references of the r most referenced registers, as determined by gcc, and subtract this from the total number of references for the procedure. To compute  $Live[P_k, r]$ , we simply check whether the  $r^{th}$  most referenced register is live across a call. The interprocedural register allocator also reads a dynamic profile of the program. The allocator uses the profile to compute the frequency along the edges as well as to improve upon our estimation of function Mem. If procedure  $P_k$ 's execution represents p% of the total number of cycles t, we let  $Mem[P_k, 0] * Freq[P_k] = p\% * t$ , where  $Freq[P_k]$  is the number of times  $P_k$  is called.

The interprocedural register allocator generates information on the registers that are save-free and spilled. Gcc then reads this information to produce the corresponding interprocedural allocation. Our interprocedural register allocator could be included as part of a link time allocation as, for example, implemented by Wall [Wal86].

Figure 3.10 gives speedups from a few SPEC92 benchmarks[[Sp] of our save-free allocation and our save-free allocation followed by register spilling. As we have not performed

| benchmark  | time spent computing allocation           |  |  |

|------------|-------------------------------------------|--|--|

|            | as a percentage of total compilation time |  |  |

| compress   | 13.8%                                     |  |  |

| decompress | 12.0%                                     |  |  |

| ear        | 12.2%                                     |  |  |

| eqntott    | 22.1%                                     |  |  |

| ora        | 29.5%                                     |  |  |

Figure 3.11: Times for computing a minimum cost allocation with register spilling and allocation of globals as a percentage of the total compilation time.

interprocedural register allocation on library routines, each allocation (including gcc's) spills caller-save registers around library calls.

Adding register spilling to our approach generates only a small improvement over gcc's intraprocedural register allocation. A weakness of our approach is that we may have an insufficient number of callee-save registers or caller-save registers. We may have too few caller-save registers in a leaf routine, where we can avoid spilling a caller-save register. For a routine near the top of the call graph, spilling caller-save registers can be much more expensive then spilling a callee-save register. A caller-save register will be saved and restored around each call, whereas a callee-save register is saved and restored only upon calling and returning from the routine.

Our results indicate that a save-free allocation can be competitive with a gcc allocation. In addition, using our approach for spilling registers around calls, only a small benefit is achieved from register spilling.

Figure 3.11 presents the time finding an interprocedural register allocation as a percentage of the total compilation time without interprocedural register allocation. Our interprocedural register allocation represents a significant percentage of the total compilation time.

As mentioned in Section 3.4, our algorithm removes transitive edges to simplify a call graph. After removing transitive edges, the call graph for each of these benchmarks has a maximum shared level, the largest number of shared nodes along a path from the root of the call graph to a leaf, of three or less. On benchmarks with a shared level greater than

three, our algorithm required too much space on our machine.

In the next chapter, we present an interprocedural register allocator that applies a network flow approach. Applying network flows yields a much faster interprocedural register allocator that can efficiently find allocations for large call graphs.

### 3.9 Conclusions

This chapter presents a DAG-based minimum cost interprocedural register allocation algorithm. This algorithm has been extended to perform register spilling around calls. We found that for a sample of the SPEC92 benchmarks, a save-free approach is comparable with gcc's intraprocedural allocation, which may spill registers around calls. Unfortunately, due to the space required by this algorithm, we are able to run it only on a subset of the SPEC92 benchmarks.

## Chapter 4

# A Network Flow Approach

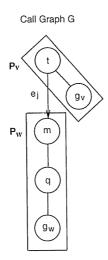

This chapter presents both a *save-free* interprocedural register allocator (which never spills registers across calls), and an interprocedural register allocator that spills registers as necessary across calls. Our save-free allocator models the cost of allocating registers to procedures and finds a minimum cost allocation. A profile is used to estimate the benefit of allocating different levels of registers to each procedure.

Our interprocedural register allocator that spills registers across calls minimizes the cost of allocating registers to procedures as well as spill cost. The cost of spilling a register across a call is a function of the call's frequency. Register spilling allows registers to be reassigned along a path in the call graph when profitable.

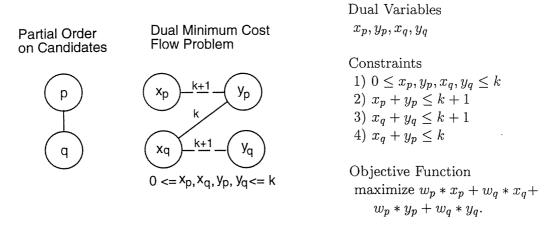

To generate a save-free interprocedural register allocation of a call graph, we utilize Cameron's algorithm for finding a maximum weight k-antichain in a partially ordered set [Cam85]. To find a maximum weight k-antichain, Cameron maps solutions from a dual minimum cost flow problem<sup>1</sup>. A dual minimum cost flow problem can be transformed into a minimum cost flow problem and solved in polynomial time. In Section 4.2, we generalize our allocation model to allow for register spilling across calls.

Our approach can be used with conventional compilers that translate one procedure

<sup>&</sup>lt;sup>1</sup>Cameron refers to the dual minimum cost flow problem as a dual transportation system of linear inequalities. When we transform this dual problem into the primal problem, the network flow graph is not bipartite and, thus, the primal problem is not a transportation problem. However, the primal problem is a minimum cost flow problem. We, therefore, refer to the dual as a dual minimum cost flow problem.

at a time. Each procedure may be translated using any of the well-known, high-quality, intraprocedural register allocators[BCKT89][CK91][PF92]. Then using profile information our minimum cost interprocedural register allocator determines how many registers each procedure will be given and where spills will be placed. A minimum cost interprocedural register allocation may not allocate registers to all locals in a procedure. For each of these procedures, an intraprocedural register allocator will generate a revised allocation using the procedure's interprocedurally allocated registers and the temporary registers available to each procedure.

### 4.1 Save-free Interprocedural Register Allocation

In this section, we describe a save-free interprocedural register allocator that determines the number of registers to allocate to the locals of each procedure for acyclic call graphs (cycles in call graphs normally force saves across recursive calls). Our solution is based on Cameron's algorithm for finding a maximum weight k-antichain in a partially ordered set [Cam85]. In Section 4.2, we generalize our allocation model to compute a minimum cost allocation that may include register spilling across calls in (possibly cyclic) call graphs.

For each procedure, we assume an intraprocedural register allocator has already grouped locals that can be assigned the same register. We refer to each group as a register candidate. An interprocedural register allocator selects which candidates are allocated registers. Each procedure has a few temporary registers available. Locals assigned these registers do not require interprocedurally allocated registers. These locals are correctly allocated at register allocation time.

Initially, we assume that a register candidates is live across all calls in a procedure. However, in Section 4.4 we distinguish between candidates not live across calls and candidates live across one or more calls.

Our interprocedural register allocator may give fewer registers to a procedure than the number of candidates it has. An intraprocedural register allocator can produce a valid allocation when given fewer registers. The intraprocedural register allocator will spill values internally as necessary. We assume there is a positive benefit associated with allocating a register to a register candidate. As more candidates are allocated registers the benefit of the allocation increases (and, equivalently, the cost associated with the allocation decreases). In our interprocedural register allocation, a benefit estimates the decrease in loads and stores from allocating a register to a candidate. Given k registers, our save-free interprocedural register allocator selects an allocation in which the benefits of register allocated candidates sum to a maximum (across all procedures). That is, registers are given to procedures that benefit the most.

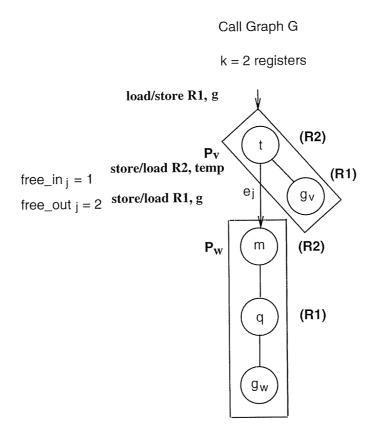

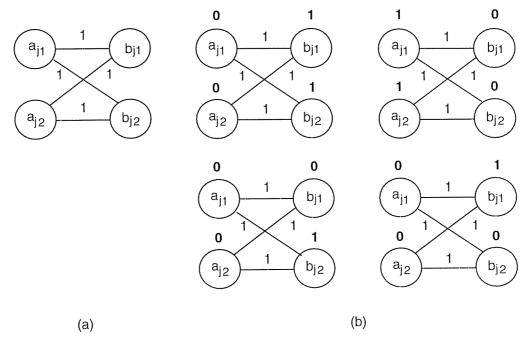

### 4.1.1 Defining a partial ordering on the candidates of a call graph

Let G = (P, E) be an acyclic call graph, where P is a set of procedures and E is a set of call edges. We represent the set of calls from procedure  $P_v \in P$  to  $P_w \in P$  as a single edge in the call graph. Let S be the set of register candidates in P. For procedure  $P_v \in P$ , let  $C(P_v)$  be the set of register candidates in  $P_v$ .

We define the following partial order ( $\sqsubseteq$ ) on candidates in an acyclic call graph such that there is an ordering between two candidates if and only if they cannot be assigned the same register in a save-free interprocedural register allocation:

- 1. In the partial order, assume the relation between candidates in a procedure is an arbitrary chain; that is, there is an ordering between every two candidates in the same procedure.

- 2. Let  $c_v \in C(P_v)$ ,  $c_w \in C(P_w)$ , and  $P_v \neq P_w$ . If there is a path from procedure  $P_v$  to  $P_w$ , then  $c_w \sqsubset c_v$ .

For  $c_i, c_j \in S$ ,  $c_i \sqsubset c_j$  is defined as  $c_i \sqsubseteq c_j$  and  $c_i \neq c_j$ . Given (1) and (2), there is an ordering only between two candidates of the same procedure or between candidates in separate procedures connected along a path in the acyclic call graph. Thus, either  $c_v \sqsubset c_w$  or  $c_w \sqsubset c_v$  for candidates  $c_w, c_v \in S$  if and only if  $c_w$  and  $c_v$  cannot be assigned the same register in the call graph.

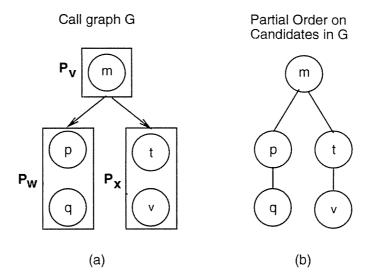

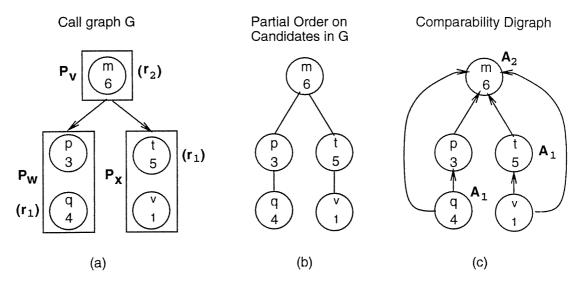

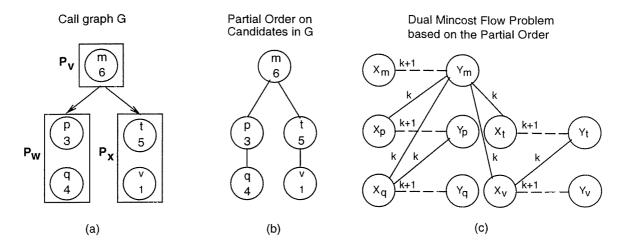

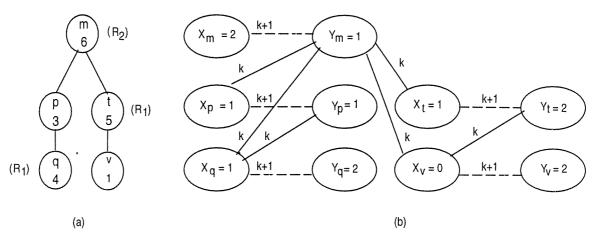

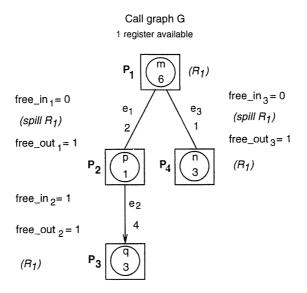

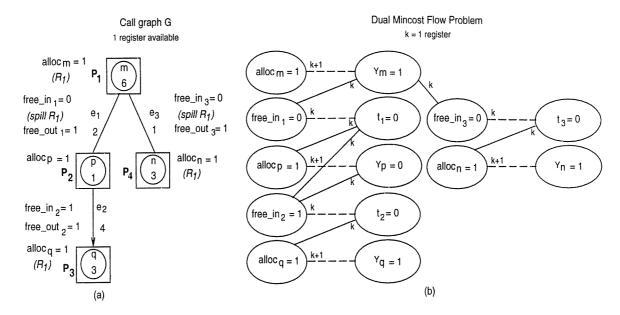

In Figure 4.1(a), procedure  $P_w$  has two candidates, p and q, and procedure  $P_x$  has two candidates t and v. A partial order on the candidates in the call graph appears in (b). We

Figure 4.1: An example call graph, allowing for multiple candidates in a procedure, and a partial order on the candidates of the call graph.

assume the ordering between p and q is  $q \sqsubset p$  and the ordering between t and v is  $v \sqsubset t$ . Since  $P_v$  calls  $P_w$ ,  $q \sqsubset m$  and  $p \sqsubset m$ , and since  $P_v$  calls  $P_x$ ,  $v \sqsubset m$  and  $t \sqsubset m$ .

Throughout Section 4.1, we assume  $(\sqsubseteq)$  refers to the partial order defined by (1) and (2).

### 4.1.2 Interference Graph

Let T be a set on which there is some partial order. Define a comparability digraph D(T) as having an edge from u to v when u is less than v in the partial order [Cam85]. If S is the set of candidates of a call graph G and the partial order is  $(\sqsubseteq)$ , then D(S) is the interference graph for a save-free interprocedural register allocation of G. If there is an edge between  $c_u$  and  $c_v$  in D(S), then either  $c_u$  and  $c_v$  are candidates in the same procedure, or  $c_u$  and  $c_v$  are candidates in procedures along a path in the call graph. Candidates  $c_u$  and  $c_v$  cannot be assigned the same register.

Since a partial order defines the interference relation between candidates in a save-free interprocedural register allocation, the interference graph is transitive. The interference graph for *intra*procedural register allocation, however, can be non-transitive[Cha82]. In an intraprocedural register allocation, two live ranges that interfere are assigned different

Figure 4.2: A call graph G, a partial order on the candidates in G, and the comparability digraph of the candidates in G.

registers. Assume live ranges  $l_a$  and  $l_b$  interfere and live ranges  $l_b$  and  $l_c$  interfere. Live range  $l_a$  does not necessarily interfere with  $l_c$ . In a save-free interprocedural register allocation, if procedure  $P_v$  calls  $P_w$  and  $P_w$  calls  $P_x$ , then execution will normally return to  $P_v$ . To avoid overwriting the registers live across a call, candidates in  $P_v$ ,  $P_w$ , and  $P_x$  are all assigned different registers.

Figure 4.2 displays a call graph G, the partial order ( $\sqsubseteq$ ) on the set of candidates, S, of G, and the comparability digraph D(S). The number below a candidate is the benefit of allocating a register to that candidate. Since  $q \sqsubseteq p$  and  $p \sqsubseteq m$ , there is an edge in D(S) between q and p, p and m, and q and m. These three candidates can never be assigned the same register. Candidate t can be assigned the same register as p or q, as there is no edge joining either t and p or t and q.

### 4.1.3 Antichains

We call a set of nodes in a digraph independent if none of the nodes in the set are joined by an edge. Let S be a set and assume some partial order on S. An antichain in S is an independent set of nodes in D(S). In Figure 4.2(c),  $\{p,t\}$ ,  $\{p,v\}$ ,  $\{q,v\}$ , and  $\{q,t\}$ are examples of antichains, as the candidates in each set are not joined by an edge in the comparability digraph. A k-antichain is the union of at most k antichains [Cam85]. Both  $\{p, t, q, v\}$  and  $\{p, t, v\}$  are 2-antichains.

Let S be the set of candidates of a call graph G and assume partial order  $(\sqsubseteq)$  on S. D(S) represents an interference graph for a save-free interprocedural register allocation of G and, thus, the candidates of an antichain in D(S) can be assigned the same register. A k-antichain in D(S) is a set of candidates that can be allocated using at most k registers in G.

Assume each register candidate  $c_j \in S$  has a positive integer weighting,  $w_j$ . Let  $(\sqsubseteq)$  be a partial order on S. If  $w_j$  is the benefit of allocating a register to candidate  $c_j$ , then a maximum weight k-antichain in S corresponds to a k-register save-free interprocedural register allocation whose elements sum to the maximum benefit; that is, a save-free minimum cost interprocedural register allocation using at most k registers.

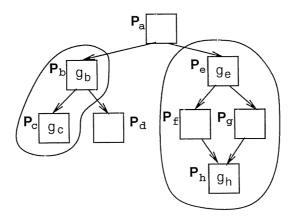

In Figure 4.2(c), assume k=2 antichains. Among the possible allocations of candidates to antichains, the choice with the greatest benefit allocates candidate m to an antichain  $(A_2)$ , and candidates q and t to an antichain  $(A_1)$ . Each antichain maps to an arbitrary, but different register. In Figure 4.2(a), m is assigned register  $r_2$ , and q and t are assigned register  $r_1$ . Since candidates p and p are not allocated registers, an intraprocedural register allocator will spill registers as necessary in procedures p and p to generate a valid register allocation.

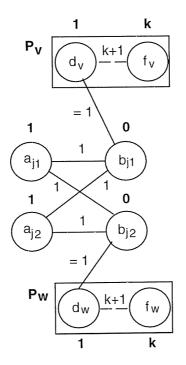

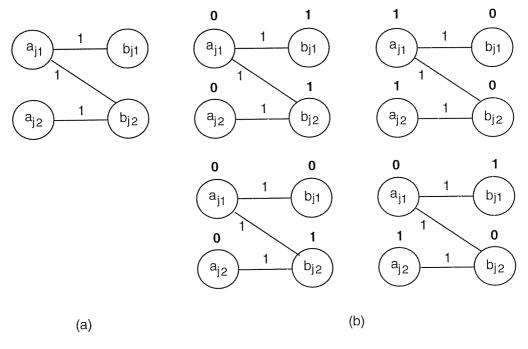

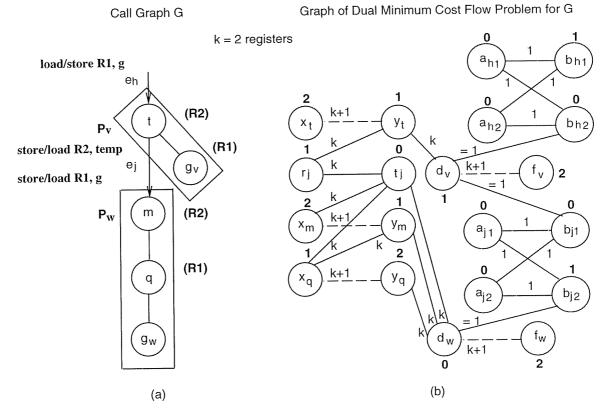

#### 4.1.4 Finding a maximum weight k-antichain sequence