**Tetra: Evaluation of Serial Program Performance on Fine-Grain Parallel Processors**

Todd M. Austin Gurindar S. Sohi

Technical Report #1162

July 1993

# Tetra: Evaluation of Serial Program Performance on Fine-Grain Parallel Processors \*

Todd M. Austin Gurindar S. Sohi

Computer Sciences Department University of Wisconsin-Madison 1210 W. Dayton Street Madison, WI 53706 {austin; sohi}@cs.wisc.edu

July 11, 1993

#### Abstract

Tetra is a tool for evaluating serial program performance under the resource and control constraints of fine-grain parallel processors. Tetra's primary advantage to the architect is its ability to quickly generate performance metrics for yet to be designed architectures. All the user needs to specify is the capabilities of the architecture (e.g., number of functional units, issue model, etc.), rather than its implementation.

Tetra first extracts a canonical form of the program from a serial instruction trace. It then applies control and resource constraint scheduling to produce an execution graph. The control and resource constraint scheduling is directed by a processor model specification supplied to the program. Once scheduled, Tetra provides a number of ways to analyze the program's performance under the specified processor model. These include parallelism profiles, storage demand profiles, data sharing distributions, data lifetime analysis, and control distance (branch, loop, and call stack) distributions.

In this report, we present the extraction, scheduling, and analysis methodologies used by *Tetra*. We detail their implementation and discuss a number of performance optimizations used. The appendix includes the user's documentation for *Tetra*.

<sup>\*© 1993</sup> by Todd M. Austin and Gurindar S. Sohi. This work was supported by a grant from the National Science Foundation (grant CCR-8919635).

## 1 Introduction

A quantitative analysis of program execution is essential to the computer architecture design process. With the current trend in architecture of enhancing the performance of uniprocessors by exploiting fine-grain parallelism, first-order metrics of program execution, such as operation frequencies, are not sufficient; characterizing the exact nature of dependencies between operations is essential.

To date, most processors have either executed instructions sequentially, or have overlapped the execution of a few instructions from a sequential instruction stream (via pipelining). For such processors, the relevant characteristics of dynamic program execution included operation frequencies, branch prediction accuracies, latencies of memory operations in cache-based memory systems, amongst others. The continuing trend in processor architecture is to boost the performance (of a single processor) by overlapping the execution of more and more operations, using fine-grain parallel processing models such as multiscalar, VLIW, superscalar, decoupled, systolic, or dataflow (in a complete or a restricted fashion). To aid the design of such processors, simple first-order metrics of the dynamic execution, such as operation frequencies and operation latencies, are not sufficient by themselves. What is needed is a thorough understanding of how the operations of a program interact, *i.e.*, what is the nature of dependencies between operations in the dynamic execution graph, how these are impacted by the compiler and processor model, and how they impact performance. To this end, we employ dynamic dependence analysis.

Dynamic dependence analysis uses a canonical graph representation of program execution called the dynamic dependence graph (DDG). The nodes of this graph represent operations executed, and the edges in the graph represent dependencies between operations. To perform dynamic dependence analysis, we first extract the DDG from a serial program, and then re-schedule it based on the control and resource constraints of an abstract compiler and processor model. We then analyze the resulting execution graph to see the impact of the execution model on the program's performance. By iterating through this process, we can begin to more effectively explore the trade-offs involved in the design of processors that aggressively exploit fine-grain serial program parallelism.

The primary advantage of dynamic dependence analysis over other program evaluation techniques (e.g., function simulation, timing simulation, or prototyping) is its ability to quickly generate performance metrics for yet to be designed architectures. The actual implementation of the compiler or processor need not be known; all that must be specified to perform analysis is the *capabilities* of the model.

In this report, we present the extraction, scheduling, and analysis methodologies used in our dynamic dependence analyzer, *Tetra*. In Section 2 we introduce the notion of the dynamic dependence graph and discuss the various dependencies that exist in program executions. We show how DDGs can be extracted from serial traces, and then bound to a particular execution model via control and resource scheduling. A number of performance metrics that can be obtained from scheduled DDGs are described. In Section 3 we present algorithms for extracting, scheduling, and analyzing serial program DDGs. We also explore the time and storage complexities of the presented algorithms and previous work is cited. In Section 4, the implementation of *Tetra* is discussed and we detail a number of successful performance optimizations that were applied. Finally, we summarize the report in Section 5.

## 2 Overview

The primary structure that is constructed, manipulated, and analyzed is the dynamic dependence graph (DDG). It is a partially ordered, directed, acyclic graph representing the execution of a program for a particular input. The executed operations comprise the nodes the graph and the dependencies realized during the execution form the edges of the graph.

While a particular operation in the DDG corresponds to an single instruction in the program's executable, we will not use the terms operation and instruction interchangeably. There are two reasons for this. First, because the DDG captures a complete execution of a program, there will be a one-to-many mapping between the instructions in the program's executable and the operations in the DDG. For example, repeated execution of a loop will see the loop instructions represented as many times in the DDG as the number of iterations executed in the program's execution. Thus, an operation is actually an instance of a particular instruction. Second, some instructions do not create values, and thus will not find themselves in the DDG. Examples of these instructions include unconditional branches, and NOPs.

These instructions are more so artifacts of the particular architecture the analyzed program was compiled for; we leave them out of the actual DDG.

The edges in the DDG force a specific order on the execution of dependent operations – forming the complete DDG into a weak ordering of the program's required operations. Some of these program dependencies are inherent to the execution of the program and cannot be removed without changing the algorithms used in the program, others can be removed, but usually not without costs in storage and possibly execution speed. We classify program dependencies into three categories: data, control, and resource.

Data Dependencies: Two operations share a data dependency if one operation creates a value that is used by the other (also called a Read-After-Write, RAW, or flow dependency). This dependency forces an order upon operations such that source values are created before they are used in subsequent operations. Data dependencies can only be removed by changing the algorithms used in the program and/or with compiler transformations that rewrite the code. Examples of algorithmic changes include the use of parallel algorithms (e.g., parallel reduction) instead of sequential algorithms (e.g., serial summation). Examples of compiler transformations include loop unrolling, invariant loop code motion, loop interchange, and strength reduction. A DDG which contains only data dependencies, and thus is not constrained by any control or resource limitations, is called a dynamic data flow graph. Under some execution models, extra ambiguous data dependencies may be inserted into the DDG. Ambiguous data dependencies occur when static memory disambiguation, performed in the compiler, cannot determine if a memory read and write access (e.g., pointer dereferences) do or do not access the same memory, hence a conservative assumption must be made that they do, and an ordering must be enforced during compilation such that the write precedes the read instruction. In the actual execution, the same ordering will result unless the hardware has support for speculative loads (such as in the multiscalar processor [FS92]).

Control Dependencies: Control dependencies are introduced by conditional branches encountered during the execution of a program. Until the branch's predicate has been resolved, it is not known which instructions will be executed after the branch, thus all subsequent instructions share a control dependency with the conditional branch. This view of control dependence is actually overrestrictive, since it has been shown [FOW87] that by applying control dependence analysis, it is possible to either remove some control dependencies or re-attribute them to earlier executed instructions. If an instruction in the control flow graph post-dominates a conditional branch, that instruction need not share a control dependence with the conditional branch, since any path taken after the conditional branch, will always execute the post-dominating instruction. The instruction will instead be control dependent on an earlier executed predicate or with nothing (i.e., the instruction's execution is invariant with respect to any decisions made in the program. We will utilize control dependence analysis in Section 3 to design less restrictive issue models. In either case, control dependencies can be removed via speculative execution. If a processor correctly guesses the outcome of a branch, execution can proceed as if the control dependence never existed. Of course, when using speculative execution, the effectiveness of a processor's ability to remove control dependencies is a function of the program, its execution, the branch prediction algorithm, and the processor's ability to "back out" of its mis-predicted paths.

Resource Dependencies: Resource dependencies (sometimes called structural hazards) occur when operations must delay because some required physical resource has become exhausted. Examples of limited processor resources include functional units and physical storage. It is always possible to remove resource dependencies by supplying more of the critical resource.

A very important resource dependency to consider is the storage dependency. Storage dependencies occur when parallel operations compete for a single physical storage location. Storage dependencies require that a computation be delayed until the storage location for the result is no longer required by any previous computation. These dependencies are often further classified into Write-After-Read dependencies (also called anti-dependencies or WAR hazards) and Write-After-Write dependencies (also called output-dependencies or WAW hazards). Since many different data values can reside in a single storage location over the lifetime of a program, synchronization is required to ensure a computation is accessing the correct value for that storage location. Violation of a storage dependency would result in the access of an uninitialized storage location, or another data value

stored in the same storage location. Storage dependencies can always be removed by renaming. This technique (applicable in the hardware or the compiler) assigns a new physical storage location to each value created, making it possible for values destined for the same logical storage location to have overlapping lifetimes. If all values created are assigned to different locations, the program has the property of single-assignment; that is, a location is assigned to at most once. Of course this is wasteful to actually implement, as many values will have non-overlapping lifetimes, thus most renaming implementations will determine when a value is not longer needed thereby allowing its physical storage to be reclaimed.

#### 2.1 Extraction

The DDG representation of program execution lends itself well to parallelism studies. It lacks the total order of execution found in the serial stream; all that remains is the weakest partial order that will successfully perform the computation required by the algorithms used. If a machine were constructed to optimally execute the DDG, its performance would represent an upper bound on the performance attainable for the program. This claim can be made largely independent of the compilation strategy of the program, since the DDG does not contain control or resource dependencies. While the compiler can change some data dependencies, these changes are typically local in nature. <sup>1</sup> To make any substantial impact on the form of the DDG would require changing the algorithms used in the program. Since compilers cannot generally perform these changes, we say that the DDG approaches a canonical form of a program. Later, we will re-map this canonical form to a processor model that we wish to study, and reveal its impact on the program's performance.<sup>2</sup>

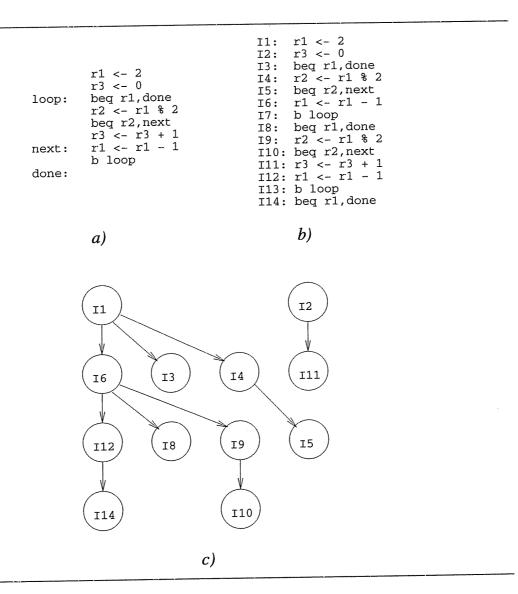

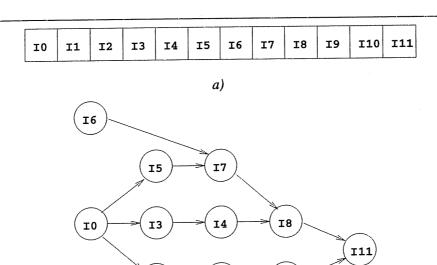

Figure 1 shows a simple program fragment, its execution trace, and the resulting DDG. Note how the loop body instructions in the original program create many instances of operations in the trace and DDG. This DDG only contains data dependencies (shown as solid arrows). In fact, we will only represent the data dependencies in the DDG; the control and resource dependencies will be accounted for when we bind the DDG to a processor model, via control and resource scheduling.

## 2.2 Scheduling

The process of scheduling operations binds them to a *level* in the execution graph. This binding is directed by an execution model specification. In the DDG of Figure 1(c) there are four levels, each one is a horizontal slice of the DDG. The scheduled DDG can be thought of as sequence of parallel instructions that would issue level-by-level in an abstract processor. In Figure 1(c), the DDG is scheduled for a processor model with no control or resource limitations, *i.e.*, an operation can execute as soon as its inputs are available. For this "oracle" processor, operations I1 and I2 would execute in the first cycle, I3, I4, I6, and I11 in the second cycle, and so on.

There are two phases to scheduling a DDG: first, control scheduling, then resource scheduling.

In the first phase, control scheduling, we determine at what level the operation is first issued. The resulting schedule depends on the compiler and processor issue model as well as the control structure of the program. Two control scheduling models are explored in this work, control flow graph (CFG) scheduling, and control dependence graph (CDG) scheduling. The first model, CFG scheduling, is the traditional issue model where instruction issue is based on control dependencies realized on a traversal of the control flow graph of the program. The second model, CDG scheduling, uses the less restrictive control dependence graph [FOW87]. Both scheduling algorithms are described in Section 3.4.

In the second phase of scheduling, resource scheduling, the issued operations are allocated to processor resources using a scheduling heuristic. Two processor resources must be allocated before an instruction can be executed – functional unit and storage resources. Functional units are allocated just long enough

<sup>&</sup>lt;sup>1</sup>Some program level transformations, such as recurrence breaking and induction variable expansion, can have a major impact on the data dependencies of loop intensive programs. Still these changes are always quite regular, and can be easily simulated during DDG extraction – algorithmic changes, for instance, identifying and transforming a serial FFT to parallel FFT, are not yet attempted by compilers and will likely never have widespread applicability.

<sup>&</sup>lt;sup>2</sup>In this respect, the compiler is very relevant, because it has significant control over how control and resource dependencies will manifest. Hence we want to remind the reader that an execution model includes both the hardware and the compiler techniques applied.

Figure 1: Sample program a), execution trace b), and resulting DDG c). The solid lines in figure c represent true data dependencies, and the node labels correspond to an instruction instance in figure b). beq <reg>,<label> branches to <label> if the value in register <reg> is zero, otherwise, it falls through to the next instruction. The "%" operator computes the remainder of an integer divide.

to compute the result value which is then stored in the allocated physical storage (either register or memory). The physical storage is reserved for an indeterminate amount of time. We could extend the resource scheduling to include other processor resources, such as result buses, functional unit input buses, or instruction window slots (as in [AS92]); the methodologies described here would apply to these cases as well.

We study both unconstrained and constrained resource scheduling techniques – all of which are detailed in Section 3. The first, topological sorting, is an optimal, resource unconstrained scheduling technique. We define an optimal schedule to be one in which the given supply of resources produces the shortest length schedule. Unfortunately, generating an optimal schedule of a DAG in the presence of resource limitations is an NP-complete problem for even very small resource supplies [LK78, GGJ78, GJ79]. Thus no known algorithm can do the task is less than exponential time (exponential with respect to the size of the trace being analyzed!) When resources are limited, a scheduling heuristic must be applied and the resulting schedule will nearly always be sub-optimal.

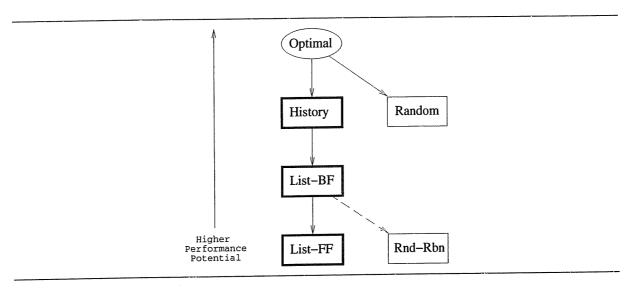

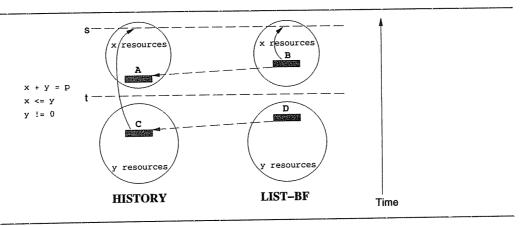

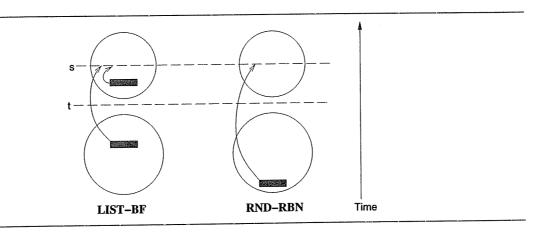

We propose five resource constrained scheduling heuristics: history schedule (HISTORY), list schedule—best fit (LIST-BF), list schedule—first fit (LIST-FF), round robin (RND-RBN), and random (RANDOM). The heuristics were selected for study because they exhibit varying degrees of storage and space complexity during execution, and in return, provide equally varying degrees of performance with respect to an optimal schedule. In Section 3.5 we describe each of the heuristics as well as show their relative performance with respect to each other. Once scheduled, we can derive a number of interesting metrics from the execution graph.

#### 2.3 Analysis

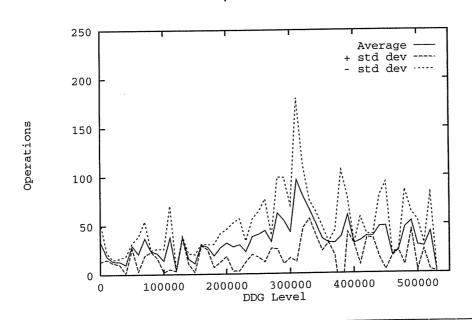

DDG metrics fall into two categories: resource demand profiles and value metrics. The first, resource demand profiles, show the quantitative demand for a particular resource as a function of the level in the scheduled DDG. The parallelism profile is a resource demand profile showing the number of functional units used in each level of the DDG. Figure 2 shows the parallelism profile of the GNU "gcc" compiler compiling its own source file "cexp.c".

The available parallelism is defined as the arithmetic average number of operations per level in the parallelism profile and can be viewed as the speedup that could be attained by an abstract machine capable of extracting and executing the DDG from the program. The length of the parallelism profile is the critical path length of the execution. This length is identical to the height of the scheduled DDG, and it gives the minimum number of steps required to evaluate the operations in the scheduled DDG. In Figure 1(c), the available parallelism is  $\frac{2+4+4+2}{4} = 3$ , and the critical path length is 4. In Figure 2 the available parallelism is 42 operations/level and the critical path length is approximately 550,000 levels.

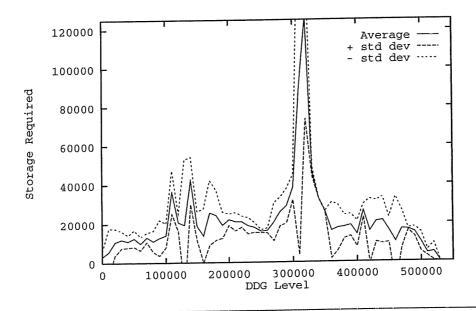

Values used by parallel operations must reside in physical storage. The physical storage demand profile (or waiting token profile) shows the amount of storage required at each level of the DDG. This profile is a function of both the parallelism in the program, and the lifetime of the values: as each increases, so will the physical storage requirements. This metric is useful in determining the amount, and type, of temporary storage required to realize the levels of parallelism shown in the parallelism profile. In Figure 3, the aggregate, compacted storage demand profile for GCC is shown. Tetra can also break the storage down by register and memory storage demand. It can do this either by the storage class of the original reference (i.e., register or memory), or by the likelihood that a compiler would allocate the object to a register or memory location. In the latter case, register locations are reserved for high frequency and short lived values, while memory is reserved for all other values. This method recognizes that storage allocation in a compiler is inextricably bound to the architecture upon which the code is intended to run, thus the further the host architecture departs from the abstract architecture, the less likely register allocation will be the same. Using the frequency/lifetime based breakdown, it becomes possible for the architecture designer to get a handle on how much storage will be needed in each level of the memory hierarchy to achieve a given level of program performance.

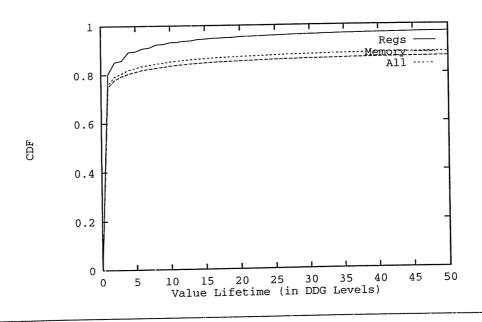

Value metrics examine characteristics which reveal of how values are produced, manipulated, and consumed during a program's execution. For example, the value lifetime distribution shows the distribution of value extents. The extent of a value is measured as a distance with respect to levels of the DDG. Figure 4 shows the value lifetime distribution of the sample GCC execution.

The degree of sharing distribution is a frequency distribution indicating how many other nodes in the

Figure 2: Example Parallelism Profile. GNU "gcc" compiling "cexp.c". This parallelism profile has been compacted; the top dashed line is the average plus the standard deviation, the bottom dashed line is the average minus the standard deviation, and the middle solid line is the average parallelism over 10,000 levels.

Figure 3: Example Aggregate Storage Demand Profile. GNU "gcc" compiling "cexp.c". This parallelism profile has been compacted; the top dashed line is the average plus the standard deviation, the bottom dashed line is the average minus the standard deviation, and the middle solid line is the average parallelism over 10,000 levels.

Figure 4: Example Value Lifetime Distribution. GNU "gcc" compiling "cexp.c". This graph is a cumulative distribution function showing the lifetime, in DDG levels, of register and memory values (as allocated by the host compiler).

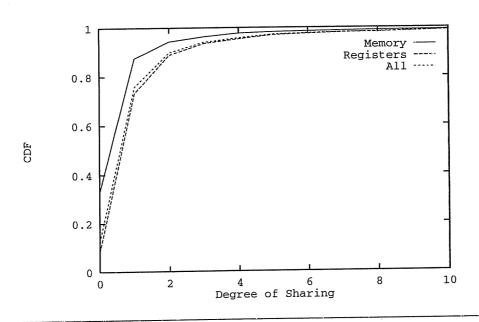

DDG used generated values. Such a distribution is important not only for a possible dataflow realization of our abstract execution engine (by indicating how many operations can be "fired" when a token is created in an explicit token store machine, for example), but also for more conventional multiprocessor execution of the program. In a multiprocessor, different processors are responsible for execution of different parts of a (suitably constrained) DDG of a program. By measuring how much data flows from the nodes in one subgraph to another (albeit in a very constrained form of the DDG that matches the processor execution model), we can measure the degree of data sharing amongst the processors, for example. These results would be directly applicable to the design of directory based cache coherency schemes. Figure 5 shows the degree of sharing distribution for the sample GCC execution.

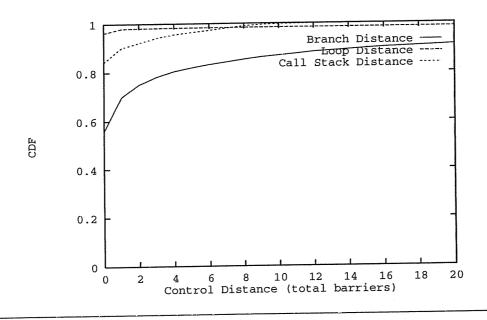

Dependency distance distributions show the "control distance" between the producer of a value and a consumer. By examining this, it is possible to gauge how well a real architecture would have to speculate past program control structures to realize a given level of parallelism. Control distances can be measures in terms of any program control construct. In this work, we measure distances on the control flow graph, branch distance, distances between iterations of a loop, loop distance, and distances on the execution call stack, call stack distance. Figure 6 shows the branch, loop, and call distance for the sample run of GCC.

The branch distance reveals the level of branch speculation required by a simple, single window of execution processor to achieve the same level of performance as the abstract target model. The loop distance metric displays the balance between loop parallelism and functional (non-loop) parallelism. This is a good indicator of how well the abstract processing model will have to support either type of parallelism, either in the compiler or the processor implementation. And the call distance indicates how parallelism is spread across separate function bodies, and thus reveals how effectively the abstract architecture will have to either support dynamic execution of multiple procedures or static inlining.

Having introduced the concept of the dynamic dependence graph and described the process of DDG analysis, namely, extraction, scheduling, and analysis – we now dive head long into the details of how these processes can be implemented.

# 3 DDG Extraction, Scheduling, and Analysis Methodologies

Designing an algorithm to extract, schedule, and analyze a serial trace, of virtually unlimited length, is a challenging task. An interesting, representative trace can easily become larger than what could be

Figure 5: Example Degree of Sharing Distribution. GNU "gcc" compiling "cexp.c". This graph is a cumulative probability distribution showing the total sharing of values by register and memory values (as allocated by the host compiler).

Figure 6: Example Control Distance Distribution. GNU "gcc" compiling "cexp.c". This graph is a cumulative probability distribution showing the total branch, loop, and call distance distributions of all edges in the DDG.

stored in a conventional computer memory. The resulting DDG, if annotated for analysis, can become even larger. The algorithms presented in this section have one dominating goal: limit storage usage at all costs, even if the time complexity of the algorithm must be increased. Before we describe our methodology, we briefly discuss the previous work in this area.

#### 3.1 Previous Work

There has been a plethora of work which measured the average parallelism in a (sequential) instruction stream for a particular hardware configuration [BYP+91, NF84, SJH89, TF70, Wal91]. These studies typically find the length of the critical path through the computation, and compute the average parallelism as the total number of instructions divided by the number of cycles of execution. (Some also measure the resource load to determine the maximum number of resources required). These studies typically evaluate how the average parallelism changes under various constraints such as register renaming, various branch prediction strategies, memory disambiguation strategies, changes in operation latencies, instruction window sizes, resource constraints, etc. Changes in a parameter result in changes to the critical path length (and resource demand), and consequently to the average (and maximum) parallelism. Because they are interested in only a single measure, namely the average or available parallelism, and not in other aspects of the DDG, they do not need to construct the entire DDG, or even parts of it.

An early work measuring total available parallelism is that of Kuck, et al. [Kea74] They statically analyzed (by hand) program dependencies in FORTRAN programs, and the resulting available parallelism was estimated from the analyzed code fragments. Kumar [Kum88] presented the first work that gathered exact parallelism profiles in serial FORTRAN programs. Kumar extracted parallelism profiles by rewriting FORTRAN programs (with COMET) such that the profile was generated during the execution of the program. Although the method would lend itself to any imperative language, it was only applied to FORTRAN. The operations in the DDG were FORTRAN statements which were assumed to execute in one unit of time. Our method of extracting DDGs from serial traces is quite different than Kumar's. While Kumar placed FORTRAN statements into the DDG, we instead place machine instructions into the DDG. This allows more precise control over the relative time taken for operations in the DDG, and finer-grain parallelism (such as that found within FORTRAN statements) will show up in our results. Moreover, since our technique builds the DDG from a serial execution trace, without modifications to the source program, it can be applied to any language, compiled or interpreted. Kumar implemented a control model similar to our CDG issue model. Specifically, he did not allow any FORTRAN statement to execute until all surrounding predicates had completed evaluation. Lam and Wilson's work [LW92] has shown this assumption to be overly restrictive, as the use of speculation can allow many operations to execute prior to the resolution of their surrounding predicates. While we too look at the effects of the control model on available parallelism, we also look at control barrier from another viewpoint. By measuring the control distance of dependencies, we can then show for a given level of parallelism, how effective speculation must be to expose that parallelism.

MaxPar [CSY90] is very similar to Kumar's COMET in that it also rewrites programs. Where Kumar's COMET was limited to scheduling program statements, MaxPar has the ability to schedule at the granularity of operation-level, statement-level, loop-level, or subprogram-level. It can also limit computing resources available during analysis. They implemented four list scheduling algorithms: near-optimal (identical to LIST-BF), earliest available (identical to LIST-FF), circular (identical to RND-RBN), and random (identical to RANDOM). We expand on their work by proposing a new, more powerful scheduling heuristic, HISTORY. We also extend their heuristics to support scheduling of resource with non-deterministic latency, which allows us to examine the effects of limited storage resources.

A number of papers from the dataflow literature have included examples of DDG analysis [CA88, ACM88, AN89, Nik90]. For example, Culler and Arvind [CA88] provide detailed parallelism profiles and waiting token (or storage demand) profiles for some dataflow programs. Their dataflow processor and language environment lends itself well to DDG analysis. Instrumenting the dataflow processor's execution is sufficient to generate the parallelism profiles and critical path. Yet their environment lacks storage and most control dependencies, so their results will not include the effects they have on available parallelism. Therefore, it is not clear how their results would extend to programs written in imperative languages such as C or FORTRAN, and also how they could be applied to processors that have more restricted computation models. We have found in our research that our results agree with the conclusions of [ACM88] and [Kum88] that ordinary programs and algorithms, not intended to execute in parallel

environments, do indeed have a significant amount of fine-grain parallelism.

Larus performed detailed studies of loop level parallelism for a number of the SPEC benchmarks [Lar91]. Because the analysis was intended primarily for directing the development and application of compilers capable of parallelizing loops, the analysis was limited to intra-loop parallelism of each lexically top level loop. Our analysis examines parallelism in a more global view, thus allowing inter-loop parallelism to also be analyzed. Still, for a number of programs, our results are quantitatively very close to Larus', supporting that for many programs, much of the parallelism is intra-loop parallelism.

Mahlke et al. [MWC<sup>+</sup>91] examined the effects of compiler optimizations on serial program parallelism. They looked specifically at three classes of program optimization: classical, superscalar, and multiprocessor. The superscalar optimizations encompass their superblock global trace scheduling techniques, loop unrolling and peeling, and induction variable expansion. The multiprocessor compiler optimizations were primarily memory renaming (simulated in the analysis) and data migration (faster loads). They found that classical and superscalar optimizations did expose more parallelism, especially in small instruction windows. And the multiprocessor optimizations were most effective for very large instruction windows. When running on an "oracle" machine (i.e., no resource or control constraints, perfect memory disambiguation, and unlimited renaming), they found that program transformations exposed little more intrinsic parallelism. This supports our thesis that the DDG of a program is, for the most part, a canonical form of a program.

Wilson and Lam [LW92] studied the effects of control dependencies on available parallelism. Their primary result showed how combining control dependence analysis, multiple flows of control, and speculative execution could expose a large portion of the total available parallelism found in the unconstrained DDG. Hence, the critical factor in the development of aggressive fine-grain parallel processors will likely not be control dependence resolution, but rather other factors, like data dependence resolution. We extend their work by providing a framework in which both control and resource constraints can be combined.

Theobald, et al. [TGH92] examined the smoothability of serial program parallelism. By constraining the available computational resources (via a HISTORY schedule), they were able explore a program's sensitivity to limited functional unit supplies. We extend their work by evaluating the advantages of more computationally frugal scheduling heuristics as well as showing the limitations in their scheduling heuristic. We also examine the smoothability of the storage demand, and combine both control and resource scheduling.

We extend our earlier work [AS92] in a number of ways. This paper provides a more detailed description of the methodology, and we describe a number of invariants on the algorithm as well as examine its time and storage complexity. We extend our methodology to include construction of control and resource constrained DDGs, and then provide a full treatment of the scheduling heuristics, their complexity, and their limitations. We detail a number of very successful performance optimizations in our implementation of *Tetra*. And our results now include a number of new metrics, including storage demand profiles, value lifetime profiles, and control distance profiles.

# 3.2 Unconstrained DDG Extraction and Analysis

Construction of the unconstrained DDG need only consider the data dependencies realized in the analyzed program's execution. During scheduling, all control dependencies are ignored, and an unlimited supply of functional units and storage are available in any level of the DDG. Later, we will extend the unconstrained DDG methodology to also account for more restrictive issue models and limited physical resources, and we will discuss the many difficulties in their handling. The basic extraction, scheduling, and analysis algorithm is shown in pseudo-code in Figure 7.

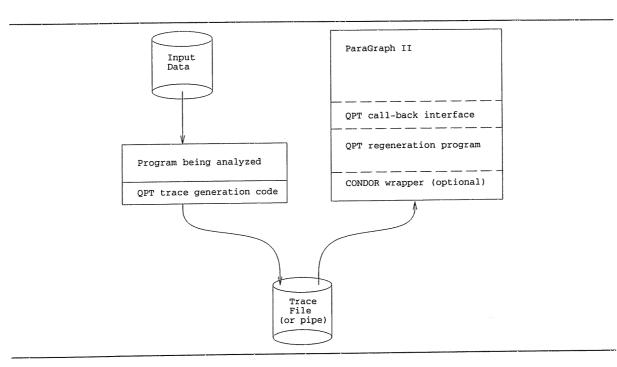

The algorithm iterates across each instruction in the trace stream, in the order of their execution, performing extraction, control and resource scheduling, and analysis in one pass.

The trace instructions are accessed through the argument trace. This variable is a typed stream, and it functions similar to C's standard input stream. The trace stream provides two built in operations: EOF, and NEXT. trace.EOF returns a boolean indicating if there is more information to be read from the trace stream, and inst := trace.NEXT assigns the next instruction from the trace stream into the variable inst. Because the extraction and analysis is performed in one pass of the trace stream, the trace stream can be "piped" directly into the DDG analyzer, thus there is no need to store the entire instruction trace.

```

type

Level: integer;

UniqueID: Address OR RegisterNumber;

Inst: record

pc: Address;

src: set of UniqueID;

dest: UniqueID;

end;

var

baseLevel, deepestLevel: Level;

procedure AnalyzeDDG(trace: STREAM of Inst)

liveWell: MAPPING from UniqueID to Level;

maxPred, value, schedLevel: Level;

inst: Inst;

baseLevel := 0;

deepestLevel := 0;

while (NOT trace.EOF) do

inst := trace.NEXT;

{\bf if} \ (liveWell[inst.dest]. EXISTS) \ {\bf then}

Update Value Metrics (live Well[inst.dest]);\\

endif

if (HasSideEffect(inst)) then

liveWell[inst.dest] := deepestLevel + Latency(inst); \\

baseLevel := schedLevel := deepestLevel;

deepestLevel := deepestLevel + Latency(inst);

else

maxPred := baseLevel;

for all value ∈ inst.src do

if (liveWell[value].EXISTS) then

maxPred := MAX(maxPred, liveWell[value]);

endif

endfor

schedLevel := ControlSchedule (inst, \, maxPred); \\

schedLevel := ResourceSchedule(inst, schedLevel);

liveWell[inst.dest] := schedLevel + Latency(inst);

{\tt deepestLevel} := {\tt MAX}({\tt deepestLevel}, {\tt schedLevel+Latency}({\tt inst}));

UpdateBarriers(inst, schedLevel);

endif

UpdateDemandProfiles(inst, schedLevel);

endwhile

for all value \in liveWell do

UpdateValueMetrics(value);

endfor

endproc

```

Figure 7: Main Loop of DDG Extraction, Scheduling, and Analysis Algorithm.

Figure 8: Unconstrained DDG Control and Resource Scheduling Routines.

An operation's placement in the execution graph is first constrained by its input values, that is, it cannot be placed any earlier than its latest input value. This level is computed in the innermost for loop. The loop iterates across all the inputs to the current instruction, storing the most restrictive input into the variable maxPred. The initial value of maxPred, *i.e.*, the value of the variable baseLevel, forces a lower bound on the placement of operations into the DDG. baseLevel is used primarily in the handling of instructions with unknown side-effect, and in the handling of pre-existing values.

If an instruction has unknown side-effect, e.g., system calls, it is not possible (or directly obvious) to identify what storage was read or written by the instruction. Therefore, the algorithm must either assume that the instruction modified all live values in the program (pessimistic system call assumption), or that it modified nothing (optimistic system call assumption). The conservative assumption is implemented by placing the operation after all levels currently used in the DDG and bounding the placement of future operations to levels later than the operation with unknown side-effect. This placement level, found in the variable deepestLevel, ensures that the operation has access to any value created previously. deepestLevel is updated every time a new level is used that is later than any previous level. The bounding of future operations is implemented by reseting the value of the variable baseLevel. Since all future placements can be no earlier than baseLevel, future instructions are forced to read any values updated by the instruction with unknown side-effect. Later, we will use an identical procedure to realize control dependencies. For optimistic system call assumptions, we simply place the instruction into the topologically earliest level in the DDG, (i.e., at baseLevel).

Pre-existing values reside in the data segment. They are placed there at compile time by the compiler. On some architectures, these pre-existing values can also exist on the stack and in registers at the start of program execution. In any case, the value is placed on first reference, without a creating operation, into the execution graph such that it is available at the earliest defined level of the DDG. This level is stored in the variable baseLevel.

After determining the most restrictive input level (either that of the latest input, or the last system call), the calls to ControlSchedule() and ResourceSchedule() further constrain the placement to include the effects of control and resource dependencies, respectively. Control scheduling is always performed before resource scheduling, since an operation must first be issued before its resource requirements can be determined. UpdateBarriers() is later called to update any control barriers that might have been created by the current instruction. These routines are processor model dependent. We detail the ones implemented by *Tetra* in Section 3.4.

Figure 8 shows the scheduling routines used to schedule a DDG without resource or control constraints. Since there are no control or resource constraints, the routines simply return the passed levels. The resulting execution graph is the topologically sorted [Tar83] DDG. The schedule is optimal with respect to length, and it represents an upper bound on the performance that can be attained for the analyzed program. This schedule is also commonly called the eager evaluation schedule, because an operation is scheduled as soon as it its inputs are ready. This is only one of many possible optimal schedules for the operations; for example, the schedule in Figure 1(c) would still be an optimal schedule if the operation 18 was moved down one level in the schedule.

Once an operation's level in the execution graph is known, we can compute when its result value is available as simply the operation's placement level plus the latency to create the value. The algorithm calls the processor dependent function Latency() to determine the latency of an operation. This latency is equal to the total time required to compute a result, or the total time that the resource must be reserved (as in the case of memory). The level of the newly created value is then inserted into the *live well* under the address (or register specifier) of the destination storage.

The live well acts as an associative memory, allowing the algorithm to find the DDG level of an operation's input values, given a unique value identifier. The algorithm employs a mapping variable instead of an array, since the domain of value identifiers is likely to be large and sparse. The mapping variable, liveWell, supports the built in function map[indexor].EXISTS, which returns a boolean value indicating if there currently exists a mapping from indexor to some value. The assignment map[indexor] := value installs a new value into the mapping variable, deleting the previous value if one exists. In Tetra, the live well is implemented with a hash table.

It is not necessary to assign arbitrary (unique) value identifiers to newly created values. Because values residing in the same storage location will have non-overlapping lifetimes, it is sufficient to use the value's destination register number or memory address as a unique value identifier. The serial semantics of the trace stream will ensure that any reference to an entry in the live well always yields the correct value information. In the presented algorithm, we've assumed that a register number is obviously different than a memory address, if this is not the case, a single bit can be added to distinguish the two, or the registers can be mapped into an unused portion of the memory address space.

The storage requirements of the live well are proportional to the size of the program's active name space. The active name space of a program is the complete set of names (memory addresses and register specifiers) that a program will produce during its execution. Since we cannot ever de-allocate a value record, any touched memory will incur a memory cost. It is reasonable to assume that, if the value records are kept reasonable small, we can analyze nearly any program, since by definition the program's active name space must fit into the memory of the computer that can run the program. We reduce this overhead by trimming the per-value memory requirements in the live well, as well as by reducing the live well overhead. In Section 4 we discuss the implementation of the live well for Tetra. Since the live well is implemented with a hash table, the time complexity for accessing values is O(1).

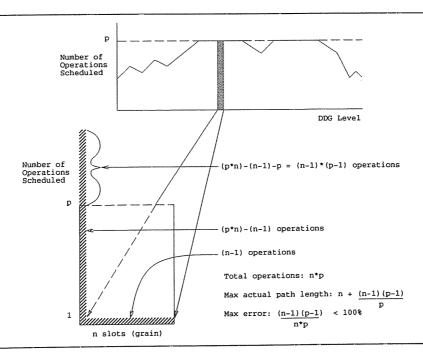

Generation of the resource demand profiles occurs at the call to UpdateDemandProfiles(). At this point, an operation has just been placed into the DDG. By inspecting the instruction, we can determine what resources are used, and update the appropriate profile vector at an index derived from the level of the placed operation. Because the profile's storage size will be on the order of the constructed execution graph's height (critical path length), it may be necessary to increase the granularity of the profile array entries. In other words, instead of saving the resource demand for a single level in an array element, we will save the total resource demand over n levels in an array element (producing a profile of granularity n). Unfortunately, no information other than the average parallelism (or storage demand) can be computed for the range. This is because the samples in the range, *i.e.*, the number of operations placed at each level, are not known until the end of the analysis. Other interesting information, such as the exact shape of the curve, or the maximum, minimum, or variance of the parallelism (or storage demand) is lost. This is usually only a problem for long traces with very little parallelism. We describe, in Section 4, a number of implementation tricks that can help mitigate the profile storage requirements.

Value metric distributions require information be stored with values in the live well. Whenever a value is created or referenced, those variables may have to be updated. For example, when computing the degree of sharing distribution, we keep a counter, initially zero, with the value in the live well, and increment it each time the variable is referenced. When the value becomes dead (at the call to UpdateValueMetrics()), the stored value usage information can then be transferred to the appropriate frequency distribution. It is important to also call UpdateValueMetrics() on all values in the live well upon completion of trace analysis, since all remaining values in the live well have become dead.

The actual mechanics to produce the value metric distributions is generally trivial, so we shall not overextend our welcome with the reader to describe them all here. However, since the implementation of the control distance metrics is significantly more complicated, we offer a complete description of these

<sup>&</sup>lt;sup>3</sup>Later, we will also define a PLatency(), which is the amount of time that the resource must be reserved before another operation can use it – this is useful for building schedules for pipelined resources.

metrics and fully describe their handling in the following section.

## 3.3 Control Distance Analysis

Consider, for sake of illustration, we accepted the task of constructing a machine that could exploit all the available parallelism from a serial program's instruction stream. One major obstacle to accomplishing this task would be devising a mechanism that could effectively overcome the control barriers found between operations producing values, and operations consuming those values. For many values, the control barriers between the producer and consumer will have to be overcome in as little as one cycle of this abstract machine's execution.

Control barriers are program constructs that perturb the normal inline fetch and issue of instructions. We quantify the "difficulty of overcoming" control barriers as the number of barriers that must be resolved (or speculated) between the operation that produces a value, and the operation that consumed that value. Since this path is always represented by an edge in the DDG, we say that a DDG edges has a control distance with respect to the serial trace. By building control distance distributions, we can gauge just how effectively this "abstract" architecture will have to overcome control barriers before it can fully exploit the available parallelism.

We examine three control distances: branch distance, loop distance, and call distance. The branch distance of a DDG edge is defined as the number of conditional branches that must be resolved (or speculated) in the serial trace before the consuming operation can be issued. The loop distance is the number of loop iterations that must be issued before the consuming operations is issued. This is commonly referred to in the literature as a loop carried dependency distance. The call distance is the distance, on the call stack, between the producing operation and the consuming operation.

We need to examine two issues: first, which edges in the DDG are most meaningful to examine, and second, what procedure can we use to measure each type of control distance.

While we can always examine the control distances on all edges, we can gain clearer results by concentrating on only the edges whose control barriers will be the "hardest" to overcome. These edges are the ones on the critical path. Since a value traveling along a critical path edge must be transmitted to the consumer in one "cycle" of our abstract machine, these edges become the most important, and hardest to resolve. Unfortunately, its computationally infeasible to locate the exact set of edges on the critical path – instead we can use a property of the critical path to easily generate a reasonable superset of these edges. All edges on the critical path span exactly one level of the DDG. Thus if we analyze only edges of length one, we can trim away many of the "easier" edges from our metrics. Just how many of these "easy" edges are removed is a function of the program and its execution. We call the length one edges the most restrictive edges.

The simplest control distance to measure is the branch distance. The only state required is a global branch counter. This counter is incremented each time a conditional branch instruction is encountered. The branch counter's current value is then placed into the live well when a value is created. The branch distribution is updated each time another operation uses this value (or each time a length one edge is created from this value, if we are only examining the most restrictive edges). The distance is computed as the current branch counter value, minus the branch counter value stored in the value record.

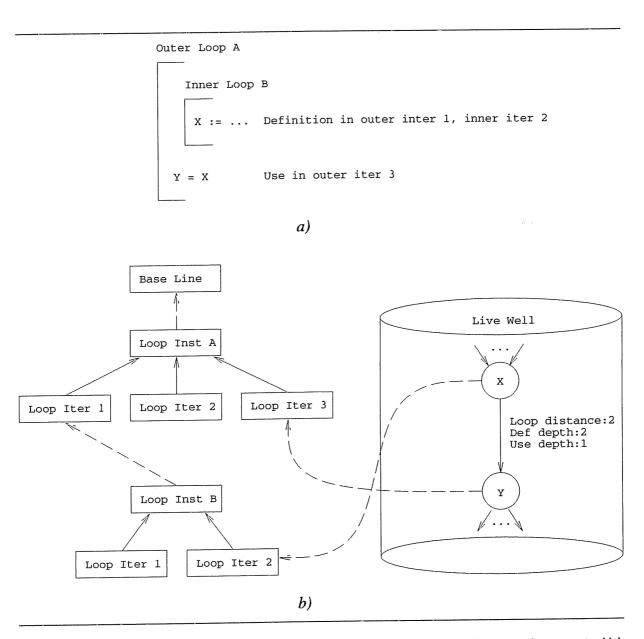

The loop distance of an edge is defined to be the intra-loop iteration distance – it is zero if the definition of a value is not used in the same loop instance. An instance of a loop is one complete invocation of a loop structure in the program's execution. Only loops executed from within another loop may have multiple instances. Figure 9(a) shows a nested loop example.

In the example code of Figure 9, a definition of X is created in the first iteration of loop A while it is executing the second iteration of the nested loop B. This value, in X, is later used in the third iteration of loop A, outside of the scope of loop B. The loop distance, in this example, is on the edge between the operation that creates X and the operation that uses X (as shown in the live well of Figure 9(b)). The loop distance of this edge is two, since the definition of X occurs in the first iteration of loop A, and is used in the third iteration. The instrumentation methodology is complicated by the possibility that a value may be created in a dynamically nested loop, which may complete execution, and thus require that its values be attributed to the surrounding loop. In fact, we will not know which loop to attribute the value to until it is used – the first common loop in the tree of dynamic loop instances is the loop in which the value is defined and used. The intra-loop distance is then computed by subtracting the use iteration,

Figure 9: Nested loop example a), and resulting loop tree b). The brackets in the nested loop example represent a high level language iterative construct. The inner loop (smaller bracket) is lexically nested in the outer loop (larger bracket). During the execution of the nested loop example, the outer loop iterates three times. In the first iteration of the outer loop, the inner loop executes for two iterations, creating a definition of X in the second iteration. The definition of X is later used, outside of the scope of the inner loop, in the third iteration of the outer loop. In the loop tree, the solid lines represent pointers to loop instance records, and the dashed lines are pointers to loop iteration records.

of this common loop, from the creating iteration.

We employ the *loop tree* structure to track the program's dynamic loop instances and iterations in a storage efficient manner. Figure 9(b) shows the live well and loop tree resulting from the code example in Figure 9(a). The loop tree contains three node types: loop instance descriptors, loop iteration descriptors, and the base line node.

A loop instance descriptor is created for each invocation of a loop in the program. A loop is defined as any subgraph of the CFG in which one basic block, the loop header, dominates all basic blocks up to and including one or more blocks that contain a back edge to the loop header [ASU86]. This definition suffices unless the CFG contains irreducible loops.<sup>4</sup> While irreducible loops can be created in most languages, they are generally not found in practice.<sup>5</sup> In our DDG analyses, we annotate the instruction trace with loop start, end, and continue "signals". The natural loop analysis is performed prior to executing the DDG analyzer. When a "loop start" signal is encountered, a loop instance descriptor is created and linked to the current loop invocation. When a "loop end" signal is encountered, the current loop invocation is reset to the parent of the loop instance that is ending. The loop instance descriptor contains a pointer to the creating loop iteration, a unique brand (used later in a tree search optimization), a tree depth variable (used for tree searches), and a reference count.

All loop tree descriptors contain a reference count indicating how many other descriptors and value records point to it. Since a program can create virtually an unlimited number of loop instances, with even more iterations, it is imperative that loop tree storage be released as soon as it is known to be unreferenced by any value in the live well. We employ a reference counting reclaimation scheme because the extent of the values created in the program, and thus referencing the loop instance records, does not follow any program structure; as a result, a loop descriptor can become free at any time during analysis. Using reference counts, we just reclaim the loop tree storage when its reference count becomes zero.

The *loop iteration descriptors* are linked to the loop instance in which they are contained. Each occurrence of "loop start" or "loop continue" signals cause the creation of a loop iteration descriptors in the loop tree. The loop iteration descriptors contain a pointer to the loop instance that created this iteration, an iteration number, and also a reference count.

Although the loop instance descriptor and loop iteration descriptors could be coalesced, they are kept separate to reduce the size of the loop tree. Because the information in the loop instance descriptor is larger than the pointer used to reference to it, less memory is used.

Whenever a value is referenced, an edge is created in the DDG. The control distance of the edge is computed by walking the loop tree, starting at the iteration descriptor of the use and definition of the value, until a common (loop instance) ancestor is found. The loop distance is then computed by subtracting the iteration number of the definition from the iteration number of the use. If the base line node is reached, the definition and use of the value are not contained within any common loop, and the loop distance is zero. We use two optimizations to speed up the tree walk: depth counts, and branding.

Each loop instance descriptor contains its depth with respect to the base line node. When walking the tree, to find a common ancestor, we can immediately determine which reference to walk up the tree first, *i.e.*, the deeper reference.

The top level loops in the program form a forest of loop trees, since the base line node is not a real loop. Each top level loop tree is assigned a unique numeric "brand" which is then stored in the loop instance descriptors. Since a use and definition must reside in the same top level loop tree, we can quickly determine the loop distance to be zero if the create and use loop instance descriptors have different brands.

The storage required to store the loop tree is bounded to a value proportional to the size of the program's active name space. Even though the number of created loop instance and iteration descriptors is unbounded, our reference counting scheme ensures that there can be no more active loop iteration descriptors than the number of values in the live well. Each value in the live well can point to (and thus increment the reference count of) at most one loop iteration descriptor, and the loop iteration descriptors can (in the worse case) each point to one at most one loop instance descriptor. Since the size of the live

<sup>&</sup>lt;sup>4</sup>One "loose" definition of an irreducible loop is: a loop which does not contain jumps into the middle from outside of the loop; a reducible loop can only have entries at the loop header. See [ASU86] for a formal definition.

<sup>&</sup>lt;sup>5</sup>The only SPEC benchmark containing irreducible loops is *spice2g6*. The problem was rectified by rewriting the offending routine in a more structured manner.

well is proportional to the size of the active name space, so too will the loop tree in the worse case. In practice, values in the live well will often point to the same iteration descriptors, thus the actual storage requirements will be much less.

The procedure by which loop distances are computed can be easily adapted to measure "call distance". Recall, that a call distance is the distance, on the call stack, between a definition of a value and its use. The call tree is similar to the loop tree; except only the instance descriptors are required since procedures do not iterate. To compute the call distance, locate the first common ancestor on the call tree. This is the procedure in which the definition of the value occurred (although it may have been in a nested procedure instance). The depth of the value use minus the depth of the common ancestor node is the call distance. The branding optimization does not apply to this computation because the call tree does not form a forest of trees.

The storage required to store the call tree is also bounded to a value proportional to the size of the active name space (for the same reason that the loop tree). And in practice, it is significantly smaller than the loop tree.

Having presented the methodologies used to perform unconstrained DDG extraction, scheduling, and analysis, we can now extend the described methodology to also support more restrictive issue models and limited physical resources. The following sections also discuss the many difficulties in their handling.

### 3.4 Control Scheduling

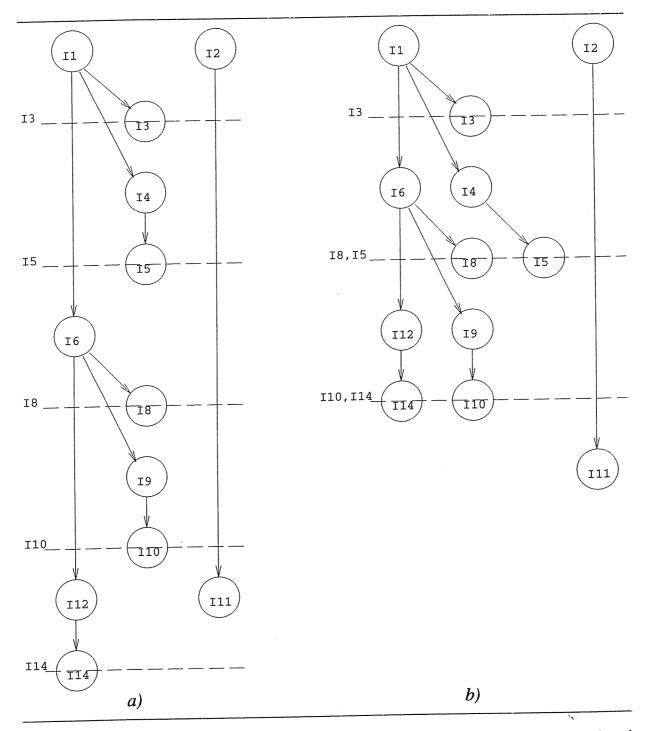

Tetra can explore the impact of two processor issue models, one based on the control flow graph (CFG), and one based on the control dependence graph (CDG). The first model, CFG issue, is the traditional issue model. Operations may execute as soon a the most recent (in trace order) branch instruction is resolved. The model also employs a speculation mechanism describing whether or not a particular edge in the CFG is speculated correctly, and thus does not constrain the DDG. A mis-speculated edge inserts a control barrier into the DDG such that no later instructions can be placed earlier in the DDG than the mis-speculated branch instruction. Figure 10(a) shows the DDG of Figure 1(c) after CFG control scheduling. In this example, no speculation was employed, so operations 13, 15, 18, 110, and 114 all insert control barriers into the schedule.

The CFG control scheduling algorithm is shown in Figure 11. The algorithm implements the functions ControlSchedule() and UpdateBarriers(), which are called from the main scheduler loop after determining the unconstrained placement of the operation (see Figure 7). ControlSchedule() simply constrains the operation such that it is later than the level of the last control barrier (stored in the variable lastBarrier). UpdateBarriers() needs to update lastBarrier if the instruction passed to it creates a control barrier. UpdateBarriers() is called after the passed instruction has been control and resource scheduled. The procedure first checks if the instruction is a conditional branch (using CondBranch()), and if so, attempts to speculate past it in the call to Speculate(). Speculate() is a processor model dependent routine that implements the speculation mechanism used, e.g., two level adaptive, n-bit counter, static predictor, n-percent correct, etc. If the speculation fails, a control barrier is inserted into the execution graph by updating the constraint variable lastBarrier. It is reset to the level of the mis-predicted conditional branch (in schedLevel). All future operations will be placed after the mis-predicted conditional branch.

The second control scheduling model, CDG scheduling, issues operations based on the more relaxed control model as specified by the control dependence graph. (See [FOW87] or [CFR+91] for a complete description and formal definition.) CDG scheduling allows operations to issued as soon as their surrounding predicate is resolved (or correctly speculated). An instruction is said to be control dependent upon its surrounding predicate, because it is this predicate that ultimately determines if the instruction is issued. In Figure 10(b), the DDG of Figure 1(c) has been control scheduled based on the control dependence graph rather than the control flow graph (as is shown in Figure 10(a)). Note how the operations I6 and I12 are "elevated" in the scheduled DDG to just after their surrounding predicate, that is, operations I3 and I8, respectively. Contrast this to the CFG scheduling case in Figure 10(a), where I6 and I12 are control dependent on I5 and I10, respectively. This mobility is allowed because the operations I6 and I12 post-dominate the branches I5 and I10, and thus their issue is invariant of any decisions that they make.

The CDG model actually appears to be multi-threaded with respect to the CFG model because the

Figure 10: CFG control constrained schedule a), and CDG control constrained schedule b). All schedules are performed on the DDG of Figure 1(c). The solid lines represent flow dependencies, and the node labels correspond to an instruction instance in Figure 1(b). The first control constrained schedule, a), uses a control flow graph (CFG) scheduling model with no speculation. The second control constrained schedule, b), uses a control dependence graph (CDG) scheduling model with no speculation. The control barriers produced by the branch instructions are shown as horizontal dashed lines and are labeled with the instruction (or instructions) creating the control barrier.

```

var

lastBarrier: Level;

function ControlSchedule(inst: Inst, earliest: Level): Level;

begin

ControlSchedule := MAX(earliest, lastBarrier);

endfunc

procedure UpdateBarriers(inst: Inst, schedLevel: Level);

begin

if CondBranch(inst) then

if NOT Speculate(inst) then

lastBarrier := schedLevel;

endif

endif

endproc

```

Figure 11: CFG Control Scheduling Algorithm.

program can now be simultaneously executing in multiple, non-contiguous areas of the program. In our research, we have found that parallel operations in horizontal slices of the execution graph are indeed non-local, *i.e.*, the independent operations are coming from different areas of the program, thus there is merit in examining this issue model.

The CDG issue model can be exploited either by the hardware or the compiler, or both. For example, Beckmann [BP92] has proposed hardware support for multithreaded execution of serial programs. The execution conditions that fire off threads are based on the CDG rather than the more restrictive CFG. Compiler examples include PDG based scheduling techniques such as region scheduling [AJLS92, GS90]. These techniques implement a CDG based issue model on mundane hardware by applying speculative and non-speculative code motion such that code executes upon resolution of the control dependent predicate, rather than the preceding branch.

Figure 12 shows the CDG based control scheduling algorithm. ControlSchedule() constrains the operation to the time of the last control barrier as defined by the CDG. This is either:

- i. the level at which last control dependent branch was resolved,

- ii. or, if this instruction is not control dependent on any instruction in the current procedure, the level at which the current procedure began execution.

To compute the DDG level for case *i*, the procedure first calls LastCDNode() which returns the address of the last executed branch upon which inst is control dependent.<sup>6</sup> We employ the computationally efficient dominance frontier technique to annotate all the conditional branches upon which a basic block is control dependent [CFR+91]. This involves first computing the post-dominator tree [LT79]. And then, for each node in the CFG, a depth first traversal is used to identify the nodes in the CFG where some basic block no longer post dominates all of its successors. This is the *dominance frontier* of the CFG node. The control dependent branches are contained in the basic blocks of the dominance frontier. In our DDG analyzer, we annotate the trace stream at the beginning of each basic block with a list of addresses of the basic blocks on which the current one is control dependent (this need only be performed at the beginning of each basic block, as all instructions in a basic block will be control dependent on the same branches); LastCDNode() uses this list to find the correct control dependent branch.

The barrier stack (in variable barrierStack records the issue time of each procedure in the current call stack. Upon a call to a procedure, the control barrier level of the calling instruction is pushed onto the lastBarrier stack. This is later used to schedule instructions that have no statically defined control

<sup>&</sup>lt;sup>6</sup>The construction of the CDG will often result in a basic block being control dependent upon a number of different conditional branches or none. If dependent on multiple branches, the controlling predicate is always the latest to have executed in the current procedure instance.

```

var

lastBarrier: MAPPING from Address to Level;

barrierStack: STACK of Level;

{\bf function}\ \ {\bf ControlSchedule (inst:\ Inst,\ earliest:\ Level)};\ \ {\bf Level};

begin

if LastCDNode(inst) == NONE then

ControlSchedule := MAX (earliest, \, barrierStack.TOP);\\

else

ControlSchedule := MAX(earliest, \, lastBarrier[LastCDNode(inst)]); \\

endif

endfunc

procedure UpdateBarriers(inst: Inst, schedLevel: Level);

begin

if CondBranch(inst) then

if NOT Speculate(inst) then

lastBarrier[inst.pc] := schedLevel;

endif

endif

if CallInst(inst) then

barrier Stack. PUSH (last Barrier [Last CDNode (inst)]);\\

endif

if ReturnInst(inst) then

barrierStack.POP;

endif

endproc

```

Figure 12: CDG Control Scheduling Algorithm.

| Scheduling<br>Algorithm |        | Time<br>Complexity |             | Space<br>Complexity | Shown to<br>always out perform | Schedule non-deterministic latencies? |  |

|-------------------------|--------|--------------------|-------------|---------------------|--------------------------------|---------------------------------------|--|

| History                 |        | Find               | O(t)        |                     |                                | _                                     |  |

|                         |        | Delete             |             | O(t)                | List – best fit                | No, degrades to                       |  |

|                         |        | Insert             | O(l)        |                     | List – first fit               | List – best fit                       |  |

|                         |        |                    | O(t)        |                     |                                |                                       |  |

|                         |        |                    | $O(\log p)$ |                     |                                |                                       |  |

|                         | Best   | Delete             | $O(\log p)$ | O(p)                | List – first fit               | Yes, with                             |  |

|                         | Fit    | Insert             | $O(\log p)$ |                     |                                | check-out/check-in                    |  |

| List                    |        | Asymp              | $O(\log p)$ |                     |                                |                                       |  |

|                         |        | Find               | O(1)        | O(p)                |                                | Voc. with                             |  |

|                         | First  | Delete             | $O(\log p)$ |                     |                                | Yes, with check-out/check-in          |  |

|                         | Fit    | Insert             | O(1)        |                     |                                | CHeck-Out/check-in                    |  |

| 1                       |        | Asymp              | $O(\log p)$ |                     |                                |                                       |  |

|                         |        | Find               | O(1)        |                     |                                | Yes, with                             |  |

| Round R                 | obin   | Delete             | O(1)        | O(p)                |                                | check-out/check-in                    |  |

|                         |        |                    | O(1)        |                     |                                | Check-out/check-in                    |  |

|                         |        | Asymp              | O(1)        |                     |                                |                                       |  |

|                         |        | Find Delete        | O(1)        |                     |                                | Yes, with                             |  |

| Random                  | Random |                    |             | O(p)                |                                | check-out/check-in                    |  |

|                         |        | Insert             |             |                     |                                | CHeck-ont/Check-in                    |  |

|                         |        | Asymp              | O(1)        |                     |                                |                                       |  |

Table 1: Comparison of the scheduling heuristics. All time and space complexities are written with respect to either the trace size, t, the number of schedulable resources, p, the maximum deterministic latency, l, or a constant, 1. The "Asymp" time complexity refers to the asymptotic time complexity of managing the resource heap, and is bound to the most costly individual operation. Space complexity refers to just the resource heap nodes, and does not include the live well. Non-deterministic latencies are caused by the scheduling of physical memory resources. Their latencies are not known at the time they are scheduled, therefore a check-out/check-in scheduling mechanism must be employed.

dependencies (case ii). When a procedure returns, the issue level of that procedure is popped off the barrier stack.

# 3.5 Resource Scheduling

The next phase of scheduling, resource scheduling, serves to further constrain the DDG due to functional unit and storage limitations.

Since generating an optimal schedule for a DAG in the presence of resource limitations is an NP-complete problem, we must employ a scheduling heuristic. *Tetra* implements five scheduling heuristics which exhibit varying degrees of storage and space complexity during execution, and in return, provide equally varying degrees of performance with respect to an optimal schedule. These are: history schedule (HISTORY), list schedule—best fit (LIST-BF), list schedule—first fit (LIST-FF), round robin (RND-RBN), and random (RANDOM). Table 1 summarizes the five resource constrained scheduling heuristics.

Because the heuristic schedules only approximate the optimal schedule, a question naturally arises: how close to optimal is the heuristic schedule? This question is typically answered by generating what is called the *competitive ratio* [GGJ78] for the given heuristic. A competitive ratio is a numeric upper bound showing, for the worse case, how much longer the resulting heuristic schedule is compared to the length of the optimal schedule for the same problem instance. Using I to denote a problem instance, the notation OPT(I) represents the length of the optimal schedule for I, and HEUR(I) is the length of the heuristic schedule. The competitive ratio for the heuristic is:

$$\max\left\{\frac{HEUR(I)}{OPT(I)}\right\} \ \forall I$$

Since we cannot hope to examine all I, one must compute HEUR(I) as a non-naive lower bound and

OPT(I) as an upper bound, thus producing a result that is likely more conservative than the true competitive ratio of the heuristic. Advancing the state-of-the-art for a particular heuristic entails finding better lower bounds on HEUR(I), thus further tightening the accuracy of the competitive ratio. Computation of a non-naive competitive ratio for heuristics which schedule arbitrary DAGs in the presence of resource constraints is still an unsolved problem. We do not attempt to solve it here, rather we have proven (in Appendix A) a relative order on the performance of each of the presented heuristics. This ordering is summarized in Table 1 and in Figure 21 in Appendix A. To summarize those results, the relative ordering is such that as one spends more processor and memory resources on the scheduling heuristic, at least as good or better schedules will be generated.

There are two underlying assumptions that we adopted when selecting heuristics for scheduling limited resources. First, operations are always scheduled in the order that they occur in the trace (i.e., we apply an on-line scheduling heuristic). This assumption is required to make the heuristic solution reasonable to implement and execute. Second, we always schedule a particular resource (e.g., registers, physical memory, functional units) from a common pool. For example, when scheduling register resources, the resource pool is not associated with a particular register, but rather with all the registers. While this makes the implementation of the heuristics somewhat more complicated, it yields much better schedules. It is also more representative of compiler and dynamic processor scheduling techniques.

### 3.5.1 History Schedule

The history schedule heuristic is the most powerful (and expensive) because it retains complete history of all resource allocation, and thus it can back schedule. Back scheduling allows the scheduler to allocate a resource earlier in time than the previous allocation of that resource. While it may seem odd that we are scheduling a resource in the past, it is justifiable. The purpose of our analysis is to evaluate the performance of a program under an abstract processor and compiler model – execution models that aggressively exploit fine-grain serial program parallelism. It is unlikely that, if built, these processors would use the same instruction presentation, i.e., it is likely that the compiler would reorganize the instruction issue order such that it was closer to a breadth first visitation of the unconstrained, scheduled DDG. History scheduling allows Tetra to generate the best possible schedule independent of the presentation of the instructions.

Because back scheduling requires deterministic latency for scheduled operations (we are filling a hole in the schedule, so the allocation request must be finite and known), we cannot use this heuristic to build schedules with limited physical storage.

Figure 13 shows the ResourceSchedule() function, called from Figure 7, for the history scheduling heuristic.

The variable resHistory holds the complete resource history for the resource pool. A different resHistory variable will be required for each pool of resources. An entry at index i in the array indicates how many resource instances have been allocated to the level i in the scheduled DDG. Each entry in resHistory is bounded to MAX\_RESOURCES, the total number of resources in the resource pool. Since each level of the DDG is represented in resHistory, the array must have at least CRITICAL\_PATH\_LENGTH entries, where CRITICAL\_PATH\_LENGTH is the length of the program's critical path.

The algorithm scans resHistory for a slot of width PLatency(inst) with sufficient resources. When found, it then increments the array entries for these levels. By clamping the entries to MAX\_RESOURCES, we can ensure that any resource is allocated in any one level no more than once. PLatency(inst) is the pipeline fill latency of the operation, that is, how long the issue of the operation will delay the pipeline. After PLatency(inst) DDG levels, another operation can be inserted into the resource pipeline. For non-pipelined resources, like memory, the PLatency(inst) is equal to the total resource allocation latency.

In Figure 14(c), a DDG is scheduled using the history schedule heuristic. In this example, the operations 16 and 19 were back scheduled.