# **Code Generation Techniques**

Todd Alan Proebsting

Technical Report #1119

November 1992

# CODE GENERATION TECHNIQUES

Ву

### Todd Alan Proebsting

A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

Doctor of Philosophy

(Computer Sciences)

at the

UNIVERSITY OF WISCONSIN - MADISON

1992

## **Abstract**

Optimal instruction scheduling and register allocation are NP-complete problems that require heuristic solutions. By restricting the problem of register allocation and instruction scheduling for delayed-load architectures to expression trees we are able to find optimal schedules quickly. This thesis presents a fast, optimal code scheduling algorithm for processors with a delayed load of 1 instruction cycle. The algorithm minimizes both execution time and register use and runs in time proportional to the size of the expression tree. In addition, the algorithm is simple; it fits on one page.

The dominant paradigm in modern global register allocation is graph coloring. Unlike graph-coloring, our technique, *Probabilistic Register Allocation*, is unique in its ability to quantify the likelihood that a particular value might actually be allocated a register *before* allocation actually completes. By computing the likelihood that a value will be assigned a register by a register allocator, register candidates that are competing heavily for scarce registers can be isolated from those that have less competition. Probabilities allow the register allocator to concentrate its efforts where benefit is high and the likelihood of a successful allocation is also high. Probabilistic register allocation also avoids backtracking and complicated live-range splitting heuristics that plague graph-coloring algorithms.

Optimal algorithms for instruction selection in tree-structured intermediate representations rely on dynamic programming techniques. Bottom-Up Rewrite System (BURS) technology produces extremely fast code generators by doing all possible dynamic programming before code generation. Thus, the dynamic programming process can be very slow. To make BURS technology more attractive, much effort has gone into reducing the time to produce BURS code generators. Current techniques often require a significant amount of time to process a complex machine description (over 10 minutes on a fast workstation). This thesis presents an improved, faster BURS table generation algorithm that makes BURS technology more attractive for instruction selection. The optimized techniques have increased the speed to generate BURS code generators by a factor of 10 to 30. In addition, the algorithms simplify previous techniques, and were implemented in fewer than 2000 lines of C.

# Acknowledgements

I have benefited from the help and support of many people while attending the University of Wisconsin. They deserve my thanks.

My mother encouraged me to pursue a PhD, and supported me, in too many ways to list, throughout the process.

Professor Charles Fischer, my advisor, generously shared his time, guidance, and ideas with me.

Professors Susan Horwitz and James Larus patiently read (and re-read) my thesis.

Chris Fraser's zealous quest for small, simple and fast programs was a welcome change from the prevailing trend towards bloated, complex and slow software.

Robert Henry explained his early BURS research and made his Codegen system available to me.

Lorenz Huelsbergen distracted me with enough creative research ideas to keep graduate school fun.

National Science Foundation grant CCR-8908355 provided my financial support. Some computer resources were obtained through Digital Equipment Corporation External Research Grant 48428.

# Contents

| A | Abstract |                                |    |  |  |

|---|----------|--------------------------------|----|--|--|

| A | cknov    | wledgements                    | iv |  |  |

| 1 | Intr     | oduction                       | 1  |  |  |

|   | 1.1      | Overview                       | 1  |  |  |

|   | 1.2      | Instruction Scheduling         | 2  |  |  |

|   | 1.3      | Register Allocation            | 3  |  |  |

|   | 1.4      | Instruction Selection          | 5  |  |  |

| 2 | Del      | ayed-Load Scheduling           | 8  |  |  |

|   | 2.1      | Overview                       | 9  |  |  |

|   | 2.2      | Previous Work                  | 10 |  |  |

|   | 2.3      | Delayed-Load Architecture      | 12 |  |  |

|   | 2.4      | Register Allocation Trade-offs | 14 |  |  |

|   |          | 2.4.1 Canonical Form           | 14 |  |  |

|   |          | 2.4.2 Adding Registers Helps   | 16 |  |  |

|   | 0.5      | Optimal Algorithm for Delay=1  | 17 |  |  |

|   |     | 2.5.1    | Exceptional Cases for Delay=1                 | 9 |

|---|-----|----------|-----------------------------------------------|---|

|   |     | 2.5.2    | Algorithm                                     | 9 |

|   |     | 2.5.3    | Optimality Proof                              | 9 |

|   | 2.6 | Spilling | g                                             | 2 |

|   | 2.7 | Extens   | sions to DLS: Related Work                    | 7 |

|   |     | 2.7.1    | Non-Delayed Leaf Nodes                        | 7 |

|   |     | 2.7.2    | Unary Nodes 3                                 | 0 |

|   |     | 2.7.3    | Register Variables                            | 1 |

|   |     | 2.7.4    | DAGs, Forests, and Internal Loads             | 2 |

|   | 2.8 | Behav    | for for Delay>1                               | 4 |

|   |     | 2.8.1    | Non-Contiguous Operand Ordering               | 5 |

|   |     | 2.8.2    | Register Bounds                               | 6 |

|   |     | 2.8.3    | Empirical Results                             | 8 |

|   |     | 2.8.4    | Anomaly 3                                     | 8 |

|   | 2.9 | Conclu   | sion                                          | 9 |

| 3 | Pro | babilis  | tic Register Allocation 4                     | 1 |

|   | 3.1 | Overv    | ew                                            | 2 |

|   | 3.2 | Graph    | Coloring Allocators                           | 4 |

|   | 3.3 | Proba    | bilistic Register Allocation                  | 7 |

|   |     | 3.3.1    | Local Register Allocation and Probabilities   | 8 |

|   |     | 3.3.2    | Global Register Allocation and Probabilities  | 9 |

|   | 3.4 | Proba    | bilities Guide Global Register Allocation 5   | 9 |

|   |     | 3.4.1    | Improving Probabilistic Register Allocation 6 | 0 |

|   |     | 3.4.2    | Example                                       | 1 |

|   |      | 3.4.3  | Probabilities Improve Beatty's Algorithm       | • | • | <br>• | • | • | • | • | 65 |

|---|------|--------|------------------------------------------------|---|---|-------|---|---|---|---|----|

|   |      | 3.4.4  | Register Assignment                            |   | • |       |   |   |   |   | 67 |

|   | 3.5  | Implem | nentation Results                              |   |   |       |   |   |   | • | 68 |

|   |      | 3.5.1  | Stanford Benchmarks                            |   |   |       |   |   |   | • | 68 |

|   |      | 3.5.2  | SPEC Benchmarks                                |   |   |       |   |   |   |   | 71 |

|   |      | 3.5.3  | Comments                                       |   |   |       |   |   |   | • | 76 |

|   | 3.6  | Compi  | ler Performance                                |   |   |       |   |   |   |   | 76 |

|   | 3.7  | Algori | thm Extensions                                 |   |   |       | • |   |   |   | 77 |

|   |      | 3.7.1  | Manipulating Probabilities                     |   |   |       |   |   |   |   | 77 |

|   |      | 3.7.2  | Allocation Interactions                        |   |   | <br>• |   |   |   |   | 79 |

|   | 3.8  | Compl  | exity                                          |   |   |       |   |   |   |   | 79 |

|   | 3.9  | Other  | Uses for Probabilities                         |   |   |       | • |   | • |   | 80 |

|   |      | 3.9.1  | Assisting Graph Coloring                       |   |   |       |   |   |   |   | 81 |

|   |      | 3.9.2  | Assisting Interprocedural Allocation           |   |   |       | • |   |   |   | 82 |

|   | 3.10 | Phase- | Ordering Concerns                              |   |   |       |   |   | • | • | 83 |

|   | 3.11 | Conclu | ision                                          |   |   |       |   |   |   | • | 85 |

|   | DITT | ac m.₁ | ole Generation                                 |   |   |       |   |   |   |   | 86 |

| 4 |      |        |                                                |   |   |       |   |   |   |   | 87 |

|   | 4.1  |        | ew                                             |   |   |       |   |   |   |   |    |

|   | 4.2  | Relate | d Work                                         | • | • | <br>• | • | • | • | • | 90 |

|   | 4.3  | BURS   | $Model \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $ | • |   | <br>• | • | • | • | • | 92 |

|   |      | 4.3.1  | Normal Form Patterns                           |   |   | <br>• | • |   |   | • | 94 |

|   | 4.4  | Algori | thm to Generate BURS Tables                    |   |   |       |   |   |   | • | 94 |

|   |      | 4.4.1  | Data Structures Used to Generate BURS Tables   |   |   | <br>• |   |   |   |   | 95 |

|   |      | 4.4.2  | Chain Rules                                    |   |   |       |   |   |   |   | 96 |

|      | 4.4.3  | Computing States and Transitions   | 97  |

|------|--------|------------------------------------|-----|

|      | 4.4.4  | State Trimming                     | 102 |

| 4.5  | Diverg | ing Grammars                       | 107 |

| 4.6  | Speed  | Optimizing Techniques              | 108 |

|      | 4.6.1  | Attempt Cheaper Alternatives First | 108 |

|      | 4.6.2  | Precompute Values                  | 108 |

|      | 4.6.3  | Lazy Computations                  | 109 |

|      | 4.6.4  | Defer Closure                      | 109 |

|      | 4.6.5  | Itemset Equivalence                | 110 |

|      | 4.6.6  | Specialize Memory Allocation       | 111 |

|      | 4.6.7  | Minimize space                     | 111 |

| 4.7  | Unpro  | fitable Optimizations              | 112 |

|      | 4.7.1  | Closure Speedup                    | 112 |

|      | 4.7.2  | Post-pass State Minimization       | 112 |

|      | 4.7.3  | Normalize Specialization           | 113 |

| 4.8  | Outpu  | t                                  | 113 |

| 4.9  | Impler | mentation Results                  | 114 |

| 4.10 | Other  | Applications of BURS               | 116 |

|      | 4.10.1 | Simple Type Inferencing            | 116 |

|      | 4.10.2 | Data Structure Auditing            | 117 |

|      | 4.10.3 | Tree Simplification                | 118 |

| 4.11 | Relate | d Systems                          | 118 |

|      | 4.11.1 | Twig                               | 119 |

|      | 4110   | DEC                                | 110 |

|    | 4.12  | Conclusion               | 120 |

|----|-------|--------------------------|-----|

| 5  | Con   | clusions and Future Work | 122 |

| A  | BUI   | RG Reference Manual      | 125 |

|    | A.1   | Overview                 | 125 |

|    | A.2   | Input                    | 126 |

|    | A.3   | Output                   | 129 |

|    | A.4   | Debugging                | 134 |

|    | A.5   | Running Burg             | 136 |

|    | A.6   | Acknowledgements         | 137 |

| Ri | hliog | ranhy                    | 137 |

# Chapter 1

# Introduction

The three main problems in code generation are what instructions to use, in what order to do the computations, and what values to keep in registers.

Aho, Johnson, and Ullman [AJU77].

### 1.1 Overview

This thesis describes the following issues in code generation theory and technology: Chapter 2 develops an optimal instruction scheduler and register allocator for delayed-load architectures, Chapter 3 describes probabilistic register allocation, a new global register allocation heuristic that is simpler and more effective than widely-used graph-coloring techniques, and Chapter 4 outlines the design and implementation of new and highly optimized techniques for producing retargetable BURS instruction selectors. Appendix A is a reference manual for BURG, the code generator-generator system developed using the techniques described in Chapter 4.

### 1.2 Instruction Scheduling

The instruction scheduling phase of code generation determines the order in which program instructions will execute. For modern machine architectures with pipeline constraints this phase of compilation is essential to generating efficient code. A common pipeline constraint on reduced instruction set computer (RISC) architectures is that a value loaded from memory into a register will not be available for use for some number of subsequent cycles. During the intervening cycles it is important to schedule other instructions to execute that do not rely on that loaded value.

Machines with such load constraints are called delayed-load architectures. RISC chips like the MIPS R2000 and the SPARC are both delayed-load architectures that require a single additional cycle before a loaded value is available in its target register. For these two machines, it is necessary to find one instruction that can execute immediately after the load instruction (and does not rely on the loaded value). If no such instruction can be found, then it is necessary to do nothing for that cycle—thereby wasting it. On the R2000, it is necessary to put an explicit NOP in the instruction stream; on the SPARC, the pipeline will automatically interlock and stall the processor for the additional cycle.

Previously, most instruction schedulers handled delayed-load scheduling by solving a more general problem of arbitrary instruction scheduling ([HG83], [GM86], [War90], [LLM+87], and [PS90]). Arbitrary instruction scheduling considers operations other than loads with delays (such as multiplies/divides) that can take many cycles to complete. This thesis describes the delayed-load scheduling (DLS) algorithm for doing instruction scheduling for computations in which the only instructions facing pipeline constraints are loads. The more general algorithms are heuristic and typically take  $O(n^2)$  time (where n is the number of instructions to be scheduled). DLS, on the other

hand, takes only O(n) time, and is optimal when the load delay is one cycle. When the delay is greater than one cycle, DLS works as an excellent heuristic.

Most of the more general scheduling algorithms do not attempt to do register allocation along with scheduling. They either schedule before allocation or afterwards, but the two issues are considered separately. This phase-ordering problem can cause the phase that comes second to work poorly. If scheduling comes first, registers tend to be over-allocated. If allocation comes first, the number of possible schedules (given that allocation) can be quite small, and may not include any good schedules. DLS, on the other hand, integrates instruction scheduling with register allocation. Done together, DLS is able to find the optimal schedule that uses the *minimum* number of registers for any optimal schedule.

Chapter 2 describes the delayed-load scheduling algorithm, DLS. In addition to the algorithm, the chapter includes an optimality proof for machines with delay of one, empirical results when the delay is greater than one, and extensions to handle expressions that require more than the available number of registers.

## 1.3 Register Allocation

Instructions that access operands in registers are usually cheaper than those that access operands in memory. Many instructions cannot access memory directly: if an operand is in memory, it is necessary to explicitly load that operand for use. In either case, it is advantageous to keep frequently used operands in registers.

Registers, however, are scarce. Even RISC processors, which are often characterized as having many registers, typically have fewer than 32 general purpose registers. Often, in a computer program, there are many more values that are candidates to go in registers

than there are registers. The *register allocation* phase of code generation is responsible for determining which values can most advantageously be held in registers and at what points in the program.

Estimating the benefit of allocating a register to a value is not difficult. Execution frequency estimates for each instruction accessing the value are simply multiplied by the potential savings at each instruction. What is more difficult to estimate is how an allocation will affect subsequent allocation decisions.

If a value is allocated a register over a given set of program points, no other value that is simultaneously live can be allocated the same register. Each allocation made by a register allocator is made at the expense of other candidates. While there may be a candidate that will yield the greatest single immediate benefit, it may be the case that it will take a register from many other candidates whose aggregate benefit would have been greater.

Previous global register allocation methods have concentrated on casting register allocation as a graph-coloring problem ([CAC+81], [CH90], [BCKT89], [LH86]). Since no two simultaneously live values may be assigned to the same register, an *interference graph* can be built where nodes represent register candidate values, and arcs exist between simultaneously live values. Heuristics are used to find an assignment of the available registers to the nodes such that two connected nodes are not assigned the same register. Unfortunately, while graph coloring ensures a legal assignment, it does not accurately measure how the different (connected) nodes are competing—only that they are competing—for registers.

To more accurately measure the effects of allocation of a register to one value over another, a *probabilistic* measure can be made. Our technique, *probabilistic* register

allocation, quantifies the likelihood that a particular value might actually be allocated a register before allocation completes. By computing the likelihood that a value will be assigned a register by a register allocator, register candidates that are competing heavily for scarce registers can be isolated from those that face lower competition. These probabilities allow the register allocator to concentrate its efforts where benefit is high and where the competition for registers is low.

The implementation of a register allocator that exploits these probabilistic estimates has proven to be very successful in finding profitable candidates for register allocation while weighing both the benefit of the allocation, and the effects of such an allocation.

### 1.4 Instruction Selection

Instruction scheduling and register allocation often assume that instructions have already been chosen to do the computations required. The *instruction selection* phase of compilation determines which instructions can best do those computations. Typically, instructions are selected to minimize the size of the generated code, or to minimize the execution time. The instruction sets of most modern CPU's are redundant. That is, there are computations that may be evaluated via two or more different sequences of instructions. The instruction selector must choose among the various (correct) options to produce the best code.

Machine architectures are not trivial, and it is not always obvious what code will most cheaply evaluate some expression. Many complex instruction set computer (CISC) architectures have many addressing modes, each of which may subsume some number of additions and shifts. Simply recognizing where they are applicable may seem difficult. Furthermore, comparing all possible combinations that legally compute the desired

result might seem computationally intensive.

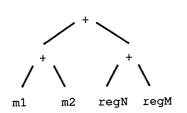

Fortunately, if we restrict our attention to expression trees (rather than the more general directed acyclic graphs) selecting optimal instructions is a straightforward problem. To do this, we will express the instruction set of the machine as a set of tree patterns. If the tree patterns that describe different instructions are given weights to describe their relative costs, dynamic programming can be used to select the optimal set of instructions to evaluate the tree ([AGT89], [AJ76], [PLG88], [BDB90], and [AG85]).

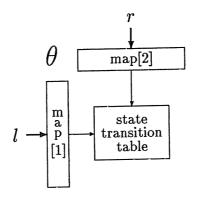

Dynamic programming is an expensive operation since it finds all optimal subsolutions before finding a solution for the entire tree. Fortunately, Bottom-Up Rewrite System (BURS) technology, can hide this cost from the compiler [PLG88]. BURS technology pre-processes the tree patterns and their costs to build automata that can drive instruction selection very quickly. BURS generated instruction selectors can be built that execute fewer than 50 VAX instructions per node of an expression tree [FH91c].

BURS code generators are fast for two reasons: they use bottom-up tree pattern matching technology (the theoretically fastest possible [HO82]), and they do all dynamic programming at compile-compile time (i.e., when the patterns are pre-processed to build the code generator). By doing dynamic programming at compile-compile time, a BURS code generator can anticipate all possible input trees with information stored in tables. An enormous amount of computation is necessary to do dynamic programming in anticipation of all possible trees. It is, therefore, important to have an efficient BURS automata generator.

Chapter 4 describes an extremely fast BURS automata generator. The algorithm described is a work-list algorithm that employs simple optimizations. The implementation of the simple algorithm is a code generator generator, BURG, that runs 10 to

30 times faster than the previous best system [FHP91]. That increase in speed lowered the time to pre-process a VAX grammar from over 7 minutes to under 15 seconds on a DECstation 5000.

Since its development, BURG has been made publicly available, and is being used at AT&T Bell Labs to develop code generators for an ANSI C compiler [FH91b].

# Chapter 2

# Delayed-Load Scheduling

Modern RISC architectures are characterized by small, simple instruction sets, and general-purpose registers. While simple functionally, many of the instructions are complicated by instruction scheduling requirements. For instance, on a MIPS R2000, an integer load from memory into a register requires a single delay cycle before the loaded value can be accessed. It is necessary to find another instruction—that does not rely on the loaded value, or contribute to the load's address computation—to be placed immediately after the load. If no useful instruction can be found, it is necessary to put a NOP after the load to absorb the *delay* cycle.

Figure 2.1 gives two legal MIPS R2000 code sequences for evaluating (a+b)+c. The instructions selected to evaluate the expression are the same except for register assignment. The useful instructions differ only in their schedules (orders) and numbers of registers used. The right sequence requires two NOP's because the values loaded are accessed by the subsequent instructions. A compiler (or assembler) must order instructions carefully to minimize the costs of scheduling constraints.

While the optimal evaluation order in Figure 2.1 requires two fewer instructions than

| Optimal         | Non-Optimal     |

|-----------------|-----------------|

| ld ri, a        | ld ri, a        |

| ld r2, b        | ld r2, b        |

| ld r3, c        | nop             |

| addi r1, r1, r2 | addi r1, r1, r2 |

| addi r1, r1, r3 | ld r2, c        |

| -               | nop             |

| -               | addi r1, r1, r2 |

Figure 2.1: Two Legal Schedules to Evaluate (a+b)+c on a MIPS R2000.

the non-optimal, it does require one more register. Avoiding scheduling conflicts requires the ability to move operations away from the instructions that load their operands. This lengthens the span of those register operands, and, therefore, increases the number of registers in use. Because registers are scarce, and can be advantageously used to hold temporary and global values, it is important not to overuse them when scheduling instructions.

### 2.1 Overview

The problem of optimally scheduling instructions under arbitrary pipeline constraints is NP-complete ([GJ79], [LLM+87], [HG82], and [PS90]). Many heuristics have been proposed for scheduling pipelined code; all assume, however, that pipeline constraints can occur after any instruction, and that operators may share common subexpressions. The intractability of finding an optimal schedule holds even if an unlimited number of registers is available. Optimal local register allocation in itself is also NP-complete in the presence of common subexpressions [GJ79]. Such negative results have led to the belief that generating good quality code for RISC machines with pipeline constraints is too difficult to do well except in complex optimizing compilers.

Fast, optimal algorithms, however, can be devised for simpler, yet realistic architectures. Our results show that for a restricted set of pipeline constraints and a simple RISC load/store architecture, optimal code can be generated in linear time for expressions without operand sharing. Our delayed-load scheduling algorithm, DLS, efficiently combines instruction scheduling and register allocation. It is restricted to handling expression trees in which all leaf nodes are direct memory references. DLS is as an attractive, simple, fast and effective alternative to more complicated, slower heuristic solutions.

### 2.2 Previous Work

An adaptation of Hu's algorithm [Hu61] gives an optimal solution to scheduling a tree-structured task system on multiple identical processors if each task has unit execution time [Cof76], but the algorithm does not handle register allocation constraints. For an architecture with 2 functional units, one for loads and one for operations, with identical pipeline constraints, Bernstein et. al. have investigated code scheduling with register allocation for trees ([BPR84] and [BJR89]). Although applicable to a much different machine, Bernstein's results and algorithms are similar to ours<sup>1</sup>—both minimize pipeline interlocks and register usage, and both run in O(n) time (where n is the number of nodes in the expression).

Code scheduling algorithms and heuristics for pipelined architectures have been extensively studied in recent years. Most of the attention to code scheduling has been

<sup>&</sup>lt;sup>1</sup>Ours can issue only one instruction per cycle.

directed at scheduling expressions represented by directed acyclic graphs (DAGs) for architectures with pipeline constraints after both loads and operations.<sup>2</sup> Heuristic attacks on this general problem can be found in [HG82], [HG83], [GM86], [War90], [LLM+87], and [PS90]. These techniques are similar in spirit; they schedule instructions from the bottom of the DAG based on differing priority heuristics. The heuristics tend to favor those instructions that (a) are ready to execute (i.e., do not face pipeline constraints); (b) will cause subsequent pipeline constraints (i.e., need to be scheduled early); (c) are "far" from the roots of the DAG (i.e., may be on a critical execution path).

Many heuristic solutions treat register allocation as a separate issue that occurs either before or after scheduling. Most heuristics work in a breadth-first manner from the bottom of the DAG up, they tend to cause many values to be live at once—filling up scarce registers. Unlike DLS, these algorithms fail to fully integrate code scheduling and register allocation, and therefore suffer from phase-ordering problems. In addition, whereas DLS runs in O(n) time, these algorithms run in  $O(n^2)$  time, and must have an additional register allocation phase.

Attempts to integrate register allocation and scheduling have been made at the basic block level. The techniques express the data dependences between instructions within a basic block as a DAG. Given the DAG, they attempt to schedule the instructions while both obeying pipeline constraints and minimizing registers. Since both optimal scheduling and register allocation on DAGs are NP-complete problems, their solutions to the integrated problem are heuristic.

Goodman and Hsu [GH88] describe a system, Integrated Prepass Scheduling (IPS), that combines register allocation and instruction scheduling. IPS is conceptually simple.

<sup>&</sup>lt;sup>2</sup>We will use operations to denote non-load instructions.

The input is an instruction DAG for which registers have not been assigned. IPS consists of two possible schedulers: CSP, and CSR. CSP does heuristic scheduling at the cost of voracious register use, and CSR tends to minimize register use while possibly doing poor scheduling. Given a DAG, IPS schedules instructions using CSP and maintains a count of live registers. When the count exceeds a threshold, IPS switches to CSR to reduce register usage. Once reduced appropriately, IPS reverts to CSP. This oscillation continues until the scheduling process is complete.

Bradlee, Eggers, and Henry [BEH91] describe another integrated system, Register Allocation with Schedule Estimates (RASE), and compare it to IPS. RASE works in three sequential passes: PRESCHED, GRA, and FINALSCHED. For each basic block, PRESCHED estimates the cost of evaluating that basic block with n registers available, for all legal register counts. Given these cost vectors, the global register allocator, GRA, computes the optimal number of registers to give to the block in face of register competition for global values. FINALSCHED simply completes the schedule required by the register level determined by GRA.

Bradlee found that IPS and RASE work well in practice—reducing execution time by an average of 12%. While RASE occasionally worked better, the resulting improvement was not significant. Both systems rely on heuristic scheduling techniques that are slow  $(O(n^2))$ , and require an *ad hoc* integration of register allocation and instruction scheduling.

## 2.3 Delayed-Load Architecture

We restrict our attention to a simple class of architectures—RISC load/store architectures with delayed loads. All instructions require a single instruction cycle to issue, and

| reg     | <b>←</b>     | memory             | load memory, reg               |

|---------|--------------|--------------------|--------------------------------|

| $reg_i$ | $\leftarrow$ | $reg_j$ op $reg_k$ | op $reg_j$ , $reg_k$ , $reg_i$ |

| memory  | $\leftarrow$ | reg                | store reg, memory              |

Figure 2.2: DLS Machine Model

| Cycle# | With Interlocks | Without Interlocks |

|--------|-----------------|--------------------|

| 1.     | load m1, r1     | load m1, r1        |

| 2.     | load m2, r2     | load m2, r2        |

| 3.     |                 | load m3, r3        |

| 4.     | add r1, r2*, r2 | load m4, r4        |

| 5.     | load m3, r1     | add r1, r2, r2     |

| 6.     | load m4, r3     | add r3, r4, r4     |

| 7.     |                 | add r2, r4, r4     |

| 8.     | add r1, r3*, r3 |                    |

| 9.     | add r2, r3, r3  |                    |

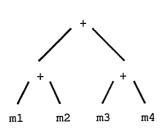

Figure 2.3: Sample Expression Tree and Two Evaluation Sequences

only loads are pipelined. Our simple machine's instruction set is given in Figure 2.2. This architecture is an approximation of the integer functional units of many modern RISC processors such as the SPARC and MIPS R3000 [PH90].

A delayed load requires that the destination of a load not be accessed by subsequent instructions for some number of instruction cycles, although other, unrelated instructions may execute. Delay will be used to refer to the number of cycles that must elapse before the destination register is ready to be used. An attempt to use a destination register prior to the elapsing of Delay cycles forces a pipeline interlock that blocks processor execution until the register has finished loading.

Figure 2.3 shows two possible evaluations of an example expression tree. It is assumed that Delay=1. The (naively produced) left sequence wastes cycles due to pipeline interlocks at times 3 and 7—asterisks (\*) denote the registers with which the delays are associated. The right sequence incurs no delays.

## 2.4 Register Allocation Trade-offs

Register allocation and instruction scheduling interact because the order of instructions determines the register needs for computing a given expression. Likewise, register allocation can limit or expand the possibilities for re-ordering code to limit pipeline interlocks.

If register allocation precedes instruction scheduling, the ability to schedule the code can be severely limited by constraints induced not by data dependences, but by constraints introduced by potential register interference. If register allocation follows instruction scheduling, a given schedule may require unnecessarily many registers, thus limiting the effectiveness of a global optimizer and possibly requiring spill code. This well-known phase-ordering problem is accepted in practice, but can lead to sub-optimal register use because the instruction schedulers minimize interlocks without taking into account the possibility that increased register demands could lead to costly register spilling.

The DLS algorithm avoids this phase-ordering problem by scheduling code and allocating registers in tandem. DLS optimally schedules instructions to avoid all delayed-load interlocks for expression trees when Delay=1. Furthermore, it finds an interlock-free schedule that minimizes register usage. When Delay>1 or when DAGs are transformed into trees, DLS serves as an excellent heuristic while retaining its conceptual simplicity, guaranteed linear performance, and integrated register allocation.

#### 2.4.1 Canonical Form

Generating code and allocating registers is much simpler for expression trees than for arbitrary DAGs. Once a preliminary schedule for the code has been generated for a

tree, and the register needs determined, it is possible to reschedule the code and reassign the registers to obtain a code sequence in a canonical form. This canonical form

has three important invariants: the relative order of the operators remains unchanged,

the relative order of the loads remains unchanged, and the number of registers needed

remains unchanged. For a given number of registers and specific operation and load

orders, the canonical order will minimize pipeline interlocks for a delayed-load machine.

The canonical schedule is produced by moving loads as early as possible in the initial instruction sequence (subject to the three invariants). Shifting the loads will move a load away from its parent in the tree and therefore increase the number of instructions between the load and its dependent operation.

To produce the canonical ordering of an instruction sequence using R registers that has L loads and (L-1) operations,<sup>3</sup> create an ordering that consists of R loads followed by an alternating sequence of L-R (op,load) pairs, followed by the remaining R-1 operations. Loads are moved before operations that they had previously followed—this does not affect data dependences since all operations depend on registers and all loads depend on memory. The movement of the loads relative to the operations will cause the necessary register assignments to change; if done systematically this will not cause the register needs to increase. Since loads increase the number of registers in use by one, and operations decrease the number of registers in use by one, the number of registers in use at any point in the evaluation is equal to the number of loads performed minus the number of operations performed. A canonical order evaluation, therefore, ensures that the number of registers in use will never exceed R.

<sup>&</sup>lt;sup>3</sup>There are (L-1) operations in a binary tree with L loads.

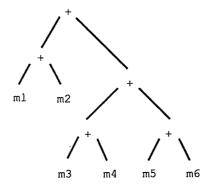

Figure 2.4 gives an example expression with a standard Sethi-Ullman (SU) instruction schedule [SU70], a canonical order with 3 registers, and a canonical order assuming 4 registers. (The Sethi-Ullman order, which is optimal with respect to register usage, orders instructions by scheduling sub-trees separately so that the sub-tree with the greater register needs is scheduled first.) Simply putting the SU-generated instructions into canonical form without additional registers removes 1 pipeline interlock. Adding the extra register eliminates all interlocks. Note that the relative orders of loads and the relative order of operations is the same in all three sequences.

### 2.4.2 Adding Registers Helps

As is seen in Figure 2.4, adding registers sometimes helps. This follows from the observation that loads can often be *shifted* backwards (*i.e.*, earlier) in the instruction sequence without affecting the outcome of the computation. This shifting does not change the relative ordering of the loads with respect to one another, or the relative ordering of the operations with respect to one another—it simply shifts the loads farther from the operations that use them. Shifting a load farther away allows its delay slot to be filled with an intervening load or operation.

Minimizing the number of registers needed to evaluate an expression without load delays is an essential consideration. If the operations in the expression tree in Figure 2.4 were evaluated from left to right, it would be necessary to use 5 registers rather than 4 to produce a canonical evaluation without interlocks. It is therefore necessary to treat the problem of optimal code generation as one of minimizing pipeline interlocks and register usage through code scheduling.

| #   | Sethi-Ullman(3) | Canonical(3)    | Canonical(4)   |

|-----|-----------------|-----------------|----------------|

| 1.  | load m3, r1     | load m3, r1     | load m3, r1    |

| 2.  | load m4, r2     | load m4, r2     | load m4, r2    |

| 3.  |                 | load m5, r3     | load m5, r3    |

| 4.  | add r1, r2*, r2 | add r1, r2, r2  | load m6, r4    |

| 5.  | load m5, r1     | load m6, r1     | add r1, r2, r2 |

| 6.  | load m6, r3     |                 | load m1, r1    |

| 7.  |                 | add r3, r1*, r1 | add r3, r4, r4 |

| 8.  | add r1, r3*, r3 | load m1, r3     | load m2, r3    |

| 9.  | add r2, r3, r3  | add r2, r1, r1  | add r2, r4, r4 |

| 10. | load m1, r1     | load m2, r2     | add r1, r3, r3 |

| 11. | load m2, r2     |                 | add r4, r3, r3 |

| 12. |                 | add r3, r2*, r2 |                |

| 13. | add r1, r2*, r2 | add r1, r2, r2  |                |

| 14. | add r3, r2, r2  |                 |                |

Figure 2.4: Expression Tree and Canonical Instruction Sequences

## 2.5 Optimal Algorithm for Delay=1

Optimal instruction scheduling and register allocation for an expression tree when Delay=1 can be done in time proportional to the size of the expression tree. Our DLS algorithm is a variation of the Sethi-Ullman algorithm adapted to our machine model. Both the SU algorithm and the DLS algorithm are driven by minimizing the register needs for evaluating an expression. These needs are denoted as the minReg of a node and refer to the minimal number of registers needed for computing the sub-tree

rooted at that node without spilling. The minReg value of a node is simply the standard SU number, adapted to our load/store architecture.<sup>4</sup> It is calculated by the following procedure, label().

The order of operations for an expression tree determines the optimal order of the loads—the loads will appear in the same relative order as their parents. This follows because forcing two (load,op) pairs,  $(l_i, op_i)$  and  $(l_k, op_k)$  (assuming that  $op_i$  comes before  $op_k$ ), out of order would force the separation between  $(l_i, op_i)$  to be less than it was originally and less than the original  $(l_k, op_k)$  distance. This decrease in separation could cause pipeline interlocks. The increase in  $(l_k, op_k)$  separation may avoid some interlocks, but the net effect cannot be advantageous. The goal of finding the optimal instruction schedule and register usage therefore reduces to finding the optimal operation schedule and register usage.

<sup>&</sup>lt;sup>4</sup>The original SU algorithm was based on a machine model in which binary operations could access their right operands directly from memory. Our model requires all operands to be in registers.

### 2.5.1 Exceptional Cases for Delay=1

When Delay=1, exactly two trees in our model have schedules that must always incur pipeline interlocks: the tree consisting of a single node, and the tree consisting of a single operator and two leaf (memory) nodes. It is trivial to verify that these must incur pipeline interlocks, and that the register needs for these trees are 1 and 2, respectively.

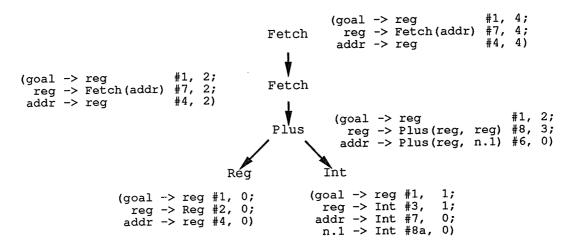

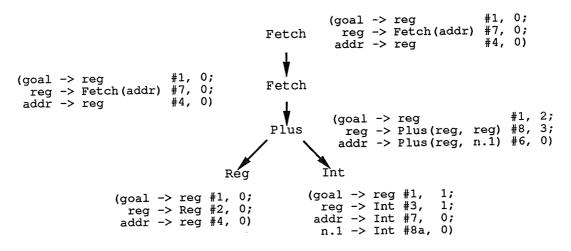

### 2.5.2 Algorithm

The DLS algorithm presented in Figure 2.5 finds an instruction schedule and register assignment that is optimal for a given expression tree. For all trees with the exception of the two just mentioned, the DLS schedule will have no pipeline interlocks and will use the minimal number of registers for *any* schedule without interlocks.

The number of registers needed for such a schedule is exactly one more than the minimal number of registers needed to evaluate the expression without any spills (i.e., the SU minReg value of the root of the expression).

The DLS algorithm is a simple three-pass algorithm for finding the optimal instruction sequence and register allocation. The procedure label() (given earlier) labels the nodes with their SU minReg values. Procedure order() finds the operation and load orders. order() is similar to the original Sethi-Ullman algorithm. schedule() then emits the instructions in canonical order.

### 2.5.3 Optimality Proof

The argument that the DLS algorithm creates an optimal instruction schedule and register allocation follows from two observations: the number of registers to avoid interlocks must be at least minReg+1, and the canonical order generated by the algorithm using

```

// Sethi-Ullman Ordering

procedure order(root : ExprNode; var opSched, loadSched : NodeList) {

if (not isLeaf(root)) {

if (root.left.minReg < root.right.minReg) {</pre>

order(root.right, opSched, loadSched);

order(root.left, opSched, loadSched);

order(root.left, opSched, loadSched);

order(root.right, opSched, loadSched);

}

append(root, opSched);

} else {

append(root, loadSched);

}

}

// Canonical Ordering

procedure schedule(opSched, loadSched : NodeList; Regs : integer) {

initialLoads : integer = MIN(Regs, length(loadSched));

for i = 1 to initialLoads do {

// Loads First

ld = popHead(loadSched);

ld.reg = getReg();

gen(Load, ld.name, ld.reg);

}

// (Operation, Load) Pairs

while (not Empty(loadSched)) {

op = popHead(opSched);

op.reg = op.right.reg;

gen(op.op, op.left.reg, op.right.reg, op.reg);

ld = popHead(loadSched);

ld.reg = op.left.reg;

gen(Load, ld.name, ld.reg);

// Remaining Operations

while (not Empty(opSched)) {

op = popHead(opSched);

op.reg = op.right.reg;

gen(op.op, op.left.reg, op.right.reg, op.reg);

freeReg(op.left.reg);

}

}

// Schedule Instructions

procedure generate(root : ExprNode; Delay : integer) {

// Compute minReg

label(root)

opSched = loadSched = emptyList();

// Initialize

// Find Load/Op Order

order(root, opSched, loadSched);

schedule(opSched, loadSched, root.minReg+Delay); // Emit Canonical Order

}

```

Figure 2.5: Optimal Delay Load Scheduling (DLS) Algorithm

minReg+1 registers does not incur pipeline interlocks.

To incur no load delays requires at least minReg+1 registers. The evaluation cannot take fewer than minReg registers by definition. If only minReg registers were available, there must be a point at which a just loaded register must be used in the next instruction, which would result in a load delay. This follows from the fact that only loads can increase the number of registers in use, and thus at some point a load must put minReg registers in use. Because only minReg registers are available, this load must be followed by an operation on the just loaded register (if another operation could have been scheduled, it would have been to keep the number of registers in use at a minimum). Therefore, more than minReg registers are needed to avoid interlocks.

Because Delay=1, it is only necessary to find a single instruction to fill every load delay slot. These can be other loads or (unrelated) operations. Adding another register, but keeping a Sethi-Ullman ordering for the operations and a canonical ordering for the entire instruction stream assures that there is at least one more register live than there is in an SU order. This register must have been made live by a load since the SU algorithm would have at most minReg registers live at any point. In other words, the loads are at least one step ahead of the operations that can use them. Since the delay slot is exactly one cycle long, and loads are at least one cycle ahead, the loads must always be followed by an unrelated instruction. This means no pipeline interlocks occur for any expression tree with at least 3 operands (except for the two previously mentioned exceptions).

The DLS algorithm creates an operation order that can be evaluated using exactly minReg registers because it creates a Sethi-Ullman ordering for the operations and loads. Because it schedules the instructions in canonical order using a single extra register, it must satisfy the necessary conditions specified in the previous paragraph. Therefore,

given a single extra register, the algorithm creates an instruction sequence optimal in evaluation time and register usage.

## 2.6 Spilling

For the DLS algorithm to be practical, it must also be able to produce good schedules when fewer than minReg+1 registers are available for allocation. Suppose, for example, that exactly minReg registers are available. Should the algorithm introduce spill code so that sub-trees may be computed without interlocks? If so, where should the spills be introduced? If not, will the computation incur excessively many pipeline interlocks? The best solution depends on the form of the expression tree.

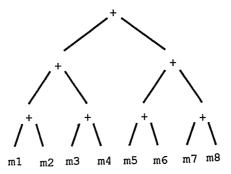

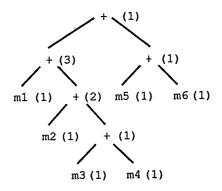

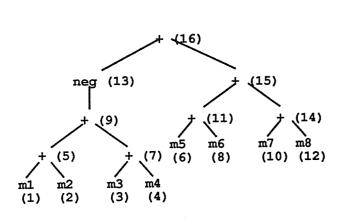

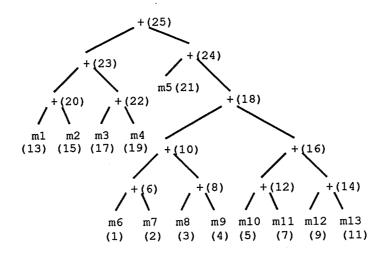

The tree in Figure 2.6 can be best handled by allowing the canonical execution order (with minReg=4 registers) and incurring a single load delay of 1 cycle. Having no interlocks would have required a spill and hence cost 2 extra instructions, a store and load. The tree in Figure 2.7 will incur 3 delay cycles, but would incur only the cost of a single load and store if a spill were introduced.

Ordering code so that spill/delay costs will be minimized requires extending the original DLS algorithm. Given an expression with two sub-trees that have identical minReg values, the algorithm orders the sub-trees such that the sub-tree exerting the minimal register pressure is scheduled last. The register pressure of a sub-tree is relative to the minReg of that sub-tree; it is simply a count of the times that minReg registers will be live in a normal SU evaluation order of the sub-tree. Register pressure is calculated by the routine in Figure 2.8.

The sub-trees of the tree in Figure 2.9 are labeled with their register pressures. The register pressure of the left sub-tree is 3 because its minReg value is 2, and in its

| #   | No Spill—Interlock | Spill—No Interlock |

|-----|--------------------|--------------------|

| 1.  | load m1, r1        | load m1, r1        |

| 2.  | load m2, r2        | load m2, r2        |

| 3.  | load m3, r3        | load m3, r3        |

| 4.  | load m4, r4        | load m4, r4        |

| 5.  | add r1, r2, r2     | add r1, r2, r2     |

| 6.  | load m5, r1        | load m5, r1        |

| 7.  | add r3, r4, r4     | add r3, r4, r4     |

| 8.  | load m6, r3        | load m6, r3        |

| 9.  | add r2, r4, r4     | add r2, r4, r4     |

| 10. | load m7, r2        | load m7, r2        |

| 11. | add r1, r3, r3     | store r4, TEMP     |

| 12. | load m8, r1        | load m8, r4        |

| 13. |                    | add r1, r3, r3     |

| 14. | add r2, r1*, r1    | load TEMP, r1      |

| 15. | add r3, r1, r1     | add r2, r4, r4     |

| 16. | add r4, r1, r1     | add r3, r4, r4     |

| 17. |                    | add r1, r4, r4     |

Figure 2.6: Spilling May be More Expensive than Interlocks—Example with 4 Registers

| #   | No Spill—Interlock | Spill—No Interlock |

|-----|--------------------|--------------------|

| 1.  | load m3, r1        | load m3, r1        |

| 2.  | load m4, r2        | load m4, r2        |

| 3.  | load m2, r3        | load m2, r3        |

| 4.  | add r1, r2, r2     | add r1, r2, r2     |

| 5.  | load m1, r1        | load m1, r1        |

| 6.  | add r3, r2, r2     | add r3, r2, r2     |

| 7.  | load m7, r3        | load m7, r3        |

| 8.  | add r1, r2, r2     | add r1, r2, r2     |

| 9.  | load m8, r1        | load m8, r1        |

| 10. |                    | store r2, TEMP     |

| 11. | add r3, r1*, r1    | load m6, r2        |

| 12. | load m6, r3        | add r3, r1, r1     |

| 13. |                    | load m5, r3        |

| 14. | add r1, r3*, r3    | add r2, r1, r1     |

| 15. | load m5, r1        | load TEMP, r2      |

| 16. |                    | add r3, r1, r1     |

| 17. | add r3, r1*, r1    | add r2, r1, r1     |

| 18. | add r2, r1, r1     |                    |

Figure 2.7: Spilling May Save Cycles—Example with 3 Registers

```

if (isLeaf(node)) {

node.pressure = 1;

} else {

if (node.left.minReg == node.right.minReg) {

// Assumes that node with minimal pressure is scheduled last.

node.pressure = MIN(node.left.pressure, node.right.pressure);

} else if (node.left.minReg > node.right.minReg) {

// node.left will be scheduled first -- Following standard SU rule.

if (node.left.minReg == node.right.minReg+1) {

// both subtrees contribute register pressure

node.pressure = node.left.pressure + node.right.pressure;

} else {

// only the first subtree contributes register pressure

node.pressure = node.left.pressure;

}

} else {

if (node.right.minReg == node.left.minReg+1) {

node.pressure = node.right.pressure + node.left.pressure;

} else {

node.pressure = node.right.pressure;

}

}

```

Figure 2.8: Computation of Register Pressure

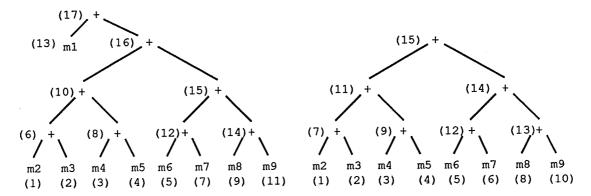

evaluation 2 registers will be live 3 times—after loading m3 (or m4), m2, and m1. The register pressure of the root node is only 1, however, because minReg=3 and the left sub-tree will be evaluated first (without ever having 3 registers live in a normal SU order), and the right sub-tree will be evaluated second, reaching 3 live registers only once—after m5 (or m6). Therefore, the optimal evaluation of the tree (given 3 registers) will incur only one load delay by scheduling the left sub-tree before the right. Had the right been scheduled first, 3 load delays would have occurred.

The decision to spill a node is made when calculating the minReg and pressure values. A node is spilled if its minReg value is equal to the number of available registers

Figure 2.9: Tree with Register Pressure Labels

and its pressure is greater than 2 (the cost of a store and load). If a node has a minReg value greater than the number of available registers, then its child with the greater pressure should be spilled. Spilling information is calculated bottom-up in the tree while calculating minReg and pressure. The algorithm avoids spilling until absolutely necessary or until it is advantageous.

```

if ((node.minReg == Registers and node.pressure > 2)

or node.minReg > Registers) {

if (node.left.pressure > node.right.pressure) {

// Spill node.left;

// Make node.left a Leaf temporary;

// Set node.left.pressure = 1;

// Set node.left.minReg = 1;

// Set node.pressure = node.right.pressure;

// Set node.minReg = node.right.minReg;

} else {

// Spill node.right, etc...

}

```

Loads introduced by spills will not cause pipeline interlocks because they will occur only at a node whose sibling has a minReg value of at least Registers-1. This ensures that the load will be part of a tree whose root has minReg of at least Registers-1. Since this new leaf (spill) node has a minReg of 1 and a register pressure of 1, it cannot increase

the minReg or register pressure of the entire tree. The cost of the spill is restricted to the cost of the store/load, and the interlocks associated with evaluating the sub-tree below the spilled node (which cannot be greater than 2).

### 2.7 Extensions to DLS: Related Work

The DLS algorithm is restricted to considering binary trees with all leaves representing delayed loads. A more realistic machine model must be able to handle unary nodes, leaf instructions without delays, and delayed loads at internal nodes.

Kurlander, Fischer, and Proebsting [KFP92] have extended DLS to optimally handle unary nodes and non-delayed leaf nodes. The improvements are called Extended DLS (EDLS). In addition, they give a simple heuristic for scheduling trees with internal delayed loads.

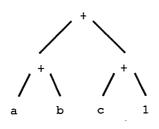

#### 2.7.1 Non-Delayed Leaf Nodes

Not all leaf instructions on real machines incur delay cycles. For instance, the result of a "load immediate" is typically available immediately! Scheduling a tree containing a non-delayed leaf node using DLS will always give a non-interlocking schedule, but it may use too many registers. It is sometimes possible to schedule an expression with non-delayed leaf nodes using only minReg registers. Figure 2.10 shows that (a+b)+(c+1) can be scheduled (without interlocks) using exactly minReg= 3 registers. Figure 2.11 shows, however, that (a+b)+1 requires minReg+1 = 3 registers for a delay free schedule. The expression (a+b)+(c+1) could be scheduled without an extra register because the loadi of 1 could be immediately followed by an instruction using that value.

In the absence of non-delayed leaf nodes, the proof that an extra register is needed

| #  | Schedule       |

|----|----------------|

| 1. | load a, r1     |

| 2. | load b, r2     |

| 3. | load c, r3     |

| 4. | add r1, r2, r2 |

| 5. | loadi 1, r1    |

| 6. | add r3, r1, r1 |

| 7. | add r2, r1, r1 |

Figure 2.10: Delay-Free Schedule using only minReg registers.

| #  | Schedule       |

|----|----------------|

| 1. | load a, r1     |

| 2. | load b, r2     |

| 3. | loadi 1, r3    |

| 4. | add r1, r2, r2 |

| 5. | add r2, r3, r1 |

Figure 2.11: Delay-Free Schedule requiring minReg+1 registers.

for delay-free evaluation followed because any schedule requiring only minReg registers would necessarily have load instructions that were immediately followed by operations using those loaded values. However, if all of the leaf instructions that increase the number of registers in use to minReg are non-delayed instructions, then the additional register is not necessary. This observation leads directly to a linear-time algorithm for determining if an additional register is needed. Every sub-tree will have a flag indicating whether or not that sub-tree can be evaluated optimally without an additional register beyond minReg. This can be computed in a single bottom-up pass of the tree (see Figure 2.12).

Recall that any (sub-)tree can be computed interlock-free with minReg+1 registers (when Delay=1). If the left and right sub-trees each require an identical number of registers (minReg) to be computed, then the entire tree will be given minReg+1 registers.

```

if (isLeaf(node)) {

node.needExtra = isDelayed(node);

} else {

if (node.right.minReg == node.left.minReg) {

node.needExtra = node.right.needExtra AND node.left.needExtra;

} else if (node.right.minReg < node.left.minReg) {

if (node.right.minReg+1 == node.left.minReg) {

node.needExtra = node.right.needExtra OR node.left.needExtra;

} else {

node.needExtra = node.left.needExtra;

} else {

// node.right.minReg > node.left.minReg

// Symmetric to right.minReg < left.minReg case.

}

}</pre>

```

Figure 2.12: Computing the need for an Extra Register with Non-Delayed Leaf Nodes.

This means the sub-tree scheduled first will have minReg+1 registers for its computation, and the DLS algorithm ensures that it will be computed without interlocks. The second sub-tree will have only minReg registers. Therefore, if one sub-tree can be computed without an extra register, it can be computed after the other, and both will proceed interlock-free.

If the minReg values of two sub-trees differ, then their order is determined by normal Sethi-Ullman constraints—the sub-tree with the greater minReg value must be computed first. (The minReg value of the entire tree will be equal to that greater minReg.) Call the two sub-trees left and right and assume without loss of generality that left.minReg > right.minReg. left will be computed before right. If left needs an extra register,

<sup>&</sup>lt;sup>5</sup>The two trees that do not have any delay-free schedules (a single load, and two loads and a single binary operation) will not incur delays when scheduled as the first of two sub-trees. The first instruction of the second sub-tree must fill the (otherwise unfilled) delay slot of the first sub-tree.

then the entire tree must need an extra register since the tree has the same minReg value as the left sub-tree. If left can be computed without an extra register, then it depends on whether or not right can be computed without interlocks given only left.minReg-1 registers. If right.minReg is less than left.minReg-1 then right will have the extra register it needs for DLS delay-free scheduling. If, however, left.minReg-1 does not provide an extra register for right to be computed, then it is necessary to examine whether right needs an extra register (since it is **not** going to get one).

While this algorithm is simple and fast, its utility is debatable. At best it can save a *single* register. It does not find interlock-free schedules that DLS could not find given an extra register.

### 2.7.2 Unary Nodes

Unary operations can be scheduled via a simple extension to ordinary DLS. All unary nodes are scheduled immediately *before* the operations that are going to use the values they compute. Schedule an expression using DLS as if the unary nodes were collapsed into the operands of their parents, and then expand them after scheduling is complete.

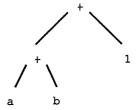

The (small) problem with this is that it too may overuse registers by one. It may be the case that a schedule exists for the expression that would not need minReg+1 registers, but instead could use only minReg. Unfortunately, some of these schedules require a non-contiguous evaluation of the expression, and DLS cannot directly find such evaluations. Figure 2.13 gives an example of a tree that requires only minReg= 4 registers for an optimal schedule, but to do so it requires a non-contiguous evaluation.

Kurlander's linear-time algorithm to find the optimal schedules for trees with unary nodes is somewhat more complicated than the algorithm to handle non-delayed leaves.

| <del></del> | 0111           |

|-------------|----------------|

| #           | Schedule       |

| 1.          | load m1, r1    |

| 2.          | load m2, r2    |

| 3.          | load m3, r3    |

| 4.          | load m4, r4    |

| 5.          | add r1, r2, r2 |

| 6.          | load m5, r1    |

| 7.          | add r3, r4, r4 |

| 8.          | load m6, r3    |

| 9.          | add r2, r4, r4 |

| 10.         | load m7, r2    |

| 11.         | add r1, r3, r3 |

| 12.         | load m8, r1    |

| 13.         | neg r4, r4     |

| 14.         | add r2, r1, r1 |

| 15.         | add r3, r1, r1 |

| 16.         | add r4, r1, r1 |

Figure 2.13: Non-Contiguous Evaluation with Unary Nodes

| #  | With Interlocks    | Without Interlocks |

|----|--------------------|--------------------|

| 1. | load m1, r1        | load m1, r1        |

| 2. | load m2, r2        | load m2, r2        |

| 3. |                    | add regN, regM, r3 |

| 4. | add r1, r2*, r2    | add r1, r2, r2     |

| 5. | add regN, regM, r3 | add r2, r3, r2     |

| 6. | add r2, r3, r2     |                    |

Figure 2.14: Evaluation Orders with Register Variables

His algorithm is capable of finding the optimal non-contiguous evaluations. The detailed algorithm and proof of correctness can be found in [KFP92].

### 2.7.3 Register Variables

As presented, the DLS algorithm cannot handle register variables (i.e., leaf nodes that do not represent load instructions). With register variables, it is not always the case that

leaf nodes allocate registers or that operations will decrease the number of registers in use. An operation that has two register variables for children will *increase* the number of registers in use when evaluated (assuming that the register variables are live after the expression).

The simple expression tree in Figure 2.14 demonstrates that a more powerful algorithm is needed to handle register variables. Normal Sethi-Ullman evaluation would label the left sub-tree with an SU-number of 2 and evaluate it before the right sub-tree with a SU-number of 1. The entire tree would therefore have a SU-number of 2. DLS would indicate that 3 registers would be needed for a delay-free evaluation, and that the left sub-tree's operator would be scheduled before the right's (a Sethi-Ullman ordering). Putting the operators and loads into a DLS-like canonical order gives an evaluation order in which an interlock will occur. Had the right sub-tree's operator been scheduled before the left's, no such interlock would have occurred.

Fortunately, Kurlander's results for unary and non-delayed leaf nodes subsumes the problem of handling register variables. For each operand of an operator that is a register variable, simply decrease the perceived arity of that operator by one. In Figure 2.14 the add of the two register variables should be treated as a non-delayed leaf node. It acts like a non-delayed leaf node since it has no associated delay, and it *increases* the number of temporary registers in use. Kurlander's scheduler would then find the optimal schedule.

### 2.7.4 DAGs, Forests, and Internal Loads

When code is generated or scheduled for an entire basic block it is natural to use a DAG as the intermediate representation because of common sub-expressions. Since optimal

Figure 2.15: Splitting At Internal Loads

code scheduling for DAGs is NP-complete, we prefer to schedule trees. By splitting nodes of a DAG, it is possible to treat a DAG as an ordered forest of trees. A DAG is split by computing shared internal nodes to temporary storage prior to computing ancestor nodes. Proceeding in a bottom-up fashion, evaluating a DAG then reduces to evaluating a sequence of trees (a forest).

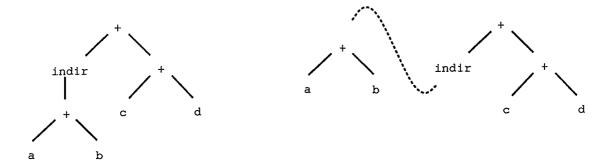

Furthermore, Kurlander [KFP92] has used this splitting idea to handle delayed loads that are internal to a tree (or DAG). Whenever a non-leaf load is encountered, the tree is split so that that load is now at the frontier of the original tree. Figure 2.15 shows the splitting as it would be applied to (a+b)+indir(c+d). From the original tree, a forest of two trees has been created—each with loads only at the leaves. These trees can be handled by DLS and EDLS.

The idea of a canonical order for trees can be extended to forests with corresponding benefits. If two trees are executed in sequence and have no data dependences between them, it is possible to order their operators and loads separately, and then schedule both sets of operators and loads together. This is done by concatenating the operator lists together and the load lists together, and then scheduling these lists such that loads from the second expression are interspersed with the operators of the first expression.

| #   | Without Merging | With Merging   | Comments           |

|-----|-----------------|----------------|--------------------|

| 1.  | load A, r1      | load A, r1     |                    |

| 2.  | load B, r2      | load B, r2     |                    |

| 3.  | load C, r3      | load C, r3     |                    |

| 4.  | load D, r4      | load D, r4     |                    |

| 5.  | add r1, r2, r2  | add r1, r2, r2 |                    |

| 6.  | add r3, r4, r4  | load E, r1     | Start merging A+B. |

| 7.  | add r2, r4, r4  | add r3, r4, r4 |                    |

| 8.  | load E, r1      | load F, r2     |                    |

| 9.  | load F, r2      | add r2, r4, r4 |                    |

| 10. | { NOP }         | add r1, r2, r2 |                    |

| 11. | add r1, r2, r2  | -              |                    |

Figure 2.16: Merging Two Trees in a Forest: (A+B)+(C+D); E+F

The operations of the first tree and the loads of the second tree are moved away from their respective loads and operations, possibly reducing register needs and pipeline interlocks. The right column of Figure 2.16 demonstrates that merging the expressions (A+B)+(C+D) and E+F yields a delay-free schedule requiring only 4 registers (the same number needed by (A+B)+(C+D) alone). This merged schedule avoids the interlock present when E+F is evaluated alone.

Entire basic blocks can also be handled in this fashion. Data dependences between stores and loads in a basic block will limit the ability to shift loads earlier in the schedule. The definition of a canonical order for a basic block must require that loads not be shifted before stores that may affect their value.

### 2.8 Behavior for Delay>1

The optimality results for Delay=1 do not directly extend to greater Delay values. DLS is, however, an excellent heuristic for larger Delay's, retaining its simplicity and linear running time. As a heuristic for instruction scheduling with Delay>1, DLS may require

more than minReg+1 registers to achieve an interlock-free schedule in canonical order. If an interlock-free schedule exists for a given expression, it can be found, however, by using minReg+Delay registers with the DLS canonical form. The same argument made for the optimality of the case Delay=1 shows that the number of registers needed for an interlock-free schedule will never be greater than minReg+Delay. Not all expressions require minReg+Delay registers for an interlock-free schedule—they may have interlock-free schedules requiring fewer registers. For this reason, a heuristic approximation to the DLS algorithm for Delay>1 is to use a DLS-generated canonical order with minReg+Delay registers. This heuristic retains the optimal scheduling results of the minReg+1 case, but may, in a few cases, over-allocate registers. In §2.8.2, we give the lower-bounds on the fewest possible registers needed for an interlock-free schedule when Delay>1.

### 2.8.1 Non-Contiguous Operand Ordering

The Sethi-Ullman algorithm generates code that is *contiguous*. That is, instructions generated for one sub-tree do not mix with the instructions for a sibling sub-tree. The DLS algorithm does not possess this property because the loads from one sub-tree may be mixed with the operations from another. The algorithm does, however, produce schedules that exhibit some contiguity: the loads taken alone, and the operations taken alone do have contiguous orders. It is precisely this property that allows a "divide and conquer" approach that treats each sub-tree separately.

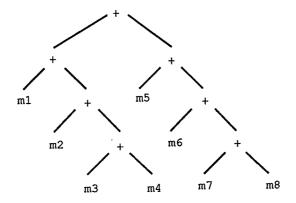

It is not always possible to generate code with this contiguous operation/load property and still have the code be optimal with respect to pipeline interlocks and register usage if Delay is greater than 1. Figure 2.17 is the *smallest* example of a tree that does

Figure 2.17: Non-Contiguous Optimal Evaluation for Delay=2.

not have an optimal schedule in which the operations/loads are ordered contiguously for Delay=2—the tree is labeled with the optimal evaluation order.

Lacking the contiguous property for optimal results, it is unlikely that a linear time algorithm exists for optimally scheduling trees with Delay>1. Whether the optimal algorithm is polynomial-time or exponential-time, it will be much more expensive to run than DLS (and in practice not all that more effective).

### 2.8.2 Register Bounds

The fact that minReg+Delay registers and a canonical ordering will always produce a delay-free schedule (when one exists) gives an upper-bound on the number of registers necessary to find such an evaluation. The optimality proof in §2.5.3 gives a lower (and upper) bound of minReg+Delay for the case where Delay=1. The previous section showed that minReg+Delay is *not* a lower bound when Delay> 1.

Given any Sethi-Ullman order evaluation of an expression, it is not difficult to show,

however, that minReg+[Delay/2] is a lower bound on the registers needed for delay-free evaluation when put into canonical form (when Delay> 1). Given the canonical evaluation order with exactly minReg registers, it must be the case that some operation immediately follows the load of one of its operands. Adding a single register shifts the loads earlier, and operations later in the schedule. For each additional register, each load moves at most one instruction earlier in the schedule and each operation moves at most one instruction later. (Loads in the initial (non-alternating) sequence of loads do not move at all—likewise for the operations in the latter part of the schedule.) Thus, the addition of each register can move a load/operation pair at most two instructions further apart.

Therefore, if Delay instructions are necessary to fill a delay slot, and each register will move at most 2 instructions between any pair, it will be necessary to use a minimum of [Delay/2] registers in addition to the original minReg.

It is possible to find the minimal number of registers needed for a particular combination of operation and load orders in linear time. This can be done by computing the schedule (in canonical order) for each possible number of registers. Starting with minReg+Delay-1 registers and working down, the canonical orders are created and tested to make certain that the loads are separated from their parent operations by at least Delay instructions. Because the lower bound on number of registers for a legal canonical order is minReg+[Delay/2], this process will require at most [Delay/2] iterations. With this inexpensive extra step, it is possible to further fine-tune DLS to use even fewer registers in many cases when Delay>1.

|       | DLS       | DLS         |                        | % DLS   |

|-------|-----------|-------------|------------------------|---------|

| Delay | Optimal   | Sub-Optimal | $\operatorname{Total}$ | Optimal |

| 2     | 1,015,481 | 17,930      | 1,033,411              | 98.3    |

| 3     | 1,015,481 | 17,930      | 1,033,411              | 98.3    |

| 4     | 1,007,509 | 25,902      | 1,033,411              | 97.5    |

| 5     | 1,007,509 | 25,902      | 1,033,411              | 97.5    |

| 6     | 1,007,511 | 25,900      | 1,033,411              | 97.5    |

| 7     | 1,007,535 | 25,876      | 1,033,411              | 97.5    |

| 8     | 1,007,703 | 25,708      | 1,033,411              | 97.5    |

| 9     | 1,008,631 | 24,780      | 1,033,411              | 97.6    |

Figure 2.18: Heuristic Results for All Trees of 25 or Fewer Nodes

### 2.8.3 Empirical Results

The DLS algorithm works extremely well as a heuristic for Delay values greater than 1. By enumerating all possible expression trees of 25 or fewer nodes, and testing the algorithm against an exhaustive search algorithm, the effectiveness of the algorithm as a heuristic can be easily verified. We ran trials for Delay's of 2 through 9 to obtain the results given in Figure 2.18. A schedule produced by DLS is considered sub-optimal if it uses R registers but contains no interlocks when there exists a non-interlocking schedule needing fewer than R registers, or if it uses R registers and contains I interlocks when there exists a schedule using R registers that contains fewer than I interlocks. DLS never uses more than minReg+Delay registers and produces a non-interlocking schedule for all but a finite number of trees for any given Delay.

### 2.8.4 Anomaly

Using DLS for Delay=2, an interesting (and surprising) counter-intuitive result has been found. It is possible for an expression tree to have a sub-tree whose optimal (delay-free) evaluation requires *more* registers than the entire tree's optimal evaluation. The left

Figure 2.19: Anomaly for Delay=2. Entire Tree Needs 5 Registers—Right Sub-tree Alone Needs 6. (The respective optimal evaluation orders are given.)

tree of Figure 2.19 can be evaluated optimally with 5 registers, however its right sub-tree taken alone requires 6 registers for a delay-free evaluation. (No delay-free evaluation exists using fewer than 6 registers, and DLS will find this optimal evaluation.) Note also that the full tree has minReg=4, and Delay=2, yet it needs only 5 registers for a spill-free, interlock-free evaluation.

#### 2.9 Conclusion

The DLS algorithm presented performs optimal code scheduling and optimal register allocation in linear time for binary expression trees with load delays of 1 cycle. The algorithm can be modified to predict optimal locations for register spilling. Unlike other code scheduling algorithms, it does not suffer from phase-ordering problems with register allocation.

Extensions to the binary tree algorithm allow DLS to optimally schedule trees with non-delayed load instructions and unary operations. DLS can handle (non-shared) register variables optimally. Heuristics for splitting trees and DAGs into forests of

trees allow DLS to schedule entire basic blocks. Basic block scheduling is improved by extending canonical orders to forests of trees that can be merged to fill delay slots.

Furthermore, DLS performs as an excellent heuristic for load delays greater than 1 and can be readily extended to handle tree forests derived from DAGs. As a heuristic it retains its coordination of register allocation and code scheduling without sacrificing its run-time efficiency or conceptual simplicity.

## Chapter 3

# Probabilistic Register Allocation

Register allocation is the code generation phase that determines which values should be held in machine registers at different points in the program. Most CISC machines (e.g., VAX) can have instruction operands accessed either directly from registers or from memory. The accesses from memory take more cycles than direct register accesses. Most RISC machines cannot access memory except through explicit loads. In either machine class, a value that can be kept in a register rather than memory will be cheaper to manipulate.

Machines, however, have only a very limited number of registers. Modern RISC architectures, like the MIPS R2000 or the SPARC, have fewer than 32 general purpose integer registers available for use. CISC processors typically have even fewer. Therefore, a compiler must often choose between competing values that can be held profitably in registers. Values that are live at a particular point in the program that are not allocated registers must be held in main memory.

Register allocation can be done globally as well as locally. Local allocators make allocation decisions within the limited range of a single basic block. Global allocators

operate at the procedure level—across basic blocks. Often global allocation will allocate a register to a heavily used variable for an entire procedure. To achieve a profitable final allocation, both local and global schemes may choose to keep a particular value in a register at some points in the code, and in memory at others.

For instance, a value may be heavily used in one loop (that will presumably execute often) but may not be used at all in another loop. If registers are scarce, a global allocator may decide to allocate a register to the value only for the loop in which it is heavily used. Not allocating it a register in the other loop will leave the register available to another value that is used in that loop. A local allocator makes similar allocations over different regions of a basic block.

A closely related problem is that of register assignment. Register assignment is the problem of determining which actual physical register will hold a particular value (that has previously been allocated a register).

### 3.1 Overview

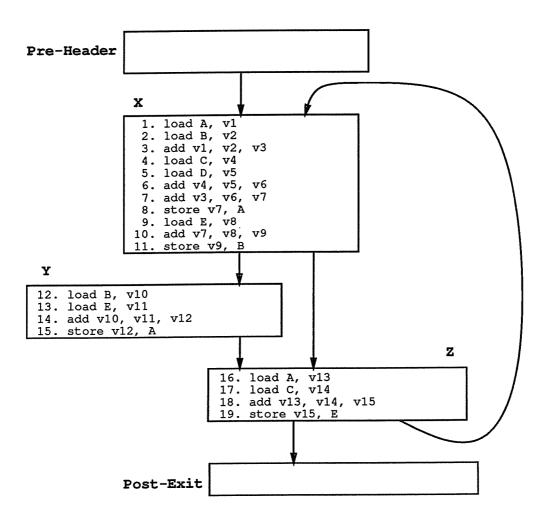

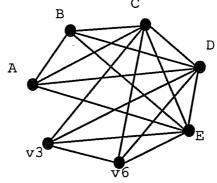

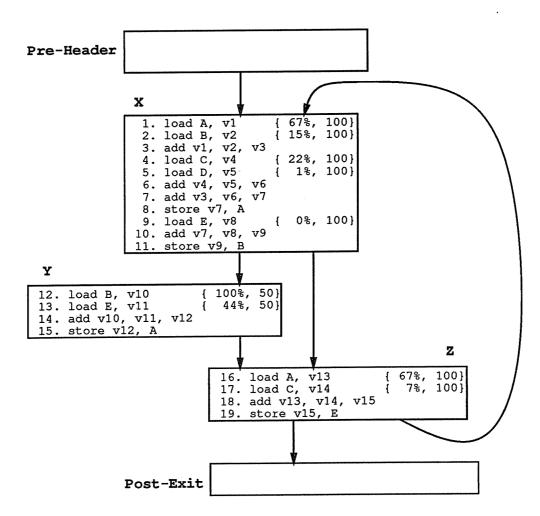

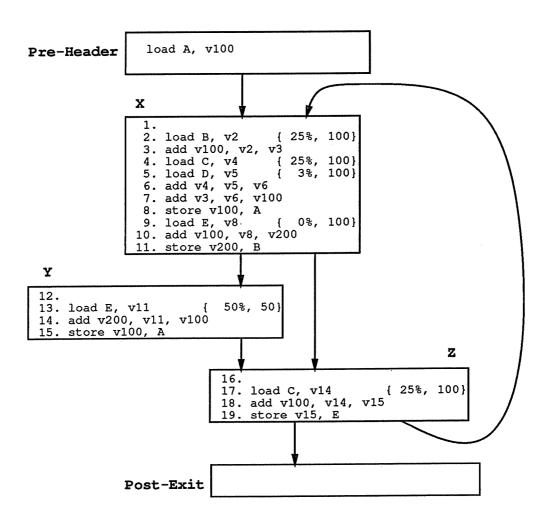

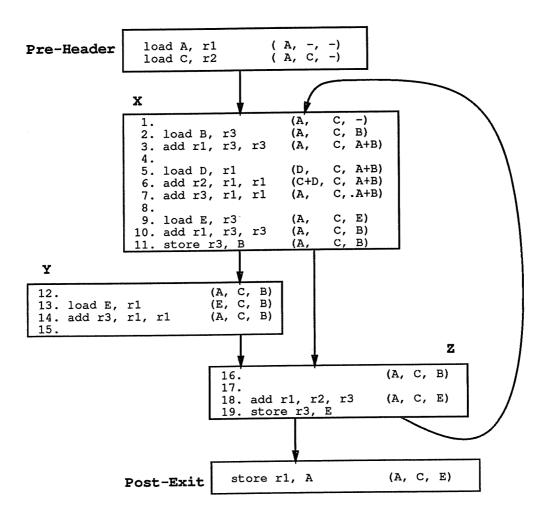

The dominant paradigm in modern global register allocation is graph coloring ([CH90], [CAC+81], [BCKT89], [LH86]). Unfortunately, graph coloring does not really address the issue of register allocation, but rather the related issue of register assignment. That is, graph coloring tells us how to assign registers so that simultaneously live values aren't assigned the same register. The harder problem—which values to put in *some* register—is not directly addressed. Hence there is always a spilling heuristic that reduces register demand until coloring (register assignment) can succeed.