# Hardware Support for Interprocess Communication

by

Umakishore Ramachandran

Computer Sciences Technical Report #667 September, 1986

|     |  |  |  | , |   |

|-----|--|--|--|---|---|

|     |  |  |  |   | • |

|     |  |  |  |   |   |

|     |  |  |  |   |   |

| i d |  |  |  |   |   |

|     |  |  |  |   |   |

|     |  |  |  |   |   |

|     |  |  |  |   |   |

|     |  |  |  |   |   |

|     |  |  |  |   | • |

|     |  |  |  |   |   |

# Hardware Support

for

# Interprocess Communication

by

Umakishore Ramachandran

A thesis submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy (Computer Sciences)

at the UNIVERSITY OF WISCONSIN - MADISON

August 1986

© Copyright by Umakishore Ramachandran 1986

All Rights Reserved

## **Abstract**

Access to system services in traditional uniprocessor operating systems are requested via protected procedure calls, whereas in message-based operating systems they are requested via message passing. Since message exchange is the basic kernel mechanism in message-based operating systems, the performance of the system depends crucially on the rate of message exchange. The advent of local area networking has sparked interest in message-based operating systems.

One of the main problems in existing multicomputer message-based operating systems has been the slowness of interprocess communication. This speed limitation is often due to the processing overhead associated with message passing. Previous studies implicitly assume that only communication between processes on different nodes in the network is expensive. However, we show that there is considerable processing overhead for local communication as well. Therefore, we propose hardware support in the form of a message coprocessor.

Our solution to the message-passing problem has two components: a software partition, and a hardware organization. To determine an effective solution we followed a three-step process: First, we profiled the kernels of four operating systems to identify the major components of system overhead in message passing. The results suggested a partitioning of the software between the host and the message coprocessor. Second, we implemented such a partition on a multiprocessor and measured its performance. Based on these results, we proposed bus primitives for supporting the interactions between the host, the message coprocessor, and the network devices. We designed the bus in detail to show the feasibility of the primitives from the point of

view of hardware implementation. Through the simplicity of the design, we show that our bus proposal is cost effective in this environment. Finally, we used Timed Petri nets to model and analyze several system architectures and show the effectiveness of our software partition and hardware organization for solving the message-passing problem.

## Acknowledgements

Marv Solomon, my advisor, has been a perennial source of inspiration and encouragement ever since I started working on my Ph. D. I will always admire him for his astute thinking and impeccable clarity in communicating his ideas. Let me be real original and simply say thanks to convey a feeling for which I have no other words!

The extent to which Mary Vernon took interest in my research and gave guidance and inspiration deserves a very special mention. She taught me all I know about Petri nets and analytical modeling. Jim Goodman was mainly instrumental in convincing me to stay on for a Ph. D (and lose mega-bucks that I could have otherwise earned!) during my uncertain early years here in Madison. I feel extremely grateful to all the faculty for the help and advice I got for free! I always love talking to Larry Landweber and Dave DeWitt, except when they bug me about SMTP bugs!

My special thanks to IBM — in particular Robin Williams and Roger Haskin — for letting me use 925 as a test-bed for my experiments. Thanks to Roger for losing in tennis occasionally to boost my morale! Jim Wyllie taught me juggling but for which my education would still be incomplete! My thanks to Sten Andler, Jon Reinke, Wayne Sawdon, Dan McNabb, Wil Plouffe, and Mike Goodfellow for making my stay in IBM extremely worthwhile. Thanks to Don Fiehman for keeping my 925s alive and kicking!

I would like to acknowledge Bellcore — in particular Mike Lesk, Tom Raleigh, Prem-Kumar, and Hikyu Lee — for allowing me to experiment with Jasmin kernel.

I have some great buddies but for whom I would have finished my thesis eons back and gone! In recent times, Tad, Al, Artsy, and Toby top the list for providing ample

distraction. Seriously, life is not going to be as much fun without you guys. Thanks for everything (including the use of workstations). Despite not being in Madison, Hari provided me with long-distance encouragement. Rana was a fun guy to have around when mindless entertainment was the need of the hour! Prasun, Rajiv, Anil, Tarak, Matthew, Sridhar, Ravi, Chang, Yang, Mohan, and Erez are just a few who made my stay in Madison very pleasant. Thanks to Mr. "Beebs" and his wrecking crew in the basement for all the help! Thanks to Sheryl for her pleasant smile any time you need one.

My parents were a source of immense moral support these last few months. They put up with my impossible schedules with cheer and understanding. I feel funny even attempting to thank my loving wife Vasanthi! Simply stated, I owe everything to her.

# **Table of Contents**

| Abstract                                    | ii |

|---------------------------------------------|----|

| Acknowledgements                            | iv |

| Chapter 1: Introduction                     | 1  |

| 1.1 Message Based Operating Systems         | 3  |

| 1.2 The Problem                             | 4  |

| 1.3 Goals                                   | 6  |

| 1.4 Description of Approach                 | 8  |

| 1.5 Thesis Overview                         | 9  |

| Chapter 2: Related Work                     | 10 |

| 2.1 Overview                                | 10 |

| 2.2 Processor Architecture                  | 11 |

| 2.3 Network Interfaces                      | 14 |

| 2.4 Protocol Processors                     | 15 |

| 2.5 Multiprocessor Architecture             | 16 |

| 2.5.1 Cm*                                   | 16 |

| 2.5.2 Auragen 4000                          | 17 |

| 2.5.3 Butterfly Multiprocessor System       | 18 |

| 2.5.4 Discussion                            | 19 |

| 2.6 Bus Architectures                       | 21 |

| 2.6.1 VMEbus                                | 22 |

| 2.6.2 Multibus II                           | 22 |

| 2.6.3 Futurebus                             | 23 |

| 2.6.4 Nanobus                               | 23 |

| 2.6.5 SB8000                                | 24 |

| 2.6.6 Discussion                            | 24 |

| 2.7 Discussion                              | 26 |

| Chapter 3: Measurements of Existing Systems | 27 |

| 3.1 Overview                                | 27 |

| 3.2 IPC Semantics                           | 28 |

| 3.2.1 Connection Oriented Communication     | 28 |

| 3.2.2 Message Size and Kernel Buffering     | 30 |

6.3 Workload Description .....

87

viii

| A.4 Micro-routines           | 166 |

|------------------------------|-----|

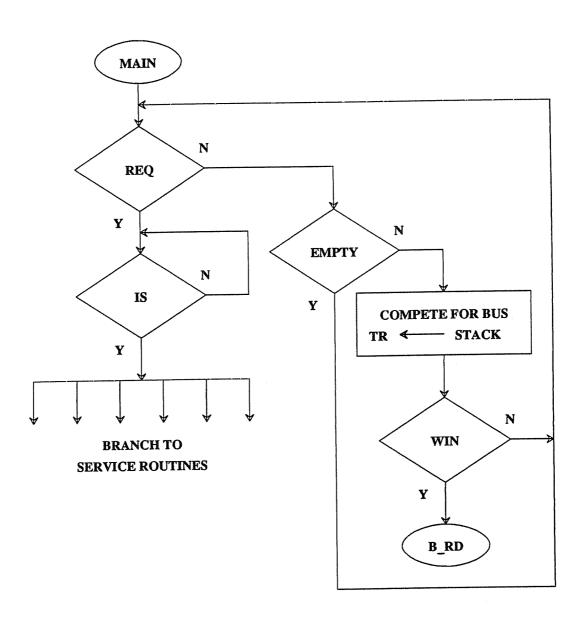

| A.4.1 Main Routine           | 167 |

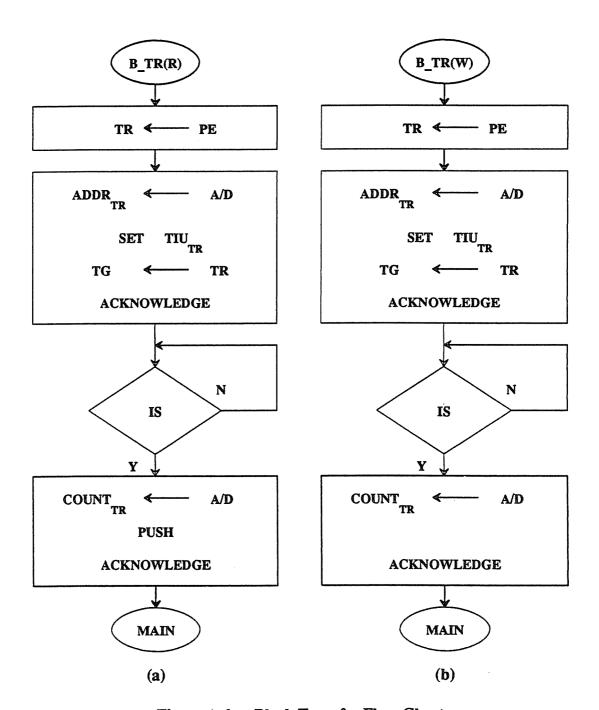

| A.4.2 Block Transfer         | 167 |

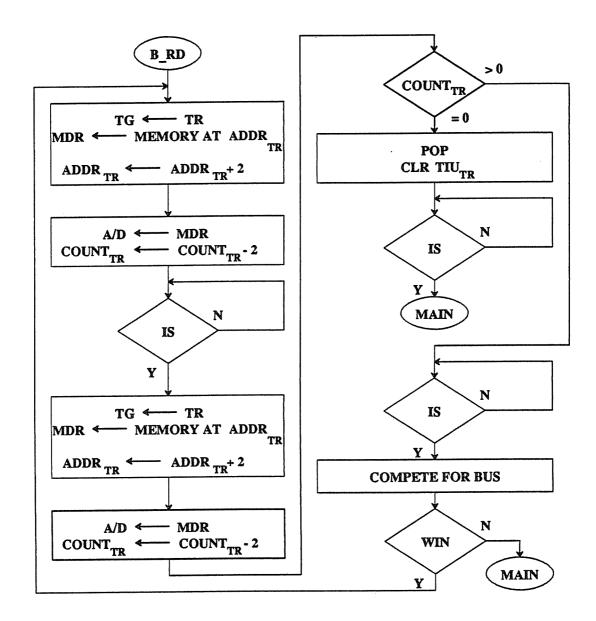

| A.4.3 Block Read Data        | 170 |

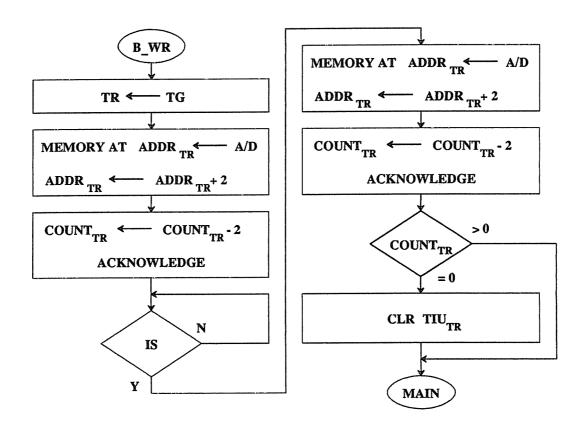

| A.4.4 Block Write Data       | 170 |

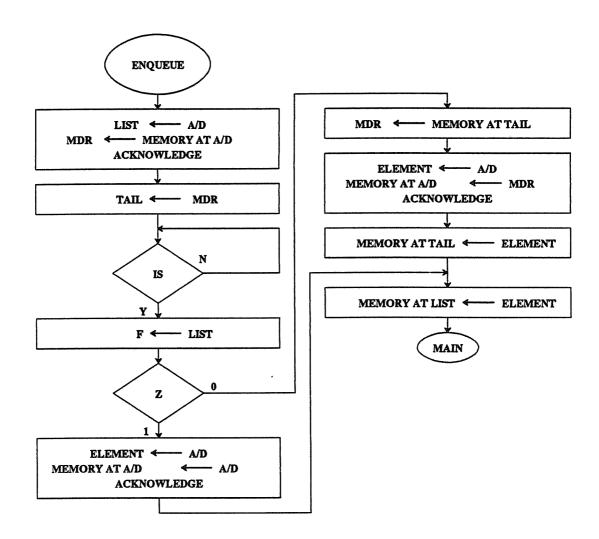

| A.4.5 Enqueue Control Block  | 172 |

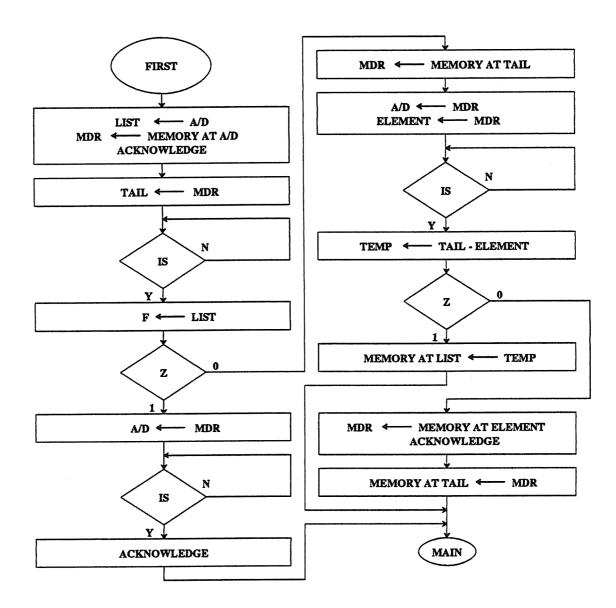

| A.4.6 First Control Block    | 174 |

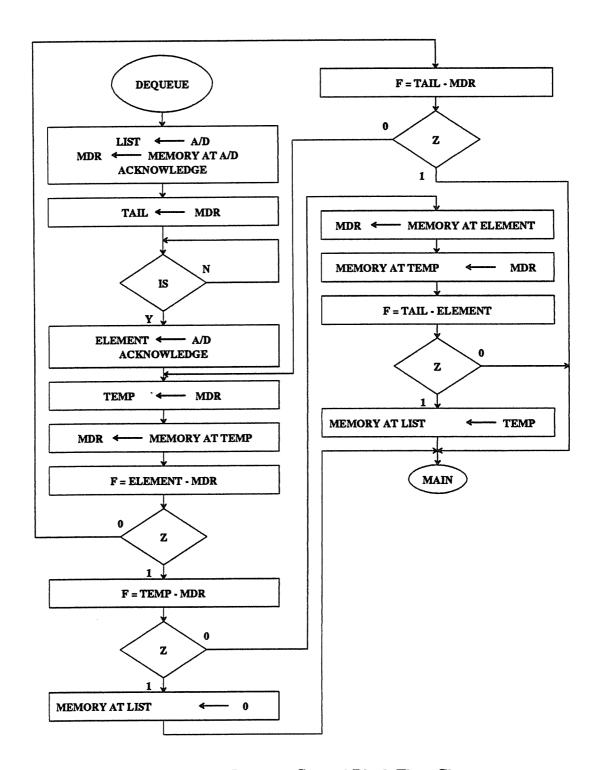

| A.4.7 Dequeue Control Block  | 17: |

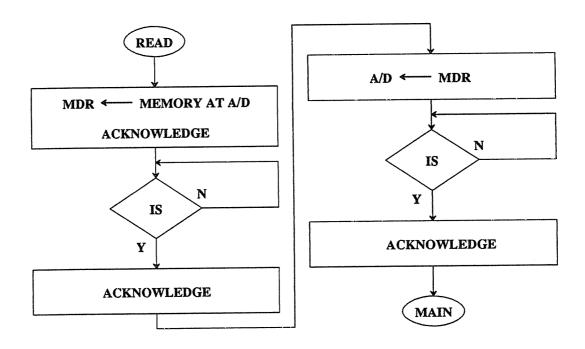

| A.4.8 READ/WRITE             | 178 |

| A.5 Error Conditions         | 179 |

| A.5.1 Block requests         | 180 |

| A.5.2 Queue manipulation     | 18  |

| A.5.3 Non-programming Errors | 183 |

| A.6 Summary                  | 182 |

| Pafarances                   | 183 |

# **List of Figures**

|                                                     | 1  |

|-----------------------------------------------------|----|

| Figure 1.1 — Distributed System                     | 1  |

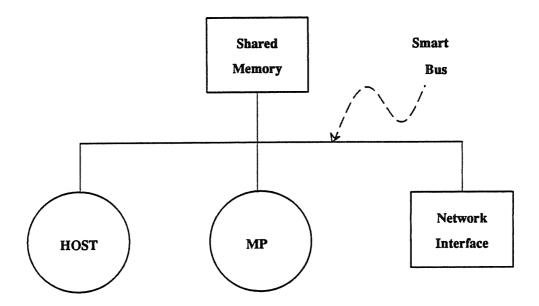

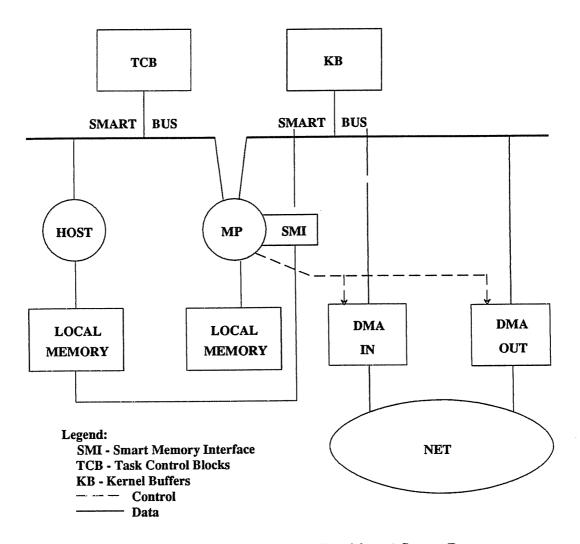

| Figure 1.2 — Node Architecture                      | 6  |

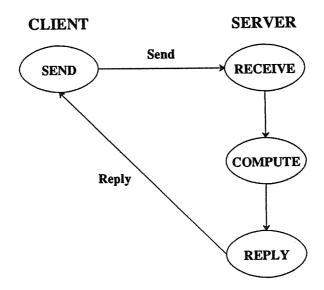

| Figure 4.1 — Task-Kernel Interface                  | 47 |

| Figure 4.2 — Communication Scenario in 925          | 47 |

| Figure 4.3 — 925 Implementation                     | 50 |

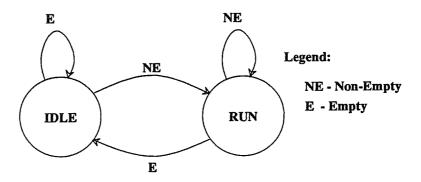

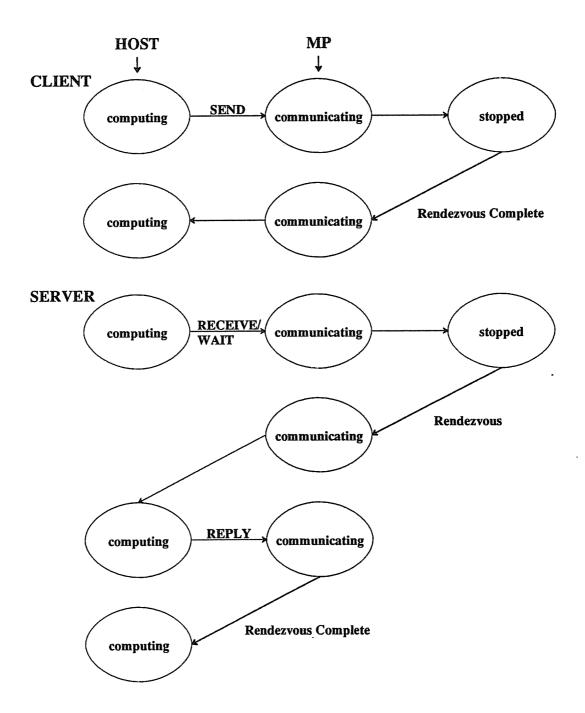

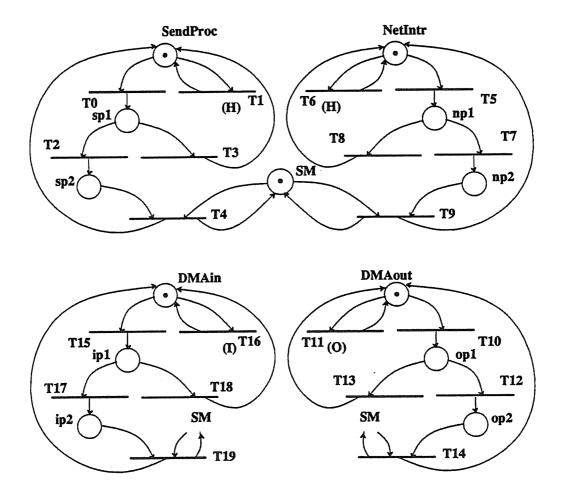

| Figure 4.4 — Processor States: Host                 | 51 |

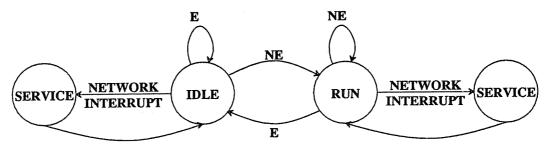

| Figure 4.5 — Processor States: MP                   | 52 |

| Figure 4.6 — Blocking Remote Invocation Send        | 53 |

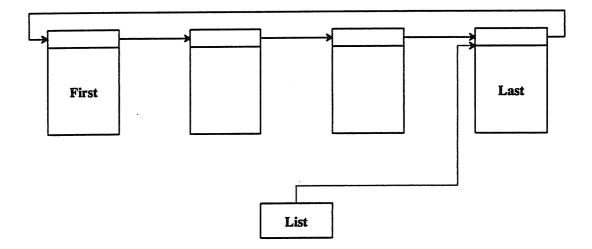

| Figure 5.1 — Queue Data Structure                   | 58 |

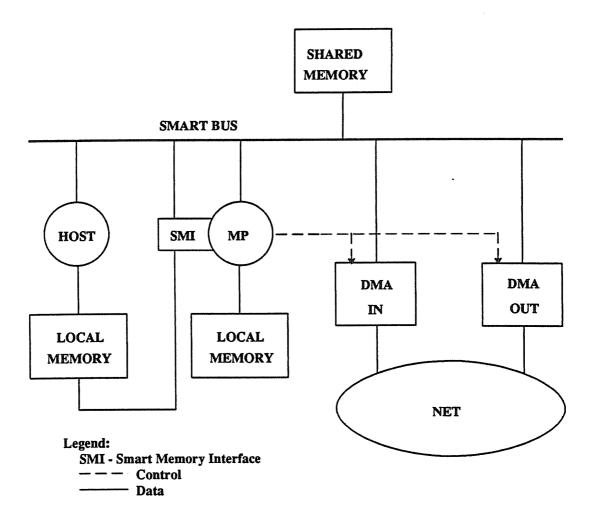

| Figure 5.2 — Smart Bus                              | 63 |

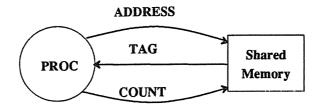

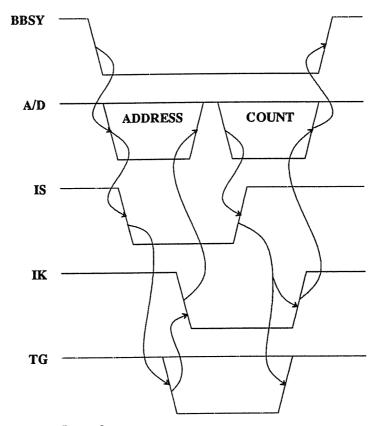

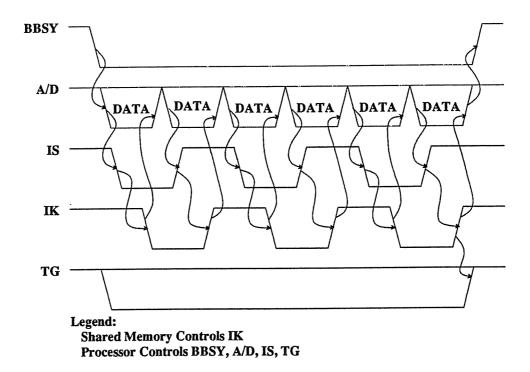

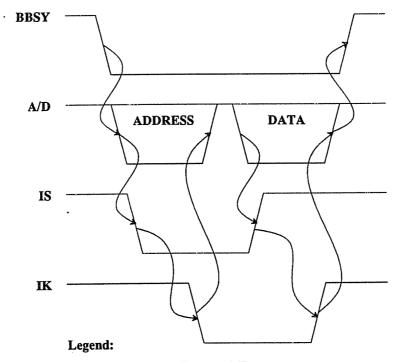

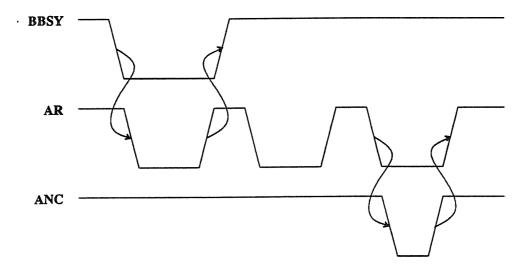

| Figure 5.3 — Block Transfer                         | 67 |

| Figure 5.4 — Block Transfer Timing                  | 67 |

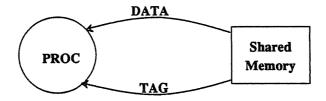

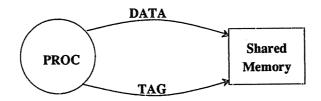

| Figure 5.5 — Block Read Data                        | 67 |

| Figure 5.6 — Block Read Data Timing                 | 67 |

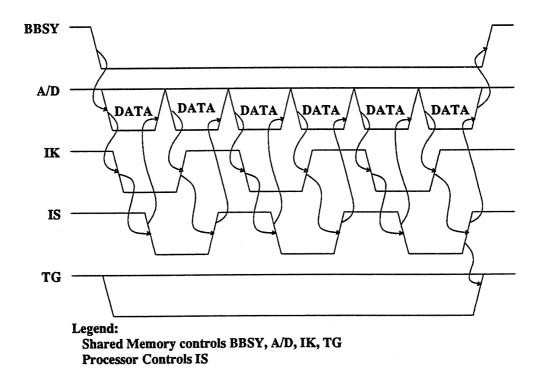

| Figure 5.7 — Block Write Data                       | 69 |

| Figure 5.8 — Block Write Data Timing                | 69 |

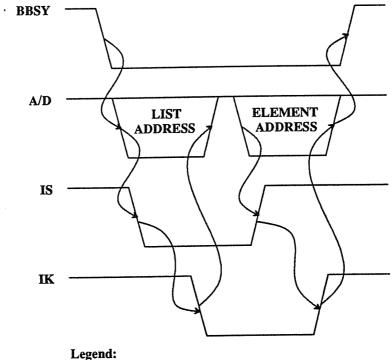

| Figure 5.9 — Enqueue/Dequeue Control Block          | 71 |

| Figure 5.10 — Enqueue/Dequeue Control Block Timing  | 71 |

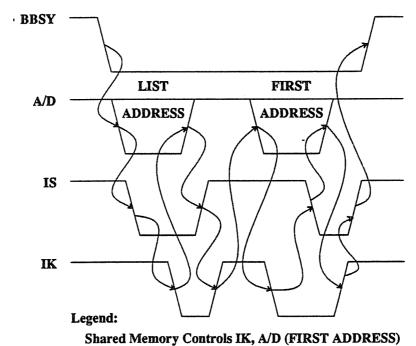

| Figure 5.11 — First Control Block                   | 72 |

| Figure 5.12 — First Control Block Timing            | 72 |

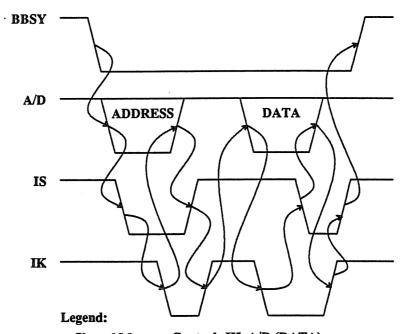

| Figure 5.13 — Read                                  | 74 |

| Figure 5.14 — Read Timing                           | 74 |

| Figure 5.15 — Write                                 | 74 |

| Figure 5.16 — Write Timing                          | 74 |

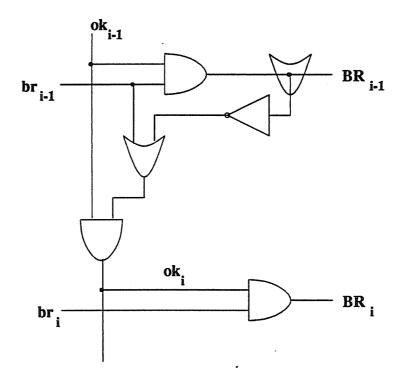

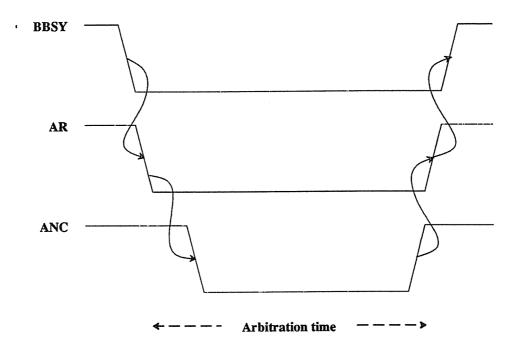

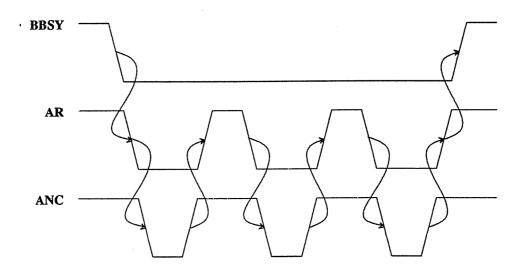

| Figure 5.17 — Taub's Arbitration Circuit            | 76 |

| Figure 5.18 — Smart Bus Arbitration                 | 76 |

| Figure 5.19 — Extended Bus Master                   | 76 |

| Figure 5.20 — Delayed Bus Request                   | 79 |

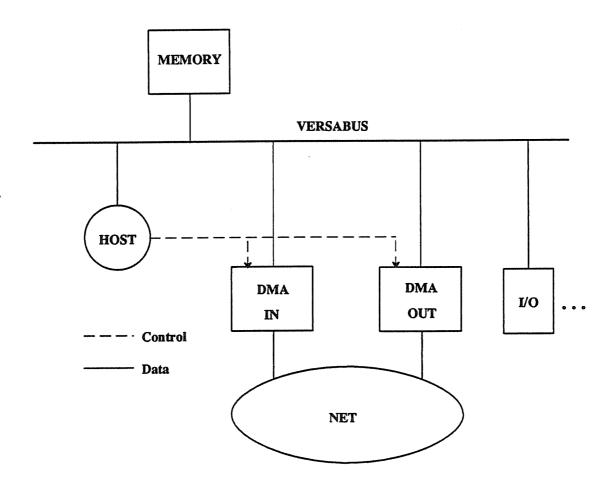

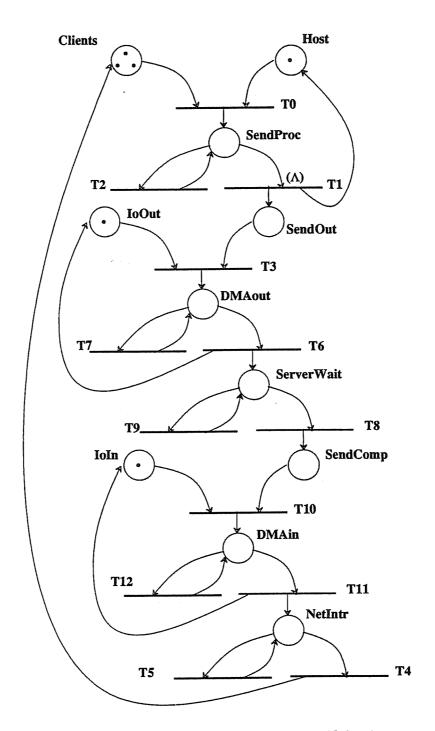

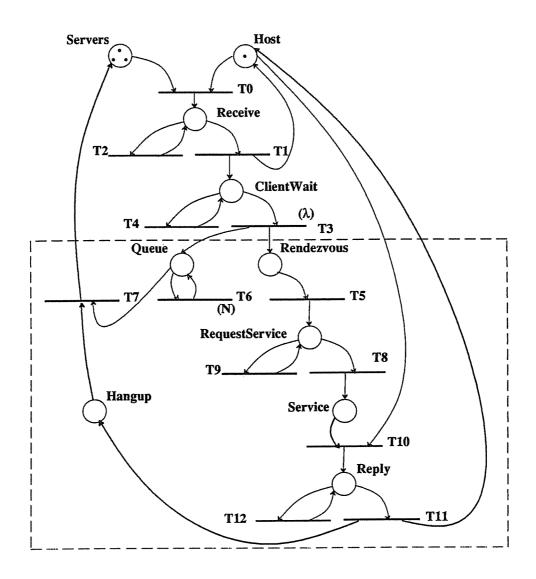

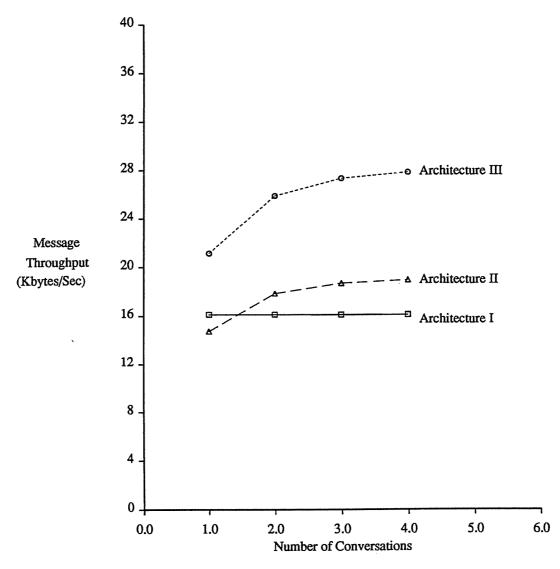

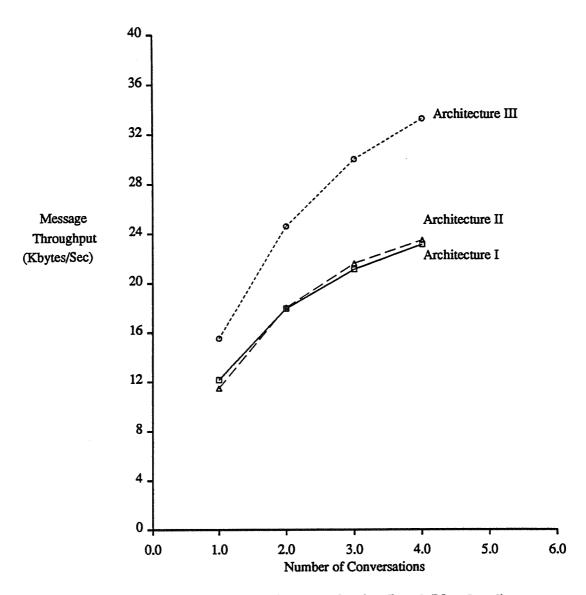

| Figure 6.1 — Architecture I: Uniprocessor           | 83 |

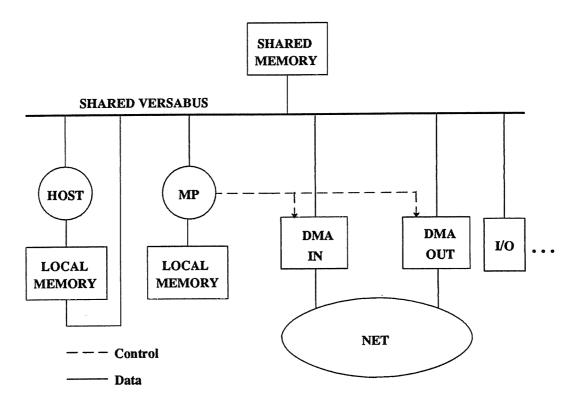

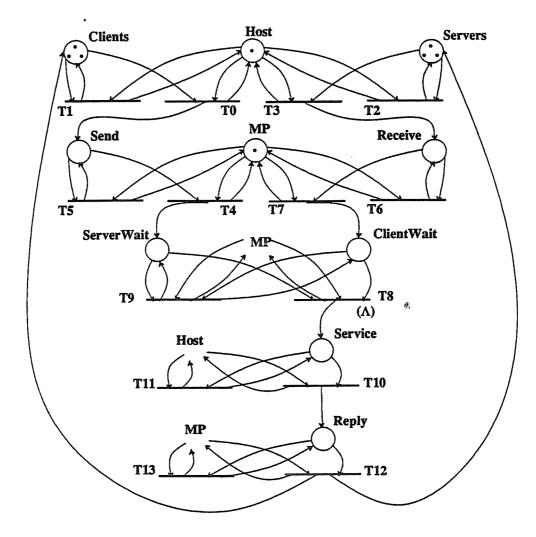

| Figure 6.2 — Architecture II: Message Coprocessor   | 84 |

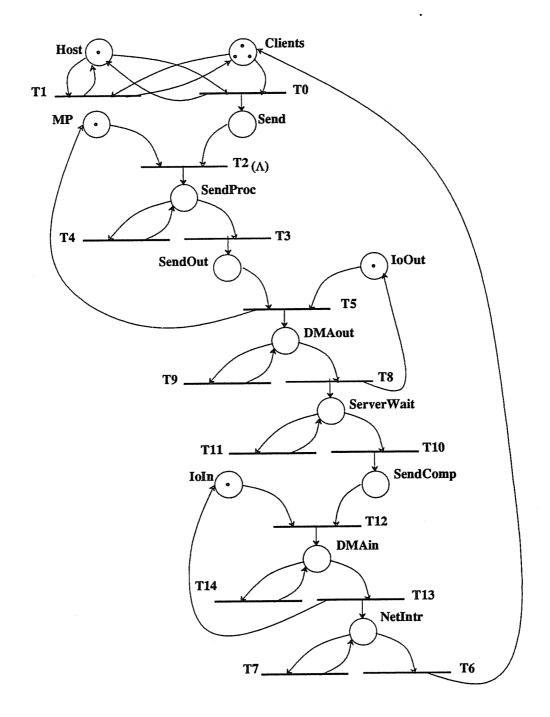

| Figure 6.3 — Architecture III: Smart Bus            | 85 |

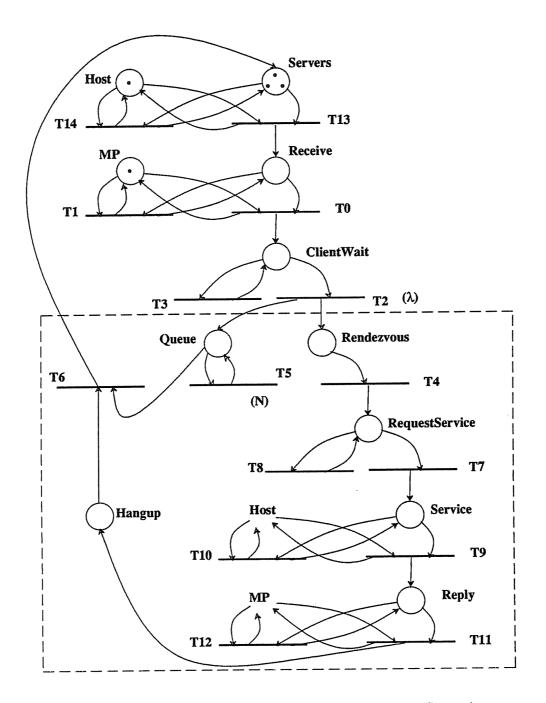

| Figure 6.4 — Architecture IV: Partitioned Smart Bus | 86 |

| Figure 6.5 — Workload                               | 88 |

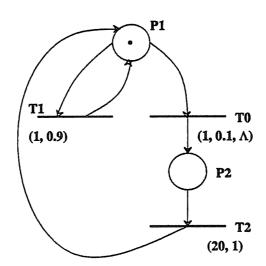

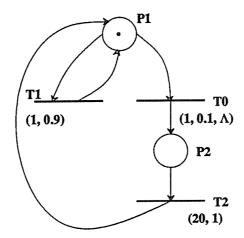

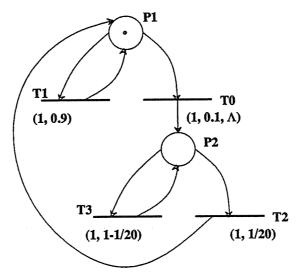

| Figure 6.6 — Petri Net Example                      | 91 |

| Figure 6.7 — Modeling Large Constant Delays         | 94 |

| Figure 6.8 — Resource contention                                 | 96  |

|------------------------------------------------------------------|-----|

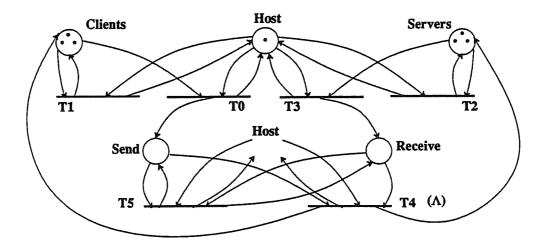

| Figure 6.9 — Architecture I: Local                               | 100 |

| Figure 6.10 — Architecture I: Non-local (Client)                 | 103 |

| Figure 6.11 — Architecture I: Non-local (Server)                 | 106 |

| Figure 6.12 — Architectures II, III, IV: Local                   | 109 |

| Figure 6.13 — Architectures II, III, IV: Non-local (Client)      | 112 |

| Figure 6.14 — Architectures II, III, IV: Non-local (Server)      | 115 |

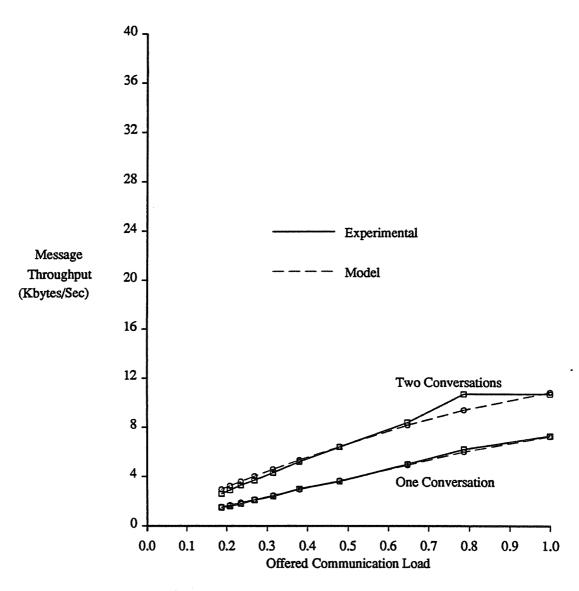

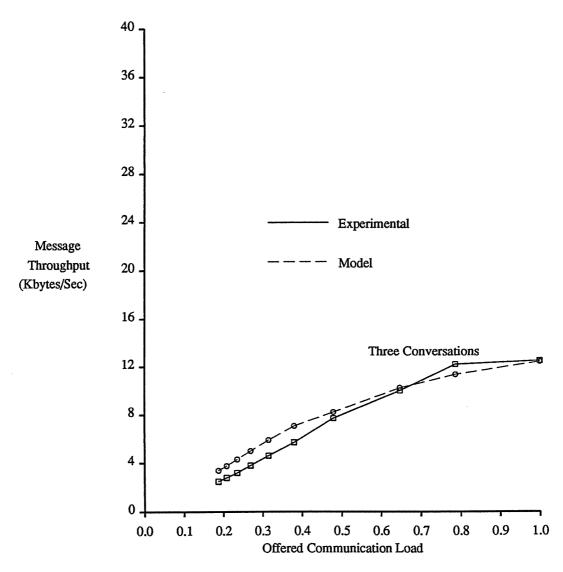

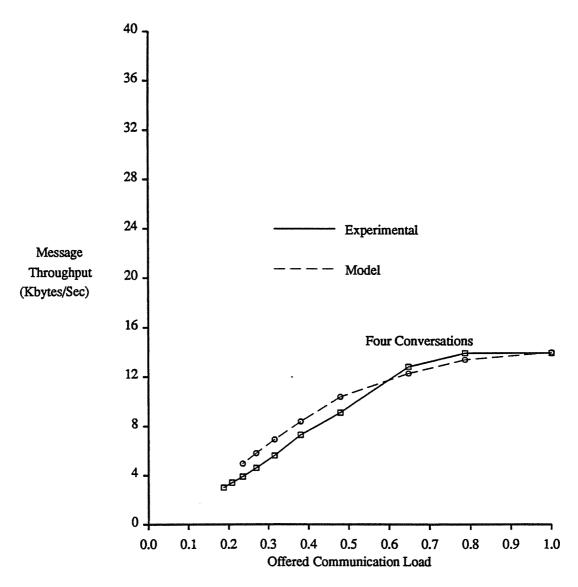

| Figure 6.15(a) — Model Validation                                | 128 |

| Figure 6.15(b) — Model Validation                                | 128 |

| Figure 6.15(c) — Model Validation                                | 128 |

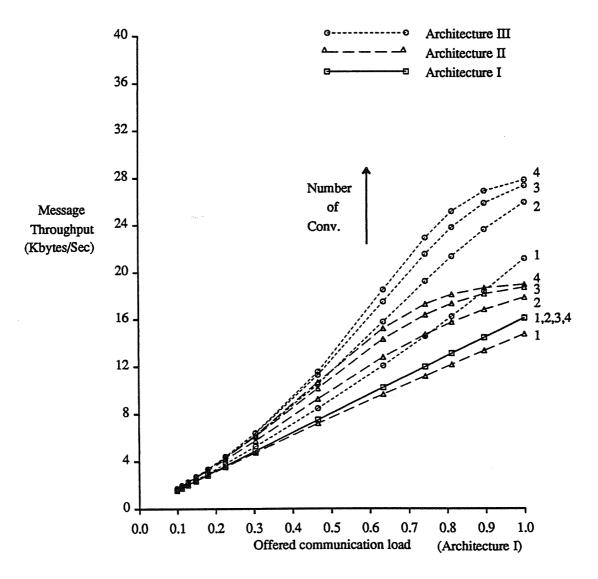

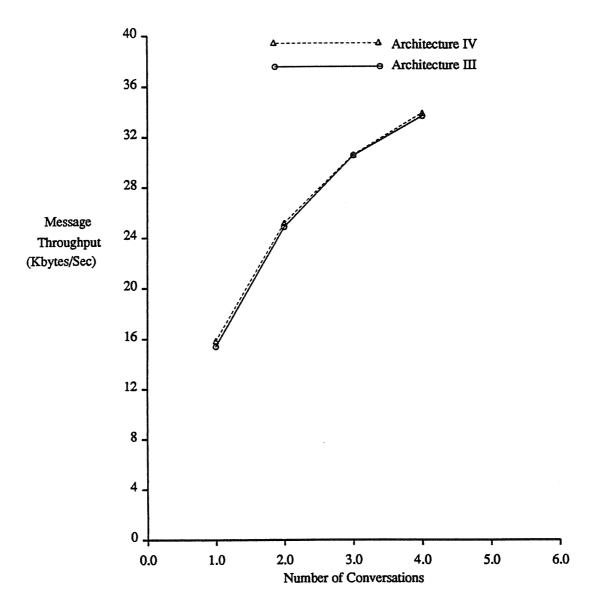

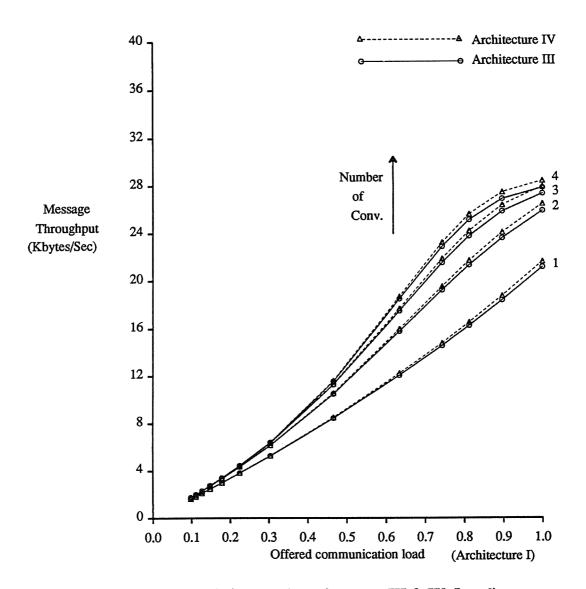

| Figure 6.17(a) — Maximum Communication Load (Local)              | 131 |

| Figure 6.17(b) — Maximum Communication Load (Non-local)          | 131 |

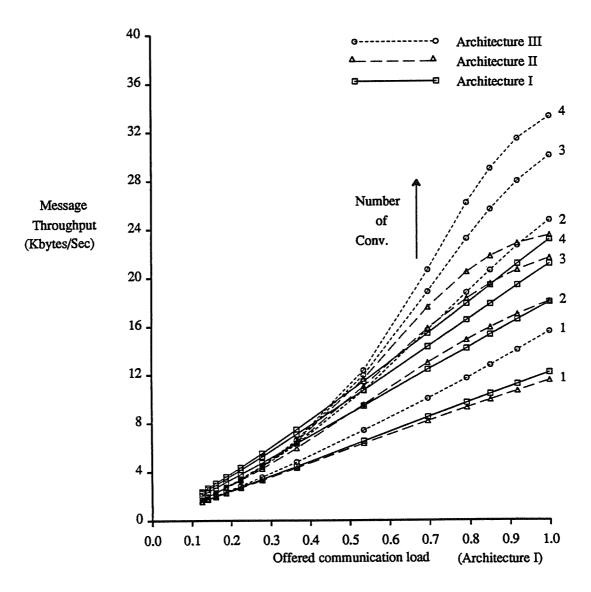

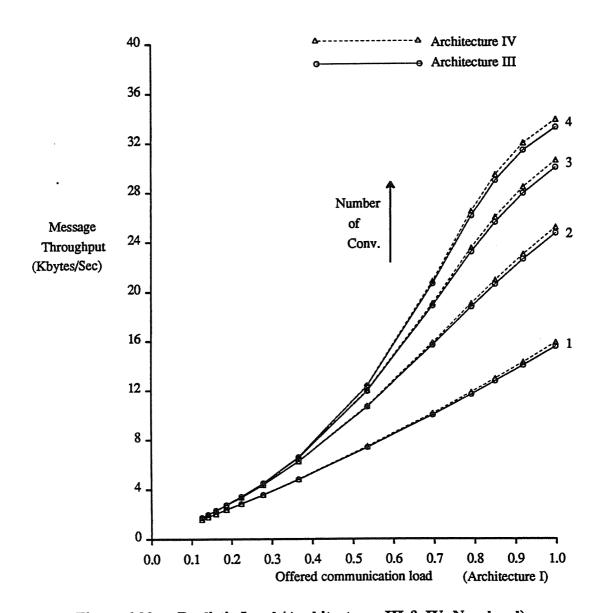

| Figure 6.18 — Realistic Workload (Local)                         | 136 |

| Figure 6.19 — Realistic Workload (Non-local)                     | 138 |

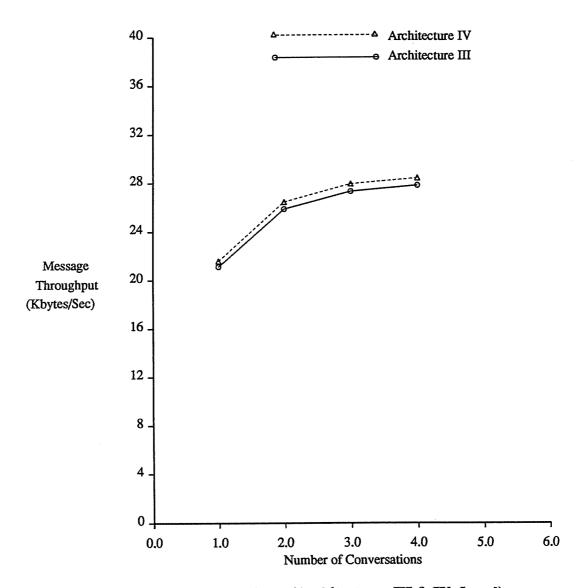

| Figure 6.20 — Maximum Load (Architectures III & IV: Local)       | 138 |

| Figure 6.21 — Maximum Load (Architectures III & IV: Non-local)   | 138 |

| Figure 6.22 — Realistic Load (Architectures III & IV: Local)     | 138 |

| Figure 6.23 — Realistic Load (Architectures III & IV: Non-local) | 138 |

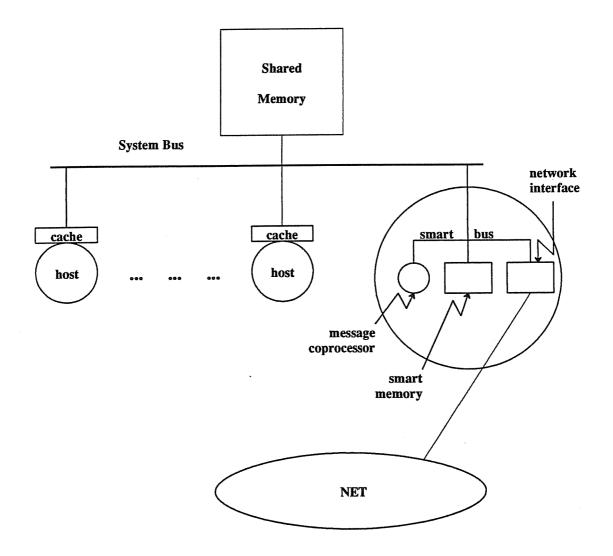

| Figure 7.1 — Shared Memory Multiprocessors                       | 155 |

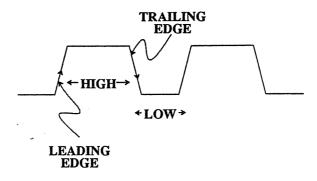

| Figure A.1 — System Clock                                        | 158 |

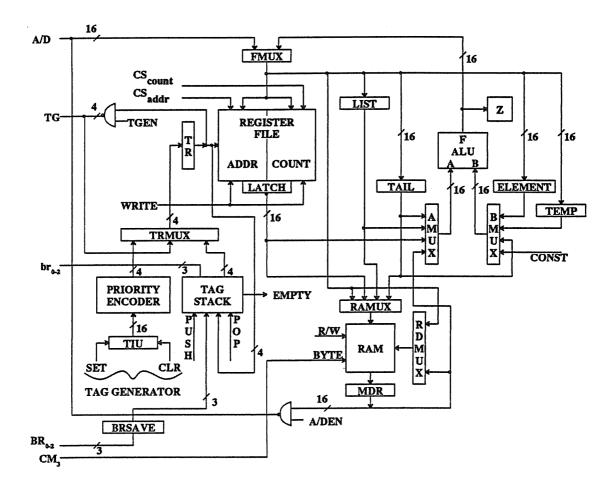

| Figure A.2 — Data Path                                           | 159 |

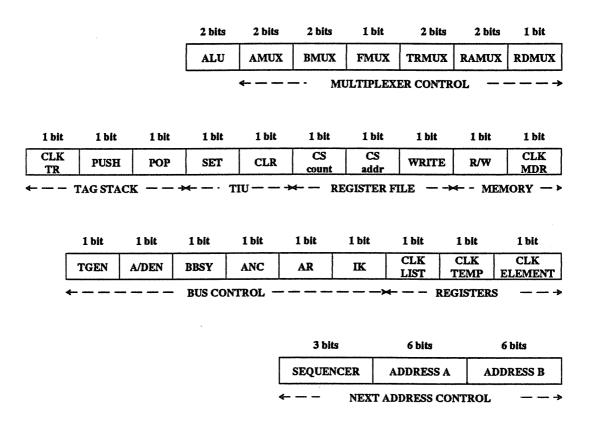

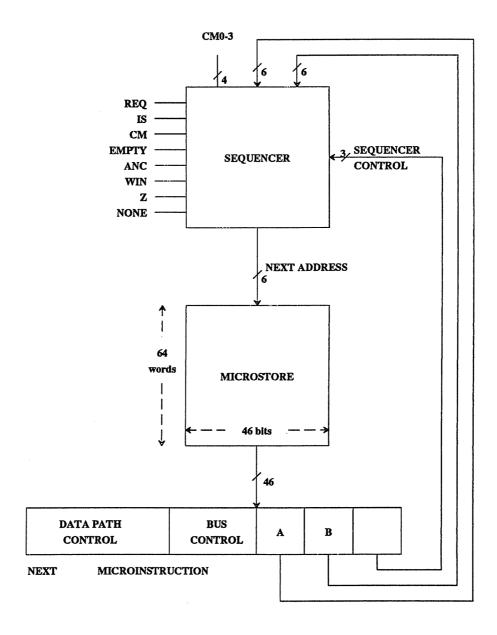

| Figure A.3 — Micro-Instruction Format                            | 162 |

| Figure A.4 — Micro-Sequencer and Control                         | 162 |

| Figure A.5 — Main Loop Flow-Chart                                | 167 |

| Figure A.6 — Block Transfer Flow-Chart                           | 167 |

| Figure A.7 — Block Read Data Flow-Chart                          | 170 |

| Figure A.8 — Block Write Data Flow-Chart                         | 170 |

| Figure A.9 — Enqueue Control Block Flow-Chart                    | 172 |

| Figure A.10 — First Control Block Flow-Chart                     | 174 |

| Figure A.11 — Dequeue Control Block Flow-Chart                   | 176 |

| Figure A.12 — Read Flow-Chart                                    | 176 |

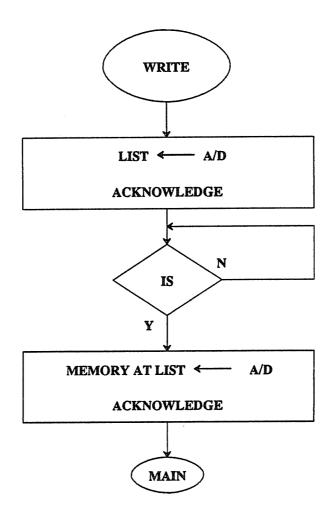

| Figure A.13 — Write Flow-Chart                                   | 178 |

# **List of Tables**

| Table 3.1 — Charlotte Profiling                                        | 34  |

|------------------------------------------------------------------------|-----|

| Table 3.2 — Jasmin Profiling                                           | 35  |

| Table 3.3 — 925 Profiling                                              | 35  |

| Table 3.4 — Unix Profiling (Local Message)                             | 40  |

| Table 3.5 — Unix Profiling (Non-local Message)                         | 41  |

| Table 3.6 — Unix Servers                                               | 42  |

| Table 3.7 — Unix Read/Write                                            | 43  |

| Table 5.1 — Smart Bus Signals                                          | 64  |

| Table 5.2 — Smart Bus Commands                                         | 65  |

| Table 6.1 — Comparison of Processing Times                             | 89  |

| Table 6.2 — Architecture I: Non-local Conversation (Client Contention) | 95  |

| Table 6.3 — Architecture I: Non-local (Client Contention Attributes)   | 96  |

| Table 6.4 — Architecture I: Local Conversation                         | 100 |

| Table 6.5 — Architecture I: Local Conversation (Transitions)           | 100 |

| Table 6.6 — Architecture I: Non-local Conversation                     | 102 |

| Table 6.7 — Architecture I: Non-local Conversation (Client)            | 103 |

| Table 6.8 — Architecture I: Non-local Conversation (Server)            | 107 |

| Table 6.9 — Architecture II: Local Conversation                        | 109 |

| Table 6.10 — Architecture II: Local Conversation (Transitions)         | 109 |

| Table 6.11 — Architecture II: Non-local Conversation                   | 112 |

| Table 6.12 — Architecture II: Non-local Conversation (Client)          | 112 |

| Table 6.13 — Architecture II: Non-local Conversation (Server)          | 115 |

| Table 6.14 — Architecture III: Local Conversation                      | 117 |

| Table 6.15 — Architecture III: Local Conversation (Transitions)        | 117 |

| Table 6.16 — Architecture III: Non-local Conversation                  | 117 |

| Table 6.17 — Architecture III: Non-local Conversation (Client)         | 117 |

| Table 6.18 — Architecture III: Non-local Conversation (Server)         | 117 |

| Table 6.19 — Architecture IV: Local Conversation                       | 122 |

| Table 6.20 — Architecture IV: Local Conversation (Transitions)         | 122 |

| Table 6.21 — Architecture IV: Non-local Conversation                   | 122 |

| Table 6.22 — Architecture IV: Non-local Conversation (Client)          | 122 |

| Table 6.23 — Architecture IV: Non-local Conversation (Server)          | 122 |

| Table 6.24 — Offered Loads (Local)                                     | 134 |

| Table 6.25 — Offered Loads (Non-local)                                 | 134 |

| Table A 1 — Data Path Chin: Component Count                            | 181 |

## Chapter 1

### Introduction

Traditionally, operating systems for uniprocessors have been implemented as a *monolithic kernel*. System services such as resource management, file management, device management, and medium-term and long-term scheduling were integrated into the kernel. The kernel is considered a protected area of the system software and thus the system services made available to the user are safe (from the user's point of view) and secure (from the system's point of view). The structure of a monolithic kernel is based on a shared memory model. The kernel individually shares memory with every application. User initiated operations are performed by the kernel using this shared memory window.

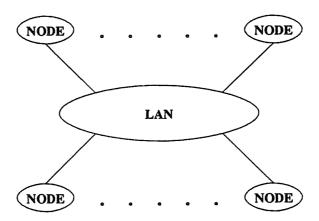

Distributed systems drastically changed the expectation of the user community toward the operating system. We define a distributed system as a collection of computing nodes interconnected by a local area network (LAN). There are one or more processors and a certain amount of memory in each node. The nodes do not share memory. Message exchange across the network is the only mechanism for communication between nodes. We do not assume anything else regarding the hardware configuration of each node. For instance, it is possible that one node may have a printer attached to it while another may not. Figure 1.1 shows our model of a distributed system. There are several disadvantages in a monolithic kernel that get highlighted in the context of a distributed system.

Figure 1.1 — Distributed System

- (1) System services are distributed among the nodes. Users may request services available on a remote node. System services have to deal with local and remote requests and be able to specify policies for handling them (perhaps) differently. Moreover, with a diverse user community there is greater need to protect the integrity of the system from malicious and naive users. Policy and mechanism are integrated in a monolithic kernel. Ideally, we want the kernel to provide mechanisms to implement *any* reasonable policy. This separation offers both flexibility as well as robustness.

- (2) Distributed systems offer the potential to balance the load across all the nodes. For instance, it is reasonable to expect a heavily-loaded node to request a lightly-loaded node to satisfy a user request. In a monolithic kernel, user requests for system services are always satisfied locally, if available. Thus the potential for load-leveling is lost with a monolithic kernel.

- (3) Monolithic kernels tend to be huge in size even for uniprocessors. Developing and debugging such kernels is an arduous effort. The problem is exacerbated

- for a distributed system. For example, 4.2bsd Unix kernel is over 300K Bytes in size.

- (4) There are a myriad of software engineering problems with monolithic kernels such as keeping consistent versions across the nodes and installing new device drivers.

#### 1.1. Message Based Operating Systems

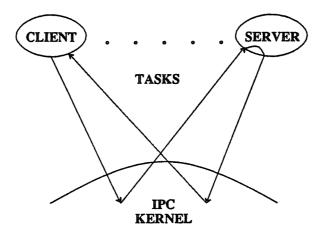

The shared memory model of a monolithic kernel does not extend to a distributed system. For reasons pointed out in the previous section, it seems appropriate to separate the system servers from the kernel. What remains in the kernel? Since there is no shared memory between the nodes, message exchange is the basic mechanism that needs to be provided in the kernel. This message passing kernel together with the servers constitute the message-based operating system. RC 4000 [Brinc 70], CSP [Hoare 78], and Thoth [Cheri 79] are early examples of message-based operating systems. With the advent of local area networking and distributed systems, message-based operating systems have become an interesting research area as indicated by several recent efforts [Baske 77, Cheri 83, Finke 83, IBM 83a, Kepec 84, Lee 84, Rashi 81, Solom 79, Tanen 81]. With a distributed system as the stage, and a collection of processes that interact with one another via explicit messages as actors, each of these research efforts has defined the semantics for message exchange between processes, that is, InterProcess Communication (IPC).

There are two important figures of merit in this environment: round-trip time, and message-throughput. Round-trip time is the elapsed time seen by an application between sending a message and receiving a reply from the intended receiver. This figure of merit affects an individual application's performance. Message-throughput is

a global figure of merit that determines the performance of the entire system. Informally, it is the number of messages that the system is capable of handling per unit time.

Defining the requirements of the user community in a distributed system, designing IPC primitives to meet these requirements, defining a framework for comparing the different IPC proposals, and designing the appropriate interface between distributed programming languages and IPC primitives are very challenging issues. Connection-oriented communication, message size and kernel buffering, process control, multicast/broadcast communication, selective receipt, and asynchronous receipt are some of the semantic issues involved in the design of IPC primitives. However, these issues are beyond the scope of this dissertation. Other researchers have investigated some of these issues [Andre 83, Lebla 82, Nelso 81, Scott 85].

#### 1.2. The Problem

We first define the problem we are trying to solve in this dissertation. The environment of interest in this research is a distributed system (Figure 1.1). A message-based operating system executes in each node. Processes communicate with one another via explicit messages — i.e., there is no shared memory for communication between processes. Communication between processes on the same node we refer to as local communication. Communication between processes on different nodes we refer to as non-local or remote communication. This view of computing has been assumed by several of the IPC proposals we just mentioned. Access to system services are requested via protected procedure calls in a traditional system, whereas in a message-based operating system they are requested via message passing. While a procedure call costs just a few instructions, IPC costs a few thousand instructions in

several systems that we studied (see § 3.4). Since message exchange is the basic kernel mechanism in message-based operating systems, the **performance** of the system depends crucially on the **rate** of message exchange. The slowness of IPC is associated with the high processing overhead that is incurred in message passing. By processing overhead, we do not mean some underlying inefficient communication mechanism that is slowing down the message-passing primitives. In fact, in each of the systems we studied, the underlying communication mechanism is fine-tuned to best reflect the message-passing primitives. The high processing overhead is in spite of this tuning.

While the problem is well-defined, there is a paucity of solutions specific to this environment. There are commercial [ABLE 84, Inter 83] products that help off-load the protocol processing for some standard protocols such as TCP/IP [Poste 81] and TP [ISO 83]. In chapter 2, we survey some of the recent efforts toward providing hardware support for network communication. Recently, there have been some modeling studies investigating the performance of front-end processor architectures [Verno 86, Woods 84]. These studies have been concerned with off-loading communication protocol processing onto front-end processors, the performance benefits that accrue from such off-loading as a function of the fraction of the total work off-loaded, and the effects on the performance due to the relative speeds of the host and the front-end processors.

The available hardware support and the modeling studies have one common premise: It is worth off-loading communication protocols to front-end processors. They implicitly assume "communication" to be the work that is performed by the operating system to satisfy non-local requests. This assumption may be reasonable for a monolithic kernel such as Unix, wherein system services are *not* requested by "message passing" mechanism. However, we have shown through our profiling studies (see

§ 3.4) that there is a high processing overhead in *both* local and non-local communication in all of the systems we studied. Thus, while the above premise is true, it is also a very simplistic approach to a much larger problem. Moreover, a protocol processor for some standard protocol (such as TCP/IP) may not mesh well with the operating system primitives. Therefore the problem needs to be addressed at a much higher level.

#### 1.3. Goals

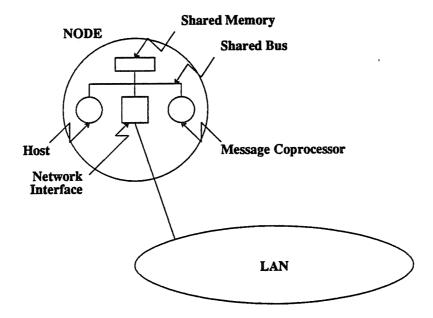

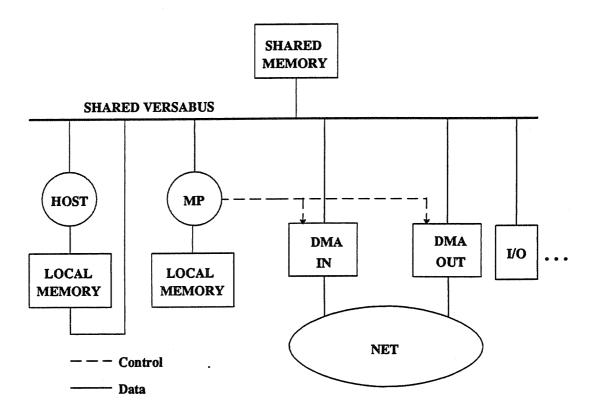

Given the fact that in distributed systems processes communicate with one another via explicit messages, and given that there is considerable processing overhead associated with message passing, there is tremendous potential for improving the message-throughput of the system by providing concurrent processing support. With a view to providing concurrent processing support, the organization we propose inside each node is shown in Figure 1.2. There is a host in each node that executes the message-based operating system and the applications. The shared bus, the shared memory, the message coprocessor, and the network interfaces together function as a single unit in assisting the host in message passing activities. The host, the message coprocessor and the network interfaces interact and synchronize via the shared memory. Note that this organization is similar to the ones assumed in the studies of network front-ends such as Woodside [Woods 84], and in the commercial products such as ABLE [ABLE 84]. However, what distinguishes our work from these earlier proposals is the level of message-passing support envisioned in our proposal. In chapter 3, we show that even local message-passing suffers from considerable processing overhead. Therefore, in this research, we provide support for message-passing at the level of the operating system primitives. Our solution to the problem suggests a system architecture that has a software aspect and a hardware aspect.

Figure 1.2 — Node Architecture

Our goal in this research is to determine a system architecture within each node that improves the system performance over an organization that does not have such hardware assistance. Our objective reduces to answering two main questions:

- (1) How should the message-based operating system be *partitioned* between the host and the message coprocessor?

- (2) What kind of bus architecture is appropriate to support interaction between the host, the message coprocessor, and the network devices?

For a given semantics of interprocess communication, round-trip time signifies a certain minimum processing overhead that has to be incurred to effect the message transfer between the sender and the receiver. If there are exactly two processes communicating with each other in the entire system, clearly there would be an increase in the processing overhead due to the interaction between the host and the message

coprocessor. However, we show that this increase can be kept very small by a careful partitioning of the message-based operating system (see chapters 4 and 6). Moreover, through our performance results, we show (see chapter 6) that the per-process round-trip time improves as a result of improving the message-throughput when there are several processes communicating with one another.

## 1.4. Description of Approach

- (1) To further our understanding of the message-passing problem, we studied four operating systems. We profiled these systems to get a breakdown of the message-passing time into component operating system functions such as short-term scheduling and kernel buffering.

- (2) These studies showed a trend that is common to the problem of message passing, and suggested a partition of message-based operating systems. We demonstrated the feasibility of this partition by implementing it on an existing system.

- (3) The implementation gave us insight into the system data structures that are manipulated in communication processing, the operations that are done on them, and the overhead for these operations. Based on the implementation experience, we have proposed a bus architecture that is appropriate to support the interactions between the host, the message coprocessor, and the network devices.

- (4) To evaluate the performance benefits of the software and hardware aspects of our proposed system architecture, we took an analytical modeling approach. By developing these models and analyzing them, we have demonstrated the effectiveness of our solution to the message-passing problem.

#### 1.5. Thesis Overview

We present a survey of the existing hardware support for IPC and discuss their short-comings to solve the message-passing problem in chapter 2. In chapter 3, we give a summary of the profiling results from our study of several operating systems, and propose a partition of the message-based operating system between the host and the message coprocessor. Chapter 4 contains implementation details of this *software* partitioning of an experimental system. Our proposal for a high-level transaction bus and an overview of the design of a shared memory controller that supports these high-level transactions is described in chapter 5. We show through this design the feasibility of the bus primitives from the point of view of hardware implementation. Chapter 6 contains details of developing analytical models of several system architectures and the performance results. We present a discussion of our design and conclusions in chapter 7.

# Chapter 2

#### **Related Work**

#### 2.1. Overview

Coprocessors are in use in a variety of situations. For instance, floating point accelerators found in many commercial systems work in coprocessor mode. Motivation for our research stems from the fact that to date, the performance of monitor-based operating systems has been superior to that of message-based operating systems. LOCUS [Walke 83] and 4.2bsd Unix [Joy 83] are examples of successful monitor-based operating systems. Existing hardware support for interprocess communication takes the form of:

- (1) Operations on structured data types in the instruction set architecture of the processor (often through microcode).

- (2) Network interfaces with direct access to host memory.

- (3) Protocol processors that implement some form of transport level protocol for off-machine communication.

- (4) Multiprocessor architectures with one processor performing message passing functions, generally for a group of processors.

- (5) Bus architectures that support higher level operations.

#### 2.2. Processor Architecture

Intel's iAPX 432 [Cox 81] chip architecture together with their iMAX [Kahn 81] operating system is an effort to unify machine architecture with the operating system. The processor architecture and the microcoded iMAX operating system, complement each other in providing a variety of interprocess communication mechanisms. The processor architecture is object-oriented, and messages and processes are examples of these objects. Intel's 432 architecture implements a very general concept of ports. "Communication ports" and "dispatching ports" are specific examples. The former binds message objects to process objects while the latter binds processor-carrier objects to process objects. In general, a port is the queueing point for objects. The communication port is used for interprocess communication, and it provides the synchronization between processes in addition to serving as the queueing point for messages. The hardware supports both blocking and non-blocking interprocess communication primitives. Mechanisms for process control and scheduling are implemented in hardware. "Carrier object" is another object supported in hardware, and is a very useful notion for implementing servers. While the 432 architecture is interesting, it pays a severe performance penalty on account of providing too much functionality in the processor architecture. We show in this dissertation that part of the solution for the message-passing problem lies in providing concurrent processing support.

The System 38 [Berst 82, Dahlb 82, Hoffm 82, Pinno 82] architecture provides a hardware-independent instruction interface to the user through the notion of objects. Objects in the system 38 architecture are similar in concept to the idea of Simula *class* [Birtw 73], in that the operations on the object are visible to the outside world but the internal representation is not. The internal representation of the object is implemented in hardware and the operations visible to the user are implemented in microcode.

Processes communicate through queue objects. The operations *send* and *receive* are defined on the queue object. *Send* is non-blocking while *receive* is blocking. Hardware provides the necessary mutual exclusion and synchronization between processes competing for the same resources through the queue object. Process scheduling is implemented in microcode and hardware. The interprocess communication mechanisms are purely for processes on the same physical processor. There is no notion of interconnecting multiple processors or networking in the system architecture.

ELXSI 6400 [Olson 83] is a bus-oriented shared-memory multiprocessor system. The system consists of 1 to 14 processors with 4 to 192 Mbytes of shared memory. The central system bus has a bandwidth of 320 Mbytes/sec excluding control bits. EMBOS is a message based operating system which executes on ELXSI 6400 system, providing demos-like [Baske 77] links. The processor architecture has twenty-six special instructions for message handling, implemented in three thousand words of microcode. On a *send-message* instruction, the hardware and microcode perform all the necessary verification checks for the existence of the target process, link-address validation, queueing of the message for transmission, and process switching to schedule the target process. Each processor maintains a hardware table of fourteen process context blocks, enabling the microcoded scheduler to perform a context switch in 10 microseconds upon message arrival. The system ensures message delivery even if the process has migrated to a different processor.

Tandem 16 [Katzm 82] multiprocessor architecture together with Guardian [Bartl 82] message-based distributed operating system is a fault-tolerant computing system with explicit hardware support for non-local messages. The system architecture includes a pair of high-speed inter-processor buses and hardware queues in each processor module associated with each bus for queueing message requests. The

destination address for each message to be received is preset in special hardware tables called bus-receive tables by the operating system kernel in the receiving processor. The message transfer between processors takes place directly between the sending and receiving processors' memories without any additional copying. The processor architecture supports an atomic hardware *send* instruction which is blocking. *Message receipt* is implicit and is done by the bus interface directly into the main memory in parallel with program execution on the receiving processor. Note that the processor is idle until the send is completed. The architecture minimizes the amount of datacopying involved in non-local interprocess communication. However, we show in the next chapter that the processing overhead involved in interprocess communication overshadows the copying overhead for message sizes up to a 1000 bytes.

The VAX 11 [DEC 78] family of computers is a very popular architecture. While it does not provide any explicit support for interprocess communication in hardware, it does provide two hardware instructions to insert and remove from a queue data structure implemented in memory. The hardware does not guarantee the integrity of these queues if these locations are accessed through other machine instructions. However these instructions are atomic and thus guarantee mutual exclusion and synchronization for interprocess communication in a controlled environment.

There is a fundamental limitation to the benefits that can be obtained by support for message-passing within the processor architecture. Performance results on the V kernel [Cheri 83] indicate that in a distributed environment, the processor bandwidth is insufficient to match the network bandwidth. Ideally, the message passing support should be in parallel with the host processor, so as to allow the host processor to perform other useful work. From the above discussion, it is apparent that, iAPX 432, System 38, and ELXSI 6400 all suffer from this limitation.

#### 2.3. Network Interfaces

Several recent researchers have argued that network interfaces should provide more functionality [Kepec 84, Mocka 82]. Mockapetris proposed a special-purpose piece of hardware (*local network interface*) [Mocka 77, Mocka 82] that provides location-independent process naming, programmable process-name tables, hardware recognition of multicast messages, associative-match hardware for looking up the destination of a message, and assurance of data delivery through the use of *match* and *accept* bits in the packet.

The interface message processor [Lee 78] gives a network architecture, protocol, and interface processor specification for a high speed recirculating data network. Lee discusses some interesting ideas for organizing the interface processor. The interface processor is implemented as three processors communicating through shared memory. The three processors respectively handle receiving, transmitting, and formatting messages.

Pronet [Prote 82], Deqna Ethernet [DEC 84], and Interlan [Inter 83] Ethernet are some of the currently available local networking hardware products. Each of these products offer an interface that performs the data-link and physical-layer functions of the Ethernet-standard proposed by Metcalfe and Boggs [Metca 76]. The interfaces handle source addressing, message framing, bit stuffing and de-stuffing and network management and error recovery functions. All of these interfaces use *direct memory access* to move data from the host memory to their packet buffers. The fixed-size receive-buffers in the interfaces are intended to help the host processor to cope with the bursty nature of network traffic. While such interfaces are essential for inter-node communication, they are not a solution for the message-passing problem in distributed systems. In fact, several researchers [Cheri 83, Gagli 85, Kepec 84, Lebla 82] have

reported message transfer-rates between processes that are only a fraction of the available network bandwidth.

#### 2.4. Protocol Processors

A single-chip product from Quanta Microtique [Quanta 83] supports a single TCP [Poste 81] connection. The network filter proposed by Mockapetris [Mocka 82] can be used together with a fast microprocessor and direct access to the host memory to implement most of the TCP protocol.

The single-board protocol processor from ABLE [ABLE 84], implements NBS level 4 [ISO 83] transport protocol. It uses the Intel 80186 [Intel 82] processor, and is interfaced to the VAX Unibus. Intel markets a functionally equivalent product for the Multibus. The protocol support is in *proms* mounted on-board, and provides the bottom four levels of the ISO protocol hierarchy [Zimme 80]. The existing version supports NBS level 4 (TP) protocol for Ethernet-based local area network. ABLE also supplies boards without *proms* for those who wish to develop their own firmware.

Intel [Stark 83] has announced a high-performance protocol coprocessor (i82586) for the Ethernet. The chip provides line control functions such as bit stuffing/unstuffing, error detection, network management, collision detection and back-off algorithms, and detailed timing functions for the Ethernet. The chip communicates via shared memory with the host processor. A linked list of commands can be specified to the protocol processor, which handles the associated data transfer without the need for host-processor intervention. The chip improves the utilization of the host-processor's memory by storing an incoming message-frame in a linked list of buffers. The processing overhead associated with receive-buffer chaining is handled by the chip, transparent to the user. The chip also provides facilities for recognizing

multicast addresses and broadcast addresses.

The TCP and TP interfaces discussed above, provide processing-support to the host-processor at the transport-layer level of the ISO protocol hierarchy [Zimme 80]. Intel's chip performs the data-link and physical-layer functions of Ethernet specification in addition to command chaining and receive-buffer chaining. While protocol processors can be of assistance in off-loading standard communication protocols such as TCP, they do not solve the message passing problem in distributed systems for two reasons:

- (1) There is no assistance for local message passing.

- (2) There is additional overhead in the form of host to front-end protocol.

#### 2.5. Multiprocessor Architecture

#### 2.5.1. Cm\*

Cm\* [Fulle 78] is a multi microprocessor computer system using LSI-11 [DEC 77] as the processing element. Each processing element has access to all of the system memory. The system organization is as follows. Each processor has a 64Kbyte local memory directly accessible through an internal bus. One to fourteen processors are interconnected by a map-bus and constitute a cluster. The clusters are interconnected by inter-cluster buses. A switch associated with each processor called *Slocal* determines whether an address generated by the processor is a local memory reference or an external memory reference. Local memory references are resolved on the LSI-11 bus. If the reference is external then Slocal passes it to the second level switch called the *Kmap*. The Kmap determines whether the reference is within the same cluster or outside the cluster. Intra-cluster references are routed to the appropriate Slocal on the

map-bus. Inter-cluster references are routed by the Kmap to the appropriate Kmap on the inter-cluster bus. The Slocal and Kmap have the address translation tables and are microcoded to perform the necessary translation. In addition to the address translation the Kmap provides microcode support for operating system functions such as semaphores called *spinlocks*, event queues, and message queueing points called *mailboxes*.

StarOS [Jones 79] is a message-based operating system that executes on Cm\*. Messages are queued in mailboxes awaiting reception. Interprocess communication is implemented via mailboxes. The mailboxes can either queue capabilities or sixteen bit data words. Mailbox functions are implemented partly in microcode.

#### 2.5.2. Auragen 4000

Auragen 4000 [Borg 83] is a message-based multiprocessor system. The basic processing unit is a cluster. The system has two high-speed inter-cluster buses and two to thirty-two clusters can be connected on these buses. Each cluster contains from three to seven Motorola 68000's [Motor 82b] and a large shared memory. One processor in each cluster is a dedicated message processor called the *executive*; the executive handles all inter-cluster message traffic. Two processors in each cluster run user and server processes, referred to as *work* processors. The remaining processors in the cluster handle peripheral and communication ports. The operating system *Auros* which executes on the system is a distributed version of Unix [Ritch 74]. Each cluster executes an identical copy of the Auros kernel. Auros performs operating-system functions local to each cluster such as scheduling runnable processes, memory management, control of local peripherals, and message handling. Auros does not perform global resource control. The message system is embedded in the operating system kernel. Processes communicate via two way communication *channels*. An entry in a cluster-

local table, the routing table, defines one end of a channel. A routing table entry contains all routing information, message queues and status information for a channel. A cluster's routing table resides in main memory and is maintained by message-system code executing either in the work or the executive processor. Some portions of the Auros kernel, in particular those responsible for message transmission and delivery, execute only on the executive processor. The message passing chore is divided between the work and the executive processors. The work processor performs validation of the interprocess communication call, channel addressing, message construction and queueing in the cluster's outgoing queue. The executive performs transmission on the inter-cluster bus and delivery of messages intended for processes in the associated cluster. The main thrust of the Auragen system is fault tolerance. Every message from a process is sent to three destinations namely, the primary receiver, the backup receiver and the backup sender. Since the backup for any process is invariably in a different cluster every message goes out on the inter-cluster bus. After the message is successfully delivered to the other clusters, it is delivered to any local destination, to guarantee atomicity of each message. No attempt is made to distinguish between local and nonlocal messages. The executive processor is similar to the Kmap of Cm\*.

## 2.5.3. Butterfly Multiprocessor System

In the Butterfly Multiprocessor [Rettb 82] each processing node is a Motorola 68000 processor with access to 256Kbytes of on-board memory. The processor nodes generate 32-bit virtual addresses. The entire physical memory of the system is accessible from all processing nodes through the butterfly switch. All the system memory is located on processor nodes in the system. It is possible to have a maximum of 4 Mbytes of memory in each processor node. Each processing node has a coprocessor

called processor node controller (PNC) [Rettb 81, Rettb 83], which is a custom-built, microcoded processor using AMD 2901 [AMD 79] bit slice components. The PNC performs the mapping from virtual to physical address for the associated processing node, and also controls the finite state machines for transmitting and receiving on the butterfly switch for non-local memory references. Chrysalis is an object-oriented operating system for the butterfly multiprocessor. The PNC provides event blocks and dual queues as operating-system support functions in micro-code. Dual queues can hold either data or event blocks. They are simple bounded buffers when data items are queued on them. Event blocks are binary semaphores with two exceptions: only its owner can wait on it, and a 32-bit value is returned on the successful completion of the wait operation. A post operation can be performed by any process that knows the name of an event block. "Wait" and "post" are the equivalent of P and V semaphore operations respectively. Process synchronization is implemented using event blocks and dual queues as follows: A receiver dequeues the dual queue. If there is data on the queue the receiver gets it; otherwise an event block that points to the receiving process is enqueued on the dual queue. When the sender wants to enqueue data and finds event blocks queued on the dual queue, it "posts" on the event block instead. The operating system can use these micro-coded operations to implement short-term scheduling of processes.

#### 2.5.4. Discussion

Both Cm\* and Butterfly are *shared-memory multiprocessors* (entire system memory shared by all processors), while Auragen is a distributed system. There is a dedicated processor to handle messages in each of these systems. However, the functions provided by these processors are often low-level and limited. For instance, the

Kmap of Cm\* is mainly intended as a hardware-assist for memory mapping. In addition, it implements a few semaphore functions in micro-code.

The main thrust of the Auragen 4000 system is fault tolerance. The primary reason for a dedicated message processor is to handle the excessive overhead imposed by the fact that every message has to be delivered to three destinations. The "executive" does not operate at the level of the operating system primitives. Instead, it serves as a transport mechanism to deliver pre-formatted messages from one cluster to other clusters. Validity checking, address translation, and kernel buffering of messages are done by the "work" processors. The system does not make any special effort to optimize local message passing. In fact, to guarantee atomicity of message transmission, messages destined for the local cluster are delivered only after the other clusters have successfully received them. There is no special hardware for accessing the shared "routing tables". The "executive" is incrementally better than "protocol processors" (see § 2.4) in that it off-loads some of the short-term scheduling decisions from the "work" processors.

The processor node controller (PNC) of the Butterfly multiprocessor is an AM2901 based microprogrammed processor. The PNC is functionally similar to the Kmap of Cm\*. The primary functions of the PNC are to recognize a non-local memory reference generated by a local node, to validate the access, and to drive the finite state machines of the switch interface in order to retrieve or store the remote memory word. It also responds to remote references to local memory from other PNC's. Additionally, the PNC provides micro-coded support functions on event blocks and dual queues to be used by the operating system for implementing short-term scheduling. However, these short-term scheduling functions are not concurrent with host activities. It is the same thread of the operating system kernel that executes

these functions. We show through our performance results (see chapter 6) that concurrent processing support is one of the keys to solving the message-passing problem.

In the next chapter, we show that validity checking, address translation, control block manipulation, and kernel buffering account for a substantial portion of the message-passing overhead. Moreover, this overhead is incurred for both local and non-local communication. There is no support for such functions in the Kmap of Cm\*, the executive of Auragen 4000, and the PNC of Butterfly.

## 2.6. Bus Architectures

Moving contiguous blocks of data between user and kernel space is one of the chores performed by a message-passing kernel (see chapter 3). Similarly, network interfaces move contiguous blocks of data between kernel or user buffers and the network. Block transfer primitives are useful for efficiently implementing such chores of the message-passing kernel. Several recent bus proposals such as VMEbus [Fisch 84, Fisch 85], Multibus II [Intel 84, Muchm 86, Rap 86], Futurebus [Balak 84, Borri 84, Taub 84], Nanobus [Encor 86], and SB8000 [Seque 85] provide block-mode access to the memory system from the processor. In addition, some of the proposals provide mechanisms for extended control of the bus to enable the current master to perform a sequence of operations on the memory. Such extended processor-memory interlocks are useful for implementing atomic operations of an operating system kernel. In the following sub-sections, we survey these bus proposals focusing on three issues relevant to this research: block transfer primitives, processor-memory interlocked operations, and arbitration. Borrill [Borri 85, Borri 86] and Kirrmann [Kirrm 85] have given a more complete comparison of the features offered by several currently popular 32-bit bus systems.

### 2.6.1. VMEbus

VMEbus has separate 32-bit address and data lines. It employs asynchronous handshake and supports both single and arbitrary-sized block transfers of data. The width of the data transfer can be selected on a cycle by cycle basis to be one of 1, 2, or 4 bytes. The bus is held for the entire duration of a block transfer. However, VMEbus provides a mechanism to preempt the next master-elect or inform the current master that there is a higher priority master waiting for access to the bus. The bus allows two types of requests: release when done (RWD) and release on request (ROR). While the RWD mode is used for single transfers and block mode transfers by devices such as direct memory access (DMA) controllers, the ROR mode is usually used by processors. Using the ROR mode, a processor remains the master of the bus until some other master requests the bus. This feature eliminates the need for a processor to arbitrate for the bus for every transfer. Further, ROR mode establishes a processor-memory interlock thus enabling the processor to perform a sequence of operations on the memory system. Arbitration for the bus is centralized. There are four levels of bus requests and the grant lines are daisy-chained for each level. The arbitration logic can either assign static priorities to each level, or implement a round-robin scheme among the levels.

# 2.6.2. Multibus II

Multibus II with a 32-bit multiplexed address/data lines, employs synchronous handshake for performing both single and arbitrary-sized block transfers of data. The width of the data transfer can be 1, 2, 3, or 4 bytes. In addition to the block transfer mode, Multibus II offers a *message passing* mode of data transfer. This mode allows the bus-interfaces in the bus-modules to exchange up to 28 bytes of data without the intervention of the module master. For example, a disk controller module could use

this mode to transfer data to the processor module. In both block-transfer mode and message-passing mode, the bus is held for the entire duration of the block transfer. There is no mechanism in Multibus II to preempt the current master or the master-elect in the event of a higher priority bus request. The *lock line* provided by the bus helps establish a processor-memory interlock during which a processor can perform a sequence of operations on the memory system. Bus arbitration is distributed, but has to be initiated by a *central service module*.

## 2.6.3. Futurebus

Futurebus [Borri 84] is an attempt to standardize the bus protocol for 32-bit multi-microprocessor systems. The specification proposes 32 multiplexed address/data lines. Similar to VMEbus, Futurebus offers single and arbitrary-sized block transfers using an asynchronous protocol. The block transfers hold the bus until completion. Preemption is possible, however, if there is a higher priority request for the bus. Futurebus supports a notion of "tenure" that gives extended bus mastership to the requester. The current master can break up a high-level operation into a sequence of operations, and execute these operations during this tenure. Arbitration in Futurebus is fully distributed, and is initiated by the current master at the end of the master's tenure.

# 2.6.4. Nanobus

Nanobus [Encor 86] has distinct 32-bit address and 64-bit data lines. It offers primitives for reading and writing fixed-size blocks (8 bytes); there is no support for arbitrary-sized block transfers. Data transfers on the bus are synchronous. Every transaction has a "requester" and a "responder". Usually, the processors are the requesters and the memory modules are the responders. Nanobus decouples requests and responses. This decoupling permits other unrelated requests and responses to occur on

the bus before the responder for a particular request returns the data. Nanobus memory modules accept fresh requests while processing the current one, and return the data in the order of arrival of requests. Each Nanobus memory module has an individual FIFO of outstanding requests; since requests and responses are decoupled, Nanobus *tags* every address and data item on the bus with the requester's identity. The only processor-memory interlocked operation provided by Nanobus is "test and set". There is separate centralized arbitration for the address and the data buses. Address-bus arbitration uses a round-robin scheme, while data-bus arbitration uses a fixed-priority scheme.

#### 2.6.5. SB8000

SB8000 [Seque 85] has multiplexed 32-bit address/data lines. Requests and responses (to reads) are decoupled in SB8000. Synchronous transfers of data packets of 1, 2, 4, and 8 bytes are supported; the responses are returned in the order of arrival of requests. There is a FIFO on the bus common to all memory modules that contains the outstanding requests. The requesters monitor the bus and recognize the response to their request by counting the number of requests outstanding. The SB8000 system offers "atomic lock memory". Each lock is a bit in memory that can be "read and set" (locked) in a single atomic operation. The bus arbitration is centralized with each unit requesting the bus at a pre-assigned priority level.

### 2.6.6. Discussion

Of the recent bus proposals, VMEbus, Multibus II, and Futurebus support "arbitrary" (within limits) sized block transfers. Arbitrary-sized block transfers lead to simpler design of bus modules such as DMA device interfaces. In each case, the bus is held for the entire duration of the block transfer. However, locking the bus for

arbitrary time periods is infeasible. For instance, packet arrival from the net is an asynchronous event. Failure to field and service network interrupts on a priority basis could lead to "data overrun" problems. Therefore, such events require priority access to the system bus. Some of the bus proposals have recognized this requirement. While VMEbus and Futurebus offer mechanisms for preempting the current master or the master-elect, Multibus II offers no such mechanism, but system designers circumvent this problem by allowing bus modules to request only small-sized block transfers. Though Nanobus and SB8000 decouple requests and responses, they do not provide arbitrary-sized block transfers. While all of the bus systems we surveyed offer some help to the processors in performing interlocked operations with the memory, these operations tend to be fairly low-level. The onus of implementing any high-level synchronization mechanism such as atomic queue manipulation is on the processors.

Preempting the current master during a block transfer results in an "abort" of the transfer, leaving the recovery from the abort to be handled by each unit that may make block transfer requests. Proposals such as VMEbus and Futurebus are intended for a versatile environment where there could be multiple memory modules, processor modules, and device modules. In such an environment, it may be worthwhile and even necessary that a processor be able to abort a transfer and restart it when a block transfer spans multiple memory modules. However, in a limited environment where all requests are directed to a single memory module, preemption places a considerable burden on the requesting modules for recovery. It would substantially reduce system complexity (and hence system cost) in such an environment for the memory module to prioritize the requests and service them (as opposed to a system that requires each module to possess recovery hardware). To achieve this capability the following conditions need to be satisfied:

- (1) The bus should not be locked for arbitrary time periods, thus allowing access for higher-priority requests.

- (2) The memory module should save information regarding block transfer requests (address and size) so that it can restart a lower-priority request after servicing a higher-priority one.

In chapter 5, we propose block transfer primitives that have these characteristics. The other innovative feature that we introduce in our proposal is atomic queue manipulation primitives. However, note that we are *not* trying to define a new standard for system buses in this research. On the contrary, these primitives are intended for use in a *limited and controlled environment*. Further, we show that these primitives are reasonable from the point of view of hardware implementation in such a controlled environment. The bus arbitration scheme we use in our bus proposal is inspired by Futurebus [Taub 84] but is simpler owing to the limited environment.

# 2.7. Discussion

The available hardware support is based on the premise that it is worth off-loading communication protocols to front-end processors. But the problem needs to be addressed at a much higher level since research in this area indicates that there is considerable overhead even for local messages. In the next chapter, we present the results of studies we performed on four distributed systems to understand the bottleneck in message passing.

# Chapter 3

# **Measurements of Existing Systems**

#### 3.1. Overview

We studied the design and implementation of four operating systems in detail: Charlotte [Artsy 84, Artsy 86, Finke 83], Jasmin [Lee 84], 925 [IBM 83a], and Unix [Ritch 74]. We profiled them to ensure that we are not discovering coding inefficiencies of one operating system but see a trend that is common to all these systems. Our model of a distributed system assumes that processes communicate via explicit messages and that system services are provided by trusted server processes (as opposed to a monolithic kernel). Charlotte, Jasmin, and 925 belong to this model. However, all of these systems are experimental research projects. We studied Unix to see whether operating systems in extensive use suffer from similar problems, although Unix does not fall into the mold of the kind of distributed system we are interested in for this research.

Charlotte and Jasmin are descendents of *Demos* [Baske 77] operating system. Charlotte is a continuing distributed operating system research project at University of Wisconsin - Madison. It is written in Modula [Wirth 77] and is built on top a communication package called the *nugget* [Cook 83] which provides reliable inter-machine message exchange. Charlotte executes on a network of VAX 11/750 processors interconnected by Pronet (10M Bits/Sec) [Prote 82].

Jasmin is a distributed message-based operating system research project at Bell Communications Research. The operating system is written in C and executes on a network of Motorola 68000 processors interconnected by S/NET (80M Bits/Sec) [Ahuja 82].

The 925 system is a distributed message-based operating system intended as a research vehicle for an office workstation project. The project is currently underway in IBM Research, San Jose. PL.8 [IBM 83b] is the system programming language used in developing 925 on a network of Motorola 68000 based multi-processors interconnected by a 4M Bits/Sec token ring [Bux 81]. More recently, 925 has been ported to the IBM PC/RT [IBM 86a] processor, and has been renamed "Quicksilver".

Unix 4.2bsd [Leffl 83] is a monitor-based operating system with local area networking embedded in the operating system kernel. The version we studied is written in C and executes on Microvax II workstation [DEC 86] interconnected by a 10M Bits/Sec Ethernet [DEC 84]

### 3.2. IPC Semantics

In the next few sub-sections, we discuss the semantic characteristics that distinguish the IPC of the above systems from one another.

# 3.2.1. Connection Oriented Communication

Charlotte, Jasmin, and 925 require that processes that wish to communicate establish a channel for communication *a priori* as opposed to systems such as V kernel [Cheri 83]. Processes in Charlotte create and use a two-way *link* for communicating with other processes. The processes at the two ends of the link have equal rights over the link for using, transferring, and destroying the link. In Jasmin, Processes create

unidirectional paths for communicating with other processes. The path has two ends: send end, and receive end. The creator of the path holds the "receive end" and receives any messages sent along the path. The "send end" can be can be given away by the creator to another process as a gift. The 925 system provides an abstraction called service, which is a queueing point for messages. A process creates a service, and other processes can install the service in their addressing domains and send messages to it. Unix provides a socket abstraction, and all interprocess communication takes place via these sockets. Sockets are two-way communication channels between any two processes and are the logical extension to the idea of pipes introduced in Unix. The transport layer below the socket can be either Unix pipes for local processes or TCP for non-local processes.

There is overhead involved in setting up and tearing down the communication channel. However, communication channels provide an efficient mechanism for the kernel to enforce authentication and security, and for the system to duplicate heavily used services. In Jasmin, to simulate a remote procedure call, a process has to enclose a gift path in the message. The kernel installs the new path which may be used by the recipient only once to send the reply. The kernel incurs the same expense for setting up and tearing down these one-shot connections as for more persistent ones. Based on the assumption that most processes expect a reply for the message sent, Charlotte provides bidirectional communication channels. However, since both the processes have equal rights over the link, checking the validity of a requested operation is very complex in Charlotte. The 925 system offers a good compromise. Information about the sender is held in the service for the duration of the rendezvous. Once the rendezvous is complete all information about the sender is erased from the service. Unix sockets are similar in functionality to Charlotte links, except that sockets (once bound) are static

and involve less checking for validity of requested operations. Messages are *addressed* to links in Charlotte, paths in Jasmin, services in 925, and sockets in Unix.

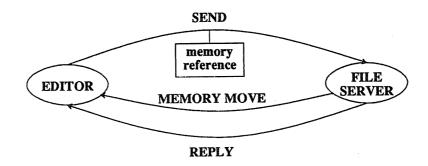

# 3.2.2. Message Size and Kernel Buffering

Messages (reliable datagrams) are not buffered in Charlotte and can be of any arbitrary size. Messages can be either fixed in size or variable in size in both Jasmin and 925. Jasmin and 925 provide kernel buffering for fixed-size messages. A Jasmin process that holds the "send end" of a gift path can send fixed-size messages (reliable datagrams) to the creator of the path using sendmsg. The message is buffered by the kernel and delivered to the process that owns the "receive end". Primitives to move arbitrary-sized blocks of data (in either direction) exist in both Jasmin and 925 (iomove in Jasmin and memory move in 925). This primitive is invoked by the holder of the "send end" of the path in Jasmin, while in 925 it is invoked by the creator of the service. In both the systems, the kernels check to make sure that the processes initiating the data movement have the necessary access permissions. Hence these system calls do not need the participation of the process at the other end. Both the kernels do not buffer these arbitrary sized messages. Messages sent on Unix sockets can be arbitrary in size and are buffered by the kernel. Kernel buffering imposes considerable housekeeping overhead on the kernel. The system has to deal with situations when the necessary resources are not available. Buffer management becomes a complicated issue (due to internal fragmentation) especially when the kernel buffers arbitrary-sized messages.

### 3.2.3. Process Control

The communication primitives in Charlotte (send and receive) can be either blocking or non-blocking. Jasmin's Sendmsg can block the sender if the system is

short on resources. *Rcvmsg* is the system call in Jasmin to receive a message and can block the caller if there are no outstanding messages on the path. *Iomove* blocks the caller till the kernel completes the requested data movement. The 925 system provides both blocking and non-blocking flavors of *send*, while *Receive* is always blocking. We discuss 925 in greater detail in the next chapter. Unix communication primitives block if system resources are not available. However, it is also possible to specify via socket options that communication primitives on a socket should not block.

## 3.2.4. Send

Charlotte, Jasmin, and Unix implement no-wait send. Posting a Charlotte send is synchronous while completion can be asynchronous. The sender can either poll the completion status or explicitly wait. The send primitive of 925 can be either no wait send or remote invocation send. The latter expects a reply from the receiver and has to explicitly wait for the reply. V kernel provides multicast send allowing a message to be addressed to several recipients. None of Charlotte, Jasmin, or 925 provide multicast/broadcast capability. Multicast communication under 4.2bsd Unix has been recently reported [Ahama 85].

### 3.2.5. Receive

Posting a Charlotte *receive* is synchronous while completion can be asynchronous. Similar to *send*, the receiver can poll the completion status or explicitly wait. Both 925 and Unix offer the facility to poll for message arrival. Jasmin has no such polling capability.

Jasmin allows a process to specify a group of paths as the source of next message. A Charlotte process can either specify any *one* link or *all* the links (that it is connected to) as the source of next message. There is no mechanism for selective receipt in either

925 or Unix.

At the time of creating a service, a 925 process can specify a *handler*. When the process posts a *receive* on the service, the kernel copies the message to the buffer specified by the process and invokes the handler. Control is returned to the process when the handler eventually *replies* to the message request. Processes in Jasmin, Charlotte, and Unix do not have the capability to specify a handler.

# 3.3. Measurement Techniques

We profiled the above operating systems to understand where time is spent in the kernel while processing message passing requests. We conducted three kinds of timing measurements:

- (1) CPU-time profiling is a measure of the distance in time between two points in a straight-line code segment. This measurement helps obtain statistics of processor-time usage in different sections of the kernel code, "hot spots", and system bottlenecks.

- (2) Procedure-call profiling is a measure of the procedure-call sequence, the number of times a kernel procedure is called, and the time spent in the procedure per visit.

- identifying the message-path from source to destination, and time-stamping the message at "interesting points" such as queueing, dequeueing and copying, we get useful statistics on the usage of kernel data structures, the type of operations that are performed on these data structures, and the amounts of time spent by the message on different queues. This measurement identifies bottlenecks (if any) in the message route. For example, if the network device is the

bottleneck, messages will probably spend most of the time on the device queues.

Profiling involves instrumenting the kernel program with code to capture the timing information into special data structures. For example, the following is the data structure we used for procedure-call profiling:

procedure\_entry = record

count : integer; timer\_value\_at\_entry : integer; elapsed\_time : integer;

end;

statistics: array (procedure\_names) of procedure\_entry;

The "statistics" data structure has an entry for each of the kernel procedure that is executed while processing a communication request. This data structure is compiled in with the kernel. A "kernel run" consists of executing a producer program that sends a fixed number of messages, and a consumer program that receives the messages from the producer. The "statistics" data structure is cleared before starting a kernel run. We read the hardware timer on entering a kernel procedure and register the value (in a field of the array entry indexed by the procedure name). Before exiting, the hardware timer is read again. The difference between the value read and the value registered at entry gives the time spent in the procedure (applying correction if the timer wraps around). We add this to the time accumulated from previous visits to the procedure kept in "elapsed\_time". The "count" field is incremented during each visit. On completion of the kernel run, we analyze the "statistics" data structure to apportion the time spent in the kernel to the individual procedures involved in the execution path. Suitable corrections have to be made to remove the cost incurred due to the timing code itself.

## 3.4. Measurement Results: Communication

For each system, the statistics were gathered by simulating a null remote procedure call. The sender executes a "send; wait for reply" loop, while the receiver executes a "receive; reply" loop. The round-trip time for a 1000-byte local message in Charlotte is 20 milli-seconds (0.5 MIPS VAX 11/750). The copy-time, i.e., the time to move information back and forth between the processes in one round-trip is only 0.6 milli-seconds (3% of round trip). Table 3.1 gives the breakdown of the round-trip time into component message-passing activities. The round-trip time for a 1000-byte non-local message is 31.7 milli-seconds, of which 4.4 milli-seconds (13.9% of round trip) is copy time. It is not until the (non-local) message size is 6000 bytes that the copy-time

VAX 11/750 (Speed ≈ 0.5 MIPS)

Round Trip (Local Message) = 20 mill-seconds (1000 Bytes one way)

Copy Time = 0.6 mill-seconds

| Copy Time one man sevenes                         |                 |                    |

|---------------------------------------------------|-----------------|--------------------|

| Activity                                          | Time            | Percent of         |

| Name                                              | (milli-seconds) | Round-Trip<br>Time |

| Kernel-Process Switching Time                     | 2               | 10                 |

| Copy Time                                         | 0.6             | 3                  |

| Entering and Exiting Kernel                       | 2.8             | 14                 |

| Protocol Processing<br>for Sender<br>and Receiver | 10              | 50                 |

| Link Translation<br>and<br>Request Selection      | 4.6             | 23                 |

Table 3.1 — Charlotte Profiling

begins to dominate the round-trip time (over 50% of round-trip time). We discuss the profiling results of Charlotte in more detail below.

Table 3.2 gives the breakdown of the round-trip time (local message) for Jasmin. The copy-time is 15% of the round-trip time. Jasmin was not a stand-alone operating system at the time of profiling. The test program was bound with the kernel and downloaded on to the processors. All three — the kernel, the sender, and the receiver programs execute in the same address space. The kernel procedures are invoked as subroutines — hence the surprisingly small round-trip time (0.72 milli-seconds on a 0.3 MIPS Motorola 68000). In Jasmin, non-local communication is implemented by a "communication task", that is periodically scheduled by the kernel to check the network channels for incoming and outgoing messages. Note that this task accounts for 15% of the round-trip time in spite of the fact that we measured local messages. A process is blocked in Jasmin when its communication request cannot be satisfied because of a temporary shortage of kernel resources. Short-term scheduling decisions in Jasmin include dispatching processes waiting on path-queues for messages, and processes blocked waiting for scarce kernel resources. 40% of the round-trip time is devoted to the processing of events leading to short-term scheduling decisions. Path management includes checking the validity of requests issued on the paths, and addressing the relevant control blocks. Buffer management includes allocating and releasing kernel buffers for copying messages from user space.

Table 3.3 gives a breakdown of the round-trip time (local message) into message-passing activities for 925. Interprocess communication in 925 follows a client-server paradigm. Clients make requests on services and servers satisfy outstanding requests on services. The scheduler in 925 is event driven. These events include

Motorola 68000 (Speed ≈ 0.3 MIPS)

Round Trip (Local Message) = 0.72 milli-seconds (32 Bytes each way)

Copy Time = 0.108 milli-seconds

| Activity<br>Name                                                              | Time (milli-seconds) | Percent of<br>Round-Trip<br>Time |

|-------------------------------------------------------------------------------|----------------------|----------------------------------|

| Actions Leading to Short-Term Scheduling Decisions                            | 0.288                | 40                               |

| Copy Time                                                                     | 0.108                | 15                               |

| Buffer Management                                                             | 0.072                | 10                               |

| Path Management                                                               | 0.144                | 20                               |

| Miscellaneous (Checking Network Channels, Communication Task Execution, etc.) | 0.108                | 15                               |

Table 3.2 — Jasmin Profiling

Motorola 68000 (Speed ≈ 0.3 MIPS)

Round Trip (Local Message) = 5.6 milli-seconds (40 Bytes each way)

Copy Time = 0.84 milli-seconds

| Activity                                                   | Time            | Percent of         |

|------------------------------------------------------------|-----------------|--------------------|

| Name                                                       | (milli-seconds) | Round-Trip<br>Time |

| Short-Term Scheduling (Including event processing)         | 1.96            | 35                 |

| Copy Time                                                  | 0.84            | 15                 |

| Entering and Exiting Kernel                                | 0.56            | 10                 |