THE FORMAL DESIGN AND ANALYSIS OF

DISTRIBUTED DATA-PROCESSING SYSTEMS

by

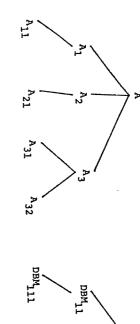

D. R. Fitzwater

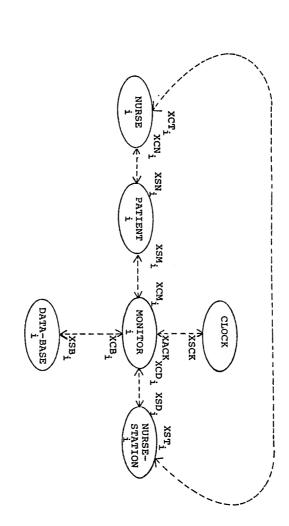

Computer Sciences Technical Report #322

August 1978

### THE FORMAL DESIGN AND ANALYSIS OF DISTRIBUTED DATA-PROCESSING SYSTEMS\*

by

#### D. R. Fitzwater

#### ABSTRACT

The abstract proposal is to support the development of the "science" behind software engineering in order to ensure required system properties, to compare current software engineering techniques, to develop specification for new design and analysis tools, and to demonstrate the practicality of the "science".

A hierarchical design schema will be developed within which formal representations and analyses can be defined and the required solutions can be found.

This report describes further work (based on CSTR 295) in DDP design, real-time systems, evolutionary processes and requirements analysis. It also presents a systematic development of the required design theory, with some examples of its use.

<sup>\*</sup>Sponsored by the Ballistic Missile Defense Systems Command, Contracts Office, BMDSC-CRS, P.O. Box 1500, Huntsville, AL 35807, under Contract No. DASG60-76-C-0080.

#### TABLE OF CONTENTS

| 1. | . Executive Overview |          |                                 |    |  |  |  |

|----|----------------------|----------|---------------------------------|----|--|--|--|

|    | 1.1                  | Payof    | fs                              | 6  |  |  |  |

|    | 1.2                  | Resea    | arch Approach                   | 7  |  |  |  |

|    |                      |          | fication Properties             | 8  |  |  |  |

|    | 1.4                  |          | fication Language               | 10 |  |  |  |

|    |                      |          | odology                         | 10 |  |  |  |

|    | 1.6                  |          | n Principles                    | 11 |  |  |  |

|    | 1.7                  |          | re Work                         | 13 |  |  |  |

| _  | <b></b> .            | <b>.</b> | •                               |    |  |  |  |

| 2. | 2. Introduction      |          |                                 |    |  |  |  |

|    | 2.1                  | Tech     | nical Quotation                 |    |  |  |  |

|    | 2                    | .1.1     | Research Area                   | 15 |  |  |  |

|    | 2                    | .1.2     | Overall Approach                | 25 |  |  |  |

|    | 2                    | .1.3     | Critical Issues                 | 28 |  |  |  |

|    | 2                    | .1.4     | Work Plans                      | 29 |  |  |  |

|    | 2.2                  | Orga     | nization                        | 31 |  |  |  |

| 3. | A Th                 | eory     | of Design                       |    |  |  |  |

|    | 3.1                  | Rese     | arch Approach                   | 33 |  |  |  |

|    | 3                    | .1.1     | Discrete Processes              | 34 |  |  |  |

|    | 3                    | 1.2      | System Development              | 35 |  |  |  |

|    |                      | 3.1.3    | Design Theory Development       | 38 |  |  |  |

|    |                      | 3.1.4    | Conclusions                     | 53 |  |  |  |

|    | 3.2                  |          | ributed Data-Processing Systems | 55 |  |  |  |

|    |                      |          | Development Pavoffs             | 55 |  |  |  |

| 3   | .2.2  | DDP Characteristics                                     | 59  |

|-----|-------|---------------------------------------------------------|-----|

| 3.3 | Speci | ification Properties                                    | 64  |

| 3   | 3.3.1 | Formality                                               | 64  |

| 3   | 3.3.2 | Consistency                                             | 69  |

| 3   | 3.3.3 | Effectiveness                                           | 70  |

| 3   | 3.3.4 | Homogeneity                                             | 73  |

| 3   | 3.3.5 | Modularity                                              | 76  |

| 3   | 3.3.6 | Informal Extensibility                                  | 78  |

| 3   | 3.3.7 | Distributed                                             | 79  |

| 3   | 3.3.8 | Generality                                              | 83  |

| 3   | 3.3.9 | Conclusions                                             | 83  |

| 3.4 | Spec  | ifications                                              | 88  |

| 3   | 3.4.1 | Nondistributed Systems                                  | 89  |

| 3   | 3.4.2 | Distributed Systems                                     | 91  |

| 3   | 3.4.3 | Specification Language1                                 | .01 |

| 3   | 3.4.4 | Computer Assisted Formal Engineering Laboratory (CAFEL) | .33 |

| 3   | 3.4.5 | Specification Analysis1                                 | .38 |

| ;   | 3.4.6 | Simulationl                                             | 44  |

| :   | 3.4.7 | Conclusionsl                                            | .46 |

| 3.5 | Meth  | odology1                                                | .48 |

| :   | 3.5.1 | Introductionl                                           | 48  |

|     | 3.5.2 | Approximation1                                          | 49  |

|     | 3.5.3 | Decomposition/Integration1                              |     |

|     | 3.5.4 | Elaborationl                                            |     |

|     | 3.5.5 | Optimization <sup>1</sup>                               | .57 |

|     | 2 5 6 | Fyolution                                               | .59 |

.

| 3.5.7      | 7 Conclusions 161                                                                |

|------------|----------------------------------------------------------------------------------|

| 3.6 Des    | sign Principles 163                                                              |

| 3.6.3      | l Formal Methodology 163                                                         |

| 3.6.2      | 2 Closure 165                                                                    |

| 3.6.3      | Unbounded Resources                                                              |

| 3.6.4      | 4 Optimization 168                                                               |

| 3.6.5      | 5 Evolutionary Adaptation 171                                                    |

| 3.6.0      | 6 Conclusions 172                                                                |

| 4. Patient | Monitoring Example                                                               |

| . 4.1 A    | Development Process                                                              |

| 4.2 Ide    | ealized Behavior 179                                                             |

| 4.3 Pro    | ocess Approximation                                                              |

| 4.4 Cl     | osed Loop System                                                                 |

| 4.5 Pro    | ocess Sharing 193                                                                |

| 4.6 Pro    | ocess Elaboration 197                                                            |

| 4.7 A      | Storage Model 199                                                                |

| 4.8 Pr     | ocess and Storage Partitioning 203                                               |

| 4.9 Co     | nclusions 208                                                                    |

| 5. Functio | nal Specification of a Microprocessor                                            |

| 5.1 In     | troduction 210                                                                   |

| 5.2 No     | tation and Organization                                                          |

| 5.3 Ba     | sic Definitions 217                                                              |

| 5.4 Th     | e Central Processor                                                              |

| 5.4.       | 1 Overview 220                                                                   |

| 5.4.       | <pre>2 Definitions for Interprocessor Interaction and Instruction Decoding</pre> |

•

| •          | 5                             | .4.3            | Definitions for Machine Instructions                                              | 229 |

|------------|-------------------------------|-----------------|-----------------------------------------------------------------------------------|-----|

| 5          | 5.5                           | Memor           | ry Processors                                                                     | 244 |

|            | 5                             | .5.1            | Overview                                                                          | 244 |

|            | 5                             | .5.2            | Memory Processor Definitions                                                      | 246 |

| 5          | 5.6                           | The I           | Peripheral Interface Adapter                                                      | 247 |

|            | 5                             | .6.1            | Overview                                                                          | 247 |

|            | 5                             | .6.2            | Peripheral Interface Adapter Definitions                                          | 249 |

| 6. 0       | . Conclusions and Future Work |                 |                                                                                   |     |

| $\epsilon$ | 5.1                           | Conc            | lusions                                                                           | 252 |

| 6          | 5.2                           | Futu            | re Work                                                                           | 255 |

|            | 6                             | .2.1            | Research Area                                                                     | 255 |

|            | 6                             | .2.2            | Overall Approach                                                                  | 263 |

|            | 6                             | .2.3            | Critical Issues                                                                   | 264 |

|            | 6                             | .2.4            | Work Plans                                                                        | 266 |

|            |                               |                 |                                                                                   |     |

| Appe       | endi<br>U                     | x A -<br>sing : | Specification of Asynchronous Interactions Primitive Functions                    | 269 |

| Appe       | endi                          | х в -           | Petri Net Models                                                                  | 292 |

| Appe       | endi                          | ж С -           | Formal Syntax Definitions                                                         | 310 |

| Appe       | <u> </u>                      | an i 172        | An Investigation of Digital System lence in the Context of a Comprehensive Theory | 313 |

| App        | endi                          | х E -           | Index to Definitions in Section 3                                                 | 360 |

THE FORMAL DESIGN AND ANALYSIS OF DISTRIBUTED DATA-PROCESSING SYSTEMS

### L. Executive Ov.

We will start this report with a general structure and results of this res. research has been carried out under Contract 0080 with the Ballistic Missile Defense Systems part of a continuing program to develop the use of data processing architectures in the solution of comple scale real time defense systems.

### 1.1 Payoffs

The major mission payoffs being addressed (however indirectly) are life cycle costs, mission confidence, rapid development, and evolutionary deployment. These payoffs are strongly impacted by such properties as the following:

- · The predictability of development systems

- The efficiency of development systems

- The reliability of development systems

- The adaptability of change of both development and application systems

- The testability of application requirement, design, and realization behaviors

- The reliability of application requirements, designs, and realizations.

The essential attributes of distributed data processing

### (DDP) systems include

- Distribution both logical and physical

- Architectural domain relatively unconstrained

Problem adaptability - fitting architecture to problem

Modularity - independently designed and tested units.

We can thus augment our list of critical properties above by adding simplicity as a property. We must find a way to exploit the modularity of DDP to obtain overall simplicity. Without this overall simplicity, DDP encrmously complicates our development processes. The current state of development methodology is barely adequate to deal with centralized data processing systems. We must find a way to both generalize and simplify the development problems.

e

### 1.2 Research Approach

The critical properties of simplicity and testability dictate that we provide a formal structure to the development process that will prevent large classes of errors and avoid worst case situations that are too complex to resolve. Large scale development processes require substantial automation of the verification and validation tests for any confidence to be established. Even simple changes may introduce undetected inconsistencies, unless they are carried out by tested and automated procedures.

We have developed a generally applicable research procedure that, if followed, will produce a formal development methodology. The procedure is driven by a set of formal specification properties selected to have a high impact on system payoffs. A formal specification language is then defined so that the required properties are testable. A set of analysis

and simulation tools is then developed to provide feedback to a designer. Next, we develop a set of designer selected and guided procedures for transforming specifications. By the use of these automated procedures a designer may start with a very high level (and general) specification (requirements) of a desired system and produce (as a sequence of such procedure applications) a final low level (and detailed) specification (suitable for analysis, simulation, and implementation. And finally, we produce some general design principles that may usefully guide a designer in the selection of the procedure sequences so as to carry out a more reliable and efficient application system development.

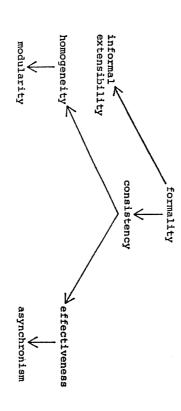

## 1.3 Specification Properties

An informal characterization of the formal specification properties required for structuring a DDP development are given below.

<u>Formal</u>: A specification is formal if it is an abstraction (i.e., a thing representing only a certain set of properties, instead of its literal self] such that its represented properties can be specified precisely. We may thus automate the analysis and transformations of specifications.

Consistent: A specification is consistent if it specifies a unique formal system that is implementable. All errors such as contradictions, omissions, or impossible constraints are automatically detectable.

Effective: A specification itself may be used to gener-

ate automatically a simulation model. Experiments using the simulation may be used to display and analyze the behavior of the specified system.

Homogeneous: Every abstraction of a system must also have a formal specification. The same specification language may be used throughout the development process.

Modular: A specification is modular if it can be partitioned into identifiable components which could be replaced by compatible components, while producing only local and predictable changes in the specified system.

Informal Extensibility: A specification may contain informal (formally uninterpreted) attributes. All relevant information, not currently included in the specification's formal properties, may be associated with specification components. Where our formal methodology does not help, it must not hinder a designer using any informal techniques.

\*Distributed: A specification must be able to define systems composed of asynchronously interacting subsystems. We can then design and study the properties of the subsystems in isolation, knowing that their integration will not produce new or unexpected behavior.

Generality: A specification language is general if there is a specification in the language for every distinct formal system. We may deliberately constrain generality in order to eliminate untestable systems.

This abstract set of properties for specifications are

8 I

critical for creating and comparing formal design theories that will enable the achievement of the potential DDP pay-

## 1.4 Specification Language

system generators. Thus we may design processes as acting processes and an interpretation of such processes computations of the generated system. system designs. have developed a formal model for asynchronously inter-The simulation of a process will display the implicit as

of the word) and algebraically specified. with the addition of some new abstract models for asynchronous tion language is a subset of conventional algebraic notation functions allows a practical and explicit design of interactinteractions called "exchange functions". The use of exchange ing processes (and corresponding systems). The process model is functional (in the mathematical sense Thus the specifica-

strained so that the specification properties described above automatically testable. algebraic specification language is sufficiently con-

that will provide the formal mothodology to a system designer prototype computer assisted formal engineering laboratory specification language was used to start the design

#### 1.5 Methodology

mation and analysis tools, and a set of rules for their use generating specifications, a set of automatable transfor-Our formal methodology consists of a set of procedures

> tions (requirements) and ending with very detailed specificadevelopment process, starting with very abstract specifica-We have constrained our procedures to support a homogeneous tions (hardware and software designs).

veloped. cesses thomselves, as well as those of the systems being de-We can thus formally specify and study such development proprocedure define the new state of the development process. procedures to an initial specification. The results of each consist of the application of some sequence of methodology space of development processes. Each development process will In effect, the set of methodology procedures defines a

for design decisions and control of the locality of changes. a specification. The formal nature of the specifications and cesses. As well as procedures for elaborating and optimizing the development process provides a high degree of traceability ing, changing, decomposing, and integrating development pro-The methodology currently includes procedures for start-

### 1.6 Design Principles

principles must be tested by practical experience to principles that can be plausibly justified a priori. They experience with a methodology, and we have little such excredence. Indeed, most such principles arise from must still be tested by perience as yet. We have done the least work on this area since such We can, however, identify some general experience.

ı 10

critical for creating and comparing formal design theories that will enable the achievement of the potential DDP pay-

## 1.4 Specification Language

We have developed a formal model for asynchronously interacting processes and an interpretation of such processes as system generators. Thus we may design processes as implicit system designs. The simulation of a process will display the computations of the generated system.

The process model is functional (in the mathematical sense of the word) and algebraically specified. Thus the specification language is a subset of conventional algebraic notation with the addition of some new abstract models for asynchronous interactions called "exchange functions". The use of exchange functions allows a practical and explicit design of interacting processes (and corresponding systems).

The algebraic specification language is sufficiently constrained so that the specification properties described above are automatically testable.

The specification language was used to start the design of a prototype computer assisted formal engineering laboratory that will provide the formal methodology to a system designer.

### 1.5 Methodology

Our formal methodology consists of a set of procedures for generating specifications, a set of automatable transformation and analysis tools, and a set of rules for their use.

We have constrained our procedures to support a homogeneous development process, starting with very abstract specifications (requirements) and ending with very detailed specifications (hardware and software designs).

In effect, the set of methodology procedures defines a space of development processes. Each development process will consist of the application of some sequence of methodology procedures to an initial specification. The results of each procedure define the new state of the development process. We can thus formally specify and study such development processes themselves, as well as those of the systems being developed.

The methodology currently includes procedures for starting, changing, decomposing, and integrating development processes. As well as procedures for elaborating and optimizing a specification. The formal nature of the specifications and the development process provides a high degree of traceability for design decisions and control of the locality of changes.

### 1.6 Design Principles

We have done the least work on this area since such principles must be tested by practical experience to gain credence. Indeed, most such principles arise from design experience with a methodology, and we have little such experience as yet. We can, however, identify some general principles that can be plausibly justified a priori. They must still be tested by experience.

### Formal Methodology:

A designer should maximize the use of a formal methodology and minimize introduction of informal steps in a formal development process. This principle will produce a maximum payoff of the design methodology.

#### Closure

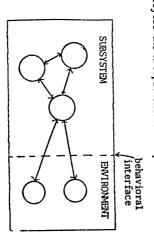

System specifications should be a closure (i.e., defining both controlled and controlling processes) and formal decompositions should be used to factor development processes. The formal analysis and testability of systems is greatly enhanced when both the control system and the environment being controlled are formally specified.

### Unbounded Resources:

A system should first be designed, without conflicts for implementing resources, to a testable level until we have a satisfactory design in all other respects. This principle greatly simplifies the initial design, and ensures that the specified system could work, even if over-designed with respect to some performances.

### Optimization:

An over-designed specification may be optimized by finding an equivalent specification in which redundant resources have been eliminated by introducing resource contention for the remaining resources. Thus the performance may be degraded by such contention in just those places where overperformance has been identified.

## Evolutionary Adaptation:

At each step of a development process, make only those design decisions that are required in order to delegate all of the rest of the design decisions to subsequent steps. This provides maximum freedom of (re-elaboration) changes with minimum scope of consequences. Hindsight is better than foresight. This principle minimizes need for foresight.

The area of design principles is fruitful and little explored. Our formal development methodology will make it possible to formulate such principles precisely and to validate their use. The generality of our design theory makes such research investment and experiments worthwhile.

### 1.7. Future Work

Given the scope of this research effort, it should not be surprising that it is only part of a continuing research project and not limited to this research contract alone.

### Formal Design Theory:

We plan to extend our formal design theory and use it as a basis for comparisons and integration of other method-ologies. In particular, we will explore the integration of our DDP design concepts into the BMD RSL/REVS Methodology.

We plan to extend our formal design attributes into dynamic performance analysis. This will involve creation of a basic theory of resource management.

Computer Assisted Formal Engineering Laboratory (CAFEL):

We plan to complete the design and implementation of a

### Formal Methodology:

A designer should maximize the use of a formal methodology and minimize introduction of informal steps in a formal development process. This principle will produce a maximum payoff of the design methodology.

#### Closure

System specifications should be a closure (i.e., defining both controlled and controlling processes) and formal decompositions should be used to factor development processes. The formal analysis and testability of systems is greatly enhanced when both the control system and the environment being controlled are formally specified.

### Unbounded Resources:

A system should first be designed, without conflicts for implementing resources, to a testable level until we have a satisfactory design in all other respects. This principle greatly simplifies the initial design, and ensures that the specified system could work, even if over-designed with respect to some performances.

### Optimization:

An over-designed specification may be optimized by finding an equivalent specification in which redundant resources

have been eliminated by introducing resource contention for

the remaining resources. Thus the performance may be degraded by such contention in just those places where overperformance has been identified.

### Evolutionary Adaptation:

At each step of a development process, make only those design decisions that are required in order to delegate all of the rest of the design decisions to subsequent steps. This provides maximum freedom of (re-elaboration) changes with minimum scope of consequences. Hindsight is better than foresight. This principle minimizes need for foresight.

The area of design principles is fruitful and little explored. Our formal development methodology will make it possible to formulate such principles precisely and to validate their use. The generality of our design theory makes such research investment and experiments worthwhile.

### 1.7. Future Work

Given the scope of this research effort, it should not be surprising that it is only part of a continuing research project and not limited to this research contract alone.

### Formal Design Theory:

We plan to extend our formal design theory and use it as a basis for comparisons and integration of other method-ologies. In particular, we will explore the integration of our DDP design concepts into the BMD RSI/REVS Methodology.

We plan to extend our formal design attributes into dynamic performance analysis. This will involve creation of a basic theory of resource management.

Computer Assisted Formal Engineering Laboratory (CAFEL):

We plan to complete the design and implementation of a

prototype CAFEL that will support the application of our formal design theory to actual development process experiemnts.

## DDP Development Experiments:

We plan to use our design theory to support DDP design experiments being carried out by the BMD Advanced Technology Center. Ultimately, these experiments will test the validity of our development methodology and quantitatively assess the resulting mission payoffs.

### INTRODUCTION

The work described in this report is a continuation of the previous work on contract DASG-60-76-C-0080 under modification p0004. The following technical proposal was prepared in response to RFQ DASG60-77-Q-0077 and the resulting contract was awarded in January 1977.

## 2.1 Technical Quotation

### 2.1.1 Research Area

The system development process is currently supported by an <u>ad hoc</u> methodology based on informal (English text) specifications. The informal nature of the specification restricts the scope and effectiveness of potential methodology tools. Some systems do get developed in spite of difficulties, and we must accept the fact that our research in methodology should broaden the range of options in the development process rather than specify a uniquely optimal process for all systems designers and customers. This section will discuss the nature of the requirements in the SOW of the RFQ.

## 2.1.1.1 Background (SOW 1.0)

The RFQ is for a continuation and extension of the current work on contract DASG-60-76-C-0080.

### 2.1.1.1.1 BMD Systems

A good review and characterization of BMD systems has been given by Davis and Vick. In particular we quote the following seven methodology requirements from that paper:

- must allow for inclusion of data processing limitations early in the development cycle. This must include the means for assessment of data processing induced system limitations (e.g., processing delays and inaccuracies) as well as the ability to provide accurate estimation of data processing hardware requirements, and support tradeoffs between alternative approaches.

- be developed which insure means for stating the required processing without the inclusion of unwarranted design detail; insure unambiguous communication of intent; provide a means to validate requirements; insure their feasibility; and be responsive to the invariable change.

- -- Design. The software design process must provide a means for earlier error detection, rapid modification, and designed-in reliability. The approach must insure the production of a highly reliable modular product

which will minimize the life cycle costs.

- -- Automation. The system must possess as much automation as possible in every phase of software development. The aids should be such that they provide maximum utilization of the thoroughness of the computer to eliminate many sources of human error.

- -- Management. The system must consist of well-defined phases containing intermediate milestones which provide for measurements and evaluation of progress. Techniques must be devised which allow a priority costing and scheduling based upon a defined, structured approach to development.

- -- Testing. The system must provide means for the allocation of performance to the data processing subsystem, the refinement of that allocation and improved means for the testing, verification and validation of that performance as an integral part of the development cycle.

- be a technology which forces the problem to be stated and structured at a high level, analyzed at that level and then allows the developer to proceed with the addition of detail in an orderly, defined and measurable fashion. This must proceed from early system definition through code delivery in a traceable and flexible manner.

$<sup>^1\</sup>mathrm{C}_{\cdot}$  G. Davis and C. R. Vick, "The Software Development System," Proceedings of the 2nd International Conference on Software Engineering, October 1976,

This technology must assure maximum designed-in reliability in the development cycle.

The intrinsic severity of typical BMD system requirements complicates the development process to a nearly unmanageable extent. This complexity poses serious problems in meeting the methodology requirements quoted above. When intrinsic gate times limit performance and force non-systematic "shoe-horning" of an application onto a centralized data processor, the ability to meet or test system requirements is seriously jeopardized.

# 2.1.1.1.2 Distributed Data Processing

A major potential advantage of DDP lies in the relaxation of the gate time bounds on performance via increased parallelism. If an arbitrary n-system "solution" is used, the development process may become n-factorially more complex. This extra burden would jeopardize the possibility of success in the developmental process. Instead, we can spend some of the DDP performance potential on simplicity. In the limit (probably unattainable) an n-system solution could become one-nth as complex as a one-system solution. In order to obtain this simplicity we must accept sufficient requirement and design constraints (laws) so that the development process becomes simpler and so that requirements can be (and can be shown to be) met.

## 2.1.1.1.3 Formal Specifications

The acceptance of design laws requires that we can test resulting specifications for their consistency with those laws. This is not possible if the specifications are informal. The addition of design laws thus requires increased formalization of the system specifications. This is not enough, however.

We cannot test arbitrary (even formal) system specifications for most properties of interest. The potential (and undetectable) worst case problems will defeat our attempts to analyze and transform specifications. Our proposed methodology must support developmental processes that generate only "well-behaved" specifications that can be tested and implemented.

### 2.1.1.1.4 Methodology

The enforcement of such laws in the development process for large complex systems is impractical unless such enforcement can be automated in specification language design and analysis. The avoidance of worst case system specifications will frequently require an automation of the development process steps that produce that specification. This does not imply an elimination of the designer. For example, an automated tool could generate only canonical structures that are well-behaved as a service to designers searching for a solution. The designer would guide both generation and selection, yet his choices would automatically obey the required laws.

## 2.1.1.1.5 Current Status

We are currently working under Army Research Contract DASG-60-76-C-0080 with the Ballistic Missile Defense Advanced Technology Center, Huntsville, Alabama. These problems have been addressed in that contract. A special report<sup>2</sup> on this work is available and a final report is in preparation.

A brief summary of the current status of this work is given below.

- -- Developmental process.

- A discrete process model has been developed

- -- Requirements specification.

- A top-down derivation of some essential requirements on requirements specification has been developed. Some typical and critical steps have been identified as candidates for methodology improvements.

- -- Formal specifications.

A formal functional specification language and interpretation has been developed. This formalism allows specification of asynchronously interacting systems and processes at varying levels of abstraction and appears to be a suitable vehicle for developing our methodology.

### -- Design process.

Some critical steps have been identified and a top level characterization of the process has been obtained. The crucial aspect is "most local" testability of design decisions.

-- Critical properties of specifications.

In addition to the usual properties of a specification itself, we have explored some additional properties required of the specified system. The most basic of these is that the systems in the complex do run and complete their process steps and can be shown to do so at the specification level (i.e., the question of whether the specifications really specify a system complex). Preliminary design laws to ensure this behavior and its testability have been developed.

-- Top down methodology development.

An approach to the development of a suitable methodology and design science has been explored.

## 2.1.1.2 Objectives (SOW 2.0)

The long term objectives in SOW 2.0 are reasonably clear and need little interpretation. The major problem lies in quantifying such goals and measuring progress toward them.

The short term objectives are designed to build on our previous results and extend the domain of specified system

<sup>&</sup>lt;sup>2</sup>D. R. Fitzwater, "The Formal Design and Analysis of Distributed Data Processing Systems," Computer Sciences Department Technical Report CSTR279, October 1976.

properties, testable at the specification level, to critical problems identified by the previous work.

# 2.1.1.2.1 Define DDP Design Theories

The design process that accepts abstract functional specifications and produces DDP process specifications must be elaborated to provide the basis for the specification of methodology tools to support it. This study must be top-down and systematic with respect to the selected properties. This objective must be met prior to tool development and prototype demonstrations required in the long term objectives.

# 2.1.1.2.2.2 Define Critical Real-Time Properties

Performance testing and prediction is a vital part of the development methodology. We must find design laws that will enable us to model, analyze, and predict performances from specifications. We must also find design laws that simplify the required real-time performance testing process for DDP systems.

# 2.1.1.2.3 Conduct Requirements Analysis

We plan to extend current studies of the requirements specifications process and its associated methodology, and develop specifications for tools and requirement specifications. The resulting specifications should be suitable for input to the design process discussed above.

# 2.1.1.2.4 Define Evolutionary Processes

Changes at requirements, design, implementation, and operational levels are inevitable. If we design for change, we may decrease their impact and increase the domain of feasible changes. Evolutionary processes that will support such changes, at each of these levels must be designed. Again, the necessary price will be accepting sufficient design laws to allow evolutionary process models to be used.

# 2.1.1.2.5 Identify Potential BMD Payoffs

Plausible arguments must be developed to support estimates of BMD payoffs. The important impacts of the developing methodology on the developments of real-time DDP systems must be identified.

# 2.1.1.3 Research Requirements (SOW 3.0)

The previous work on contract DASG-60-76-C-0080 will be continued and extended to real-time systems. In each of the areas discussed below, critical issues will be identified and potential solutions developed in the context of the previous work. In each area, a critical comparison with other representative state of the art methodologies will be made, and the problems will be identified.

# 2.1.1.3.1 Distributed Data Processing Design

The contractor will develop procedures useful for transforming data processing subsystem requirement specifications into process specifications for a network of virtual, high level, machine-independent systems. The specifications and procedures should be suitable for designers to encode and analyze functional assignments to nodes and to processes within a node.

This process will include system decomposition and integration steps as well as canonical generation of both control and data structures. Functional analysis and simulation procedures are also required.

## 2.1.1.3.2 Real-Time Systems

The contractor will identify critical properties for real-time systems that, if present, will decrease required real-time testing and increase the scope of effective testing against requirements. Sufficient conditions on the developmental process to ensure these critical properties in the resulting design, and corresponding design laws to make them effective will be developed. Tools for applying the required analysis and testing will be specified.

Dynamic models suitable for either analysis or simulation must be developed, and design laws sufficient to make the models applicable must be developed.

## 2.1.1.3.3 Evolutionary Processes

The contractor will identify critical specification properties that, if present, will limit the impact of evolving requirements or design changes. Sufficient conditions on the development process to ensure these critical properties in the resulting specifications, and the corresponding design laws to make them effective will be developed. Tools for applying the required analysis and testing will be specified.

Meeting this requirement will involve a formalization of such evolutionary processes and a careful structuring of interactions in the evolving system.

## 2.1.1.3.4 Requirements Analysis

The contractor will assess the impact on the data processing subsystem requirement specification of the properties and conditions developed above. The contractor will specify development guidelines and analysis tools sufficient to ensure those properties and conditions.

Each system property required by the development methodology may generate design laws or guidelines for any previous stage of the development process. Some Qf these will even have implications on requirement specifications.

## 2.1.2 Overall Approach (SOW 3.0)

The general approach described by the previous contract reports will be followed in this research work and appears to

be a satisfactory basis for this work. Because of the complex nature of this research, details of the approach must be produced, tested, and elaborated during the work. We can identify some of the required tasks as discussed below. Undoubtedly others will also be required.

# 2.1.2.1 Formal Specifications (SOW 3.1-3.4)

The formal functional specifications previously developed must be extended as required to support the other tasks. This work will produce a specification language and procedures for analysis and simulation of the specified systems.

since the formal specifications form the representation medium for encoding requirements and design decisions, we must study equivalence relations as a foundation for optimization of the design process. More relaxed sufficient conditions for algorithmic implication will be developed and extended to characterize more general system complexes. Formal functional simulation procedures must be developed that allow study of the behavior of specified systems at any level of abstraction.

# 2.1.2.2 Distributed Data Processing Design (SOW 3.1)

Both static and dynamic models for system decomposition/ integration will be developed to support performance impact analysis of proposed design decisions. Procedures for encoding control and data structure design decisions and their organization into a formal automatable methodology and requirements for such tools will be developed.

# 2.1.2.3 Real-Time Systems (SOW 3.2)

There appear to be three aspects to this task. The first is the analysis of critical reflex paths in a specified system to demonstrate that they are bounded and provide a model of performance coupling with other paths. The second is to simplify the performance surface (e.g., to ensure that it is convex) and thus simplify real-time testing. The third is to find sufficient design laws to minimize the required real-time testing. We plan to pursue all three possibilities.

# 2.1.2.4 Evolutionary Processes (SOW 3.3)

This is a relatively unexplored area and the critical issues must be identified. Our formal specification methodology will allow us to define a domain of evolutionary processes.

We will then develop sufficient conditions such that the changes can be analyzed, controlled and automated with minimal and predictable impact on the remainder of specifications. The model for virtual networks involved in DDP design will also be required to define potentially reachable evolved systems.

# 2.1.2.5 Requirements Analysis (SOW 3.4)

The requirements methodology based on our formal specifications will be elaborated and a small (hand worked) example will be developed as an illustration and as a source of experience with the methodology. Additional analysis and simulation tools will be specified.

### 2.1.3 Critical Issues (SOW 3.0)

addressed. The following are some of the critical issues to be

# 2.1.3.1 Distributed Data Processing (SOW 3.1)

- Equivalence. What are equivalence classes? Which requirements? members are optimal with respect to performance

- ļ Distributed data and control models. How suitable are the proposed virtual networks? What canonical structures are sufficient?

- i Decomposition/integration models. Particularly into path coupling via resource contention is modeled. application and virtual operating systems such that

- Functional simulation. What techniques are applicable and how can they be exploited?

# 2.1.3.2 Real-Time Systems (SOW 3.2)

- į Conditions for path flow analysis and prediction for boundedness and performance.

- i Resource mapping and contention resolution properties required for simple performance surfaces.

- 1 Interaction conditions that minimize, localize, and simplify real-time testing.

# 2.1.3.3 Evolutionary Processes (SOW 3.3)

- -- Definition of domain of evolutionary processes.

- -- Localization and delegation of design decisions.

- -- Specification analysis of required process

invariances.

-- What are required process invariances?

# 2.1.3.4 A Requirements Analysis (SOW 3.4)

- How to develop example prior to development of methodology tools.

- ļ How to compare with current methodologies.

### 2.1.4 Work Plans

university. No subcontractors or consultants will be employed. Wisconsin utilizing the normal facilities and equipment of the We plan to carry out the work at the University of

### 2.1.4.1 Computer Usage

The use of computers is anticipated in the following areas:

- -- Date base management.

- -- Document and report generation.

- -- Prototype tool development.

- i Analysis experiments.

- Utilization of BMD software development systems for:

- Experience

- Comparision

- Embedding evaluation

A portion of this work must be done at the ARC due to the availability of the BMD systems. Part of the remainder can be done either with BMD or university computers. Some data base and document generation work may be best carried out on university computers.

We plan to utilize university computers, terminals, and DAIN lines to access the BMD computers.

The majority of the computer work will be carried out next summer after the critical experiments and tools have been specified. Estimation of computer usage at this time is very difficult, but we anticipate that ten hours of CDC 7600 time at the ARC would not be unreasonable. Flexibility in this figure would be potentially helpful.

### 2.1.4.2 Research Effort

This technical quotation is for an increased level of support to pursue the identified issues. The staff for the spring semester will be increased but limited by the availability of qualified candidates. Maximum staffing will be reached this summer coincidental with the increased computer program developments. I plan to work on this contract on a half-time basis during the spring semester, full-time during the summer, and half-time in September for the fall semester The majority of the staff will be highly qualified graduate students working on (or preparing for) Ph.D. theses in the

area of this contract, while finishing their studies. The quality of work will be such that the major results should (and will) be published in appropriate technical journals, and meetings. A small amount of clerical help will also be required.

### 2.? Organization

The major results of the research effort are presented in section 3 on "A Theory of Design." We then present a sequence of examples of formal specifications of a "patient monitoring system," and a complete formal specification of a microprocessor system. We then conclude with a summary and an outline of future work.

### A Theory of Design

The major results of our work are described in this section with references to more detailed discussions in appendices. We develop a theory of design for distributed data processing systems suitable for complex, large scale, real-time ballistic missile defense systems.

The developed design theory is, of course, not complete. It is sufficiently developed to have a major impact on systems development and software engineering technology.

The developed design theory does provide a firm theoretical basis both for further development of a viable science of design and for further specializations for ballistic missile defense system applications.

### 1 Research Approach

The task of creating a suitable system design theory is even more complex than using it to support a system development process. We have no real hope of formalizing the creative activities involved in producing a design theory. We can, however, provide some useful factorizations of the theory developments process into simpler and solvable subproblems.

We will introduce and informally describe a useful decomposition of a research process suitable for developing design theories for many classes of application systems. We will introduce a simple model of system development processes, distinguish between system development and theory development problems, and present a procedural description of a plausible research process. The validation of this research process is of course in its application. The process described seems to have broad applicability and has been used in developing a theory of distributed data processing system design.

We will start with the postulate that our design theory will be a formal theory. That is, it will be possible to decide what the design principles are and formally analyze what they do to a design. This means that the principles will be well defined, teachable, and transferable between both designers and projects.

We will also postulate that we want a design theory suitable for large scale (more than a dozen developers)

development processes. The scale requires substantial design automation to prevent, detect, or correct designer errors. The extent to which large scale automation can be carried out is directly constrained by the formalism of the design theory. We will postulate that the specification must be modular in order to control complexity and support practical automation.

## 3.1.1 Discrete Processes

First we will introduce the concept of an abstract discrete process and distinguish between system development problems and theory development problems.

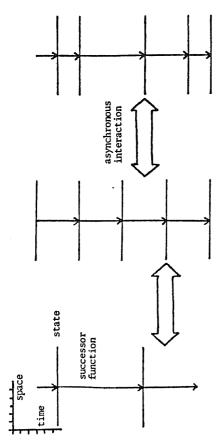

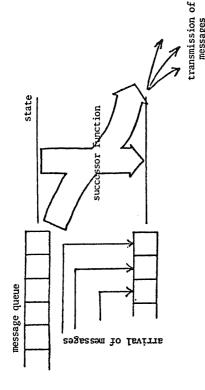

A discrete process is a state space and a relation between elements of that state space. An evaluation of the successor relation applied to a subset of the process state space and producing a subset of the process state space is called a process step. A discrete process may thus be interpreted as a generator of a set of computations.

A computation is a sequence of state space elements. The relation of a discrete process may be applied to the first member (an initial state) of a computation to generate a second member. The relation may also be reapplied to each new member of the computation to produce a successor member. This successor state generation is a computation step.

For example, if the state space N is the set of integers and the successor relation R is "increment by any prime number,"

the discrete process (R,N) will generate (among others) the computations 3, 6, 11, 18, 21, . . . and 3, 5, 7, 9, 11, . .

Both the state space and the successor relation may be defined in terms of primitive components whose nature is not formally specified. These primitive components need not be simple and may subsequently be elaborated into more elementary primitives. Thus we may also define abstractions of discrete processes that are also discrete processes defined in terms of more abstract primitives.

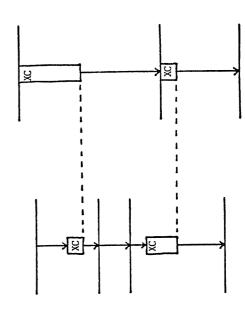

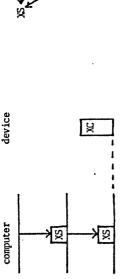

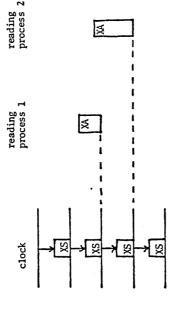

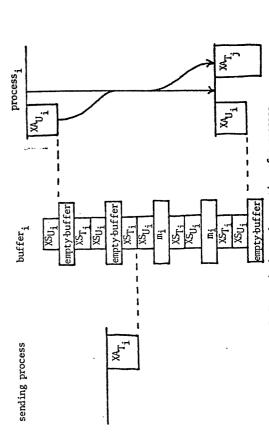

The concept of discrete processes can be extended to include asynchronously interacting processes and to apply them to both system and development processes. For this discussion we will use only the simpler discrete processes defined above.

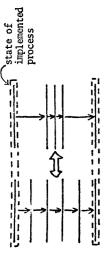

It is important to remember that we distinguish between research, development, and system processes. A research computation corresponds to the development of a design theory. A development computation corresponds to the development of a particular system design. A system computation corresponds to the operations of an implemented system design.

## 3.1.2 System Development

A system development process might be quite unstructured and formalizable only in terms of the final design specifications. We could still abstract all such processes as discrete processes in a trivial fashion. For example, any development process specified as (D,S), where D is a primitive

relation and S is the null set unioned with all possible design specifications, generates only computations of the form { }, "final specification." Only the "final specification" has a nontrivial formulation. The designer must leap to the right conclusion in just one step of the development computation.

Clearly, we wish to develop a much richer model for development processes so that we may support it with a useful and automatable methodology. We cannot do this for an arbitrary process such as (D,S) above since it is not subject to any further formal constraints.

state space of such processes will be specifications at various transformations to be carried out during a process step. abstract discrete processes, and leave all nondiscrete defined by the designers actions in producing a successor levels of abstraction. The successor relation will be informally of the power of our design theory will be the range of aspects will not formalize all aspects of system development. specification. Clearly our abstract development processes the (informal) treatment of the remaining aspects. impossible. can be will postulate that all development processes will be usefully formalized. We can formalize some aspects without prejudicing One measure That is

Our hypothetical development process can thus be described as being in a design state (that specifies the relevant design decisions) that is transformed by the designers into a new

design state that specifies the current design decisions. Thus a particular system design sequence is a computation of the development process.

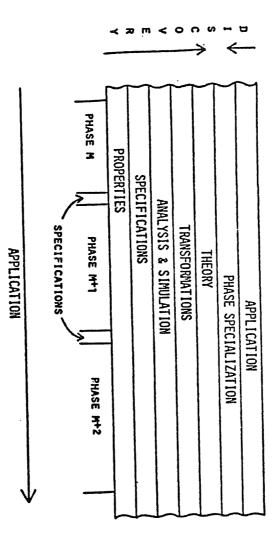

The generation of a system design via such a computation in a single step is vastly too complicated. We will thus want to support development processes whose computations consist of many (much simpler) steps. We may also wish to define subsequences of a computation as phases. A phase of a development process is a member of a partition of the computations generated by that process. The types of design decisions may be quite dependent on the phase of the development process.

Typical examples of development phases are requirements, process design, implementation, deployment, etc.

Each phase or computation step thus focuses on a more specialized system development problem (i.e., how do we get from this state to that state?). This is one way to partition a design problem into separate problems. Such design problem partitioning is essential if the designer is to succeed. There are other very important system development process decompositions that must be developed as part of an application design theory. This is a vital subject but it is outside of the scope of this metatheory discussion.

The phase type of development partitioning focuses on more detailed and simpler subproblems involving system design decisions. Unfortunately, this partitioning does not simplify

37

the design theory problems involved, since the theory of how to go from one state to some subsequent states is largely independent of which phase is involved. The complete solution to a development problem in one phase, no matter how narrowly constrained may require results from an entire methodology or design theory. There can be some theory specializations for given phase but we must first find the more general theory before we define specializations. We must thus find a different and more useful partitioning into subproblems for our research process to develop the required design theory.

## 3.1.3 Design Theory Development

The research process required to generate a particular design theory could also be formalized but this is unnecessary for our purposes. In the absence of a satisfactory design theory, we will happily settle for a useful theory rather than a theory of such theories. We will thus treat the research process quite informally. Further, until we have a useful design theory, arguments about a better one are premature. We are not after an optimum theory (how could you even tell if you had one?) but rather a useful theory. Elaborations, evolution, and experience will then get us a better theory.

We will thus postulate a particular research "computation" that will result in a design theory. This "computation" may not be optimal, but it has the essential virtue of being practical and we can (and have) carried it out to produce a

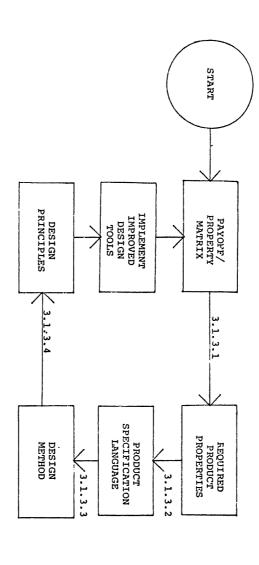

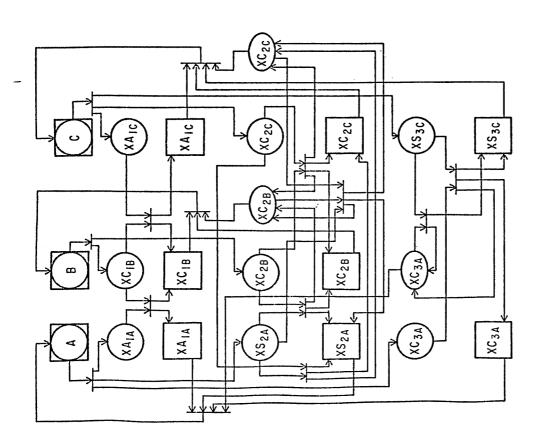

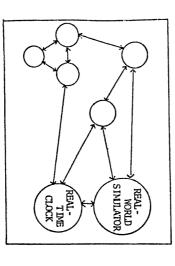

postulated research "computation" is, of course, in the usefulness of the resulting theory. This approach is intuitively plausible and is far from a random selection. There seems little point in elaborating a discussion of how and why we created this particular approach. It can stand on its own results. A brief description of the overall research Figure 3.1-1.

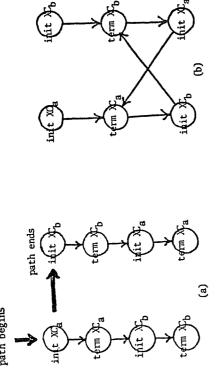

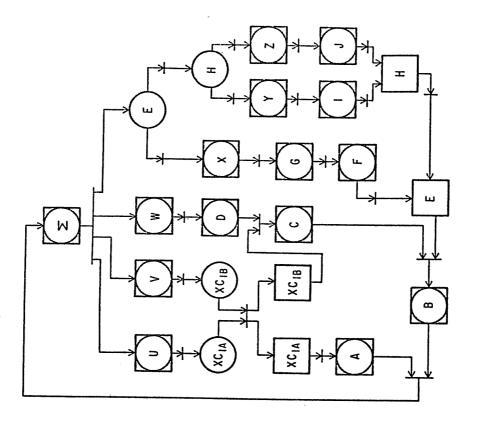

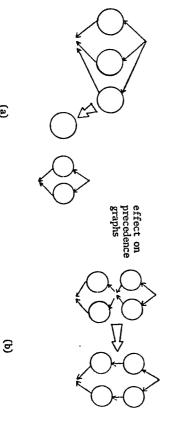

The basic problem discussed in this section, is that of decomposing the research process so as to simplify its steps. We can illustrate the relationship between development process partitioning into phases and the research process decomposition described by this research approach in Figure 3.1-2. The source of our previous difficulty with phase decomposition is now obvious. No matter how small a development step we focus on, we need the results of all of our research process steps to support it. Thus such focusing does not simplify our research problem. Our approach first identifies and develops those aspects common to all steps, second focuses on special phase sensitive problems, and third develops the application sensitive specializations.

A more detailed discussion of Figure 3.1-1 is given below, and constitutes an informal description of our research

Figure 3.1-1 A Research Procedure

The section numbers on the arrows refer to the corresponding discussions.

## 3.1.3.1 Payoffs to Properties

attained or improved by the resulting design theory and a characterization of the most significant properties of the development processes supported by that design theory. These payoffs and properties must generate requirements on our design theory rather than on an application design to be produced using our design theory. We can then study the impact of those significant properties on the desired payoffs. We may be able to develop explicit functional relationships between them, in which case we can transform the payoffs into objective functions of development attributes and can quantify the "goodness" of the design.

of specializations of the design theory. system development) will be of little use in developing a that will permit a quantitative prediction based on development process. development may be a highly desirable payoff of a development that identifies major dependencies. general theory. those that could only be obtained by monitoring a particular cannot be predicted in an application independent way (e.g., develop a qualitative (or semi-quantitative) impact matrix For many, if not all properties, we will only be able We do not have a formal model of development speed It is important to note that dependencies that They may be used in the latter development For example, rapid ţ

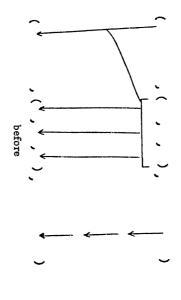

### DEVELOPMENT PROCESS

Figure 3.1-3 Research vs. Application Processes.

An application development will normally proceed from left to right through phases. A theoretical research development will flow from bottom to top. An empirical research development will flow from top to bottom by generalizing from application experience in a phase sensitive way.

This analysis then generates a set of critical properties that should be present for all development processes supported by the design theory we wish to develop. If we quit now, we would still have generated some useful results that could provide guidance to designers. However, we need not stop and we can easily proceed to the next step.

# 3.1.3.2 Properties to Specifications

Given the set of properties produced by the previous procedure, we can identify a subset of them that are properties of the system being developed. We now postulate that any allowable system specification must have these system properties or can be practically tested for them. This is the source of major requirements on our design of system specification languages. Clearly such properties are not sufficient to generate a unique specification language nor are they sufficient to completely characterize a specification language. They do represent necessary constraints on specifications.

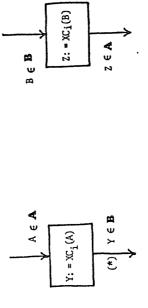

A formal language is a set of strings over a vocabulary of characters generated by a formal grammar. A specification language is a subset of a formal language such that each sentence in the language can be practically tested for the necessary properties. A system specification is thus a sentence in a specification language that is interpretable to include the design decisions and to characterize the specified system.

Note that all specifications in a specification language must be practically testable for the necessary system properties.

It is unlikely that we will have thought of all such properties the first time around. Good judgment on the part of the researcher is just as essential as good judgment on the part of the designer using the resulting theory. Iteration of this research procedure will clearly be required. However, the resulting design theory may be quite sensitive to the ordering of such properties created by incremental iterations.

We must start with the most basic properties on which other properties are dependent. For many applications of this research approach, we may actually be able to establish a partial ordering on the properties such that the existence of a later property is dependent on the existence of the previous properties. This property dependency ordering would itself provide valuable guidance to designers.

We can see in advance the need for a specification to be suitable for the automatic generation of the behavior (computations) of the specified system. Without such feedback, the designers must be severely handicapped. They could not even test hypotheses about the effects of their design decisions. We will postulate the necessity of this property for our design theory.

If we quit now we would have developed a system specification language that will allow verification of the

presence of these necessary basic properties. We also have a precise way to specify current design states and design decisions as well as design problems. This alone can significantly improve our ability to formulate, communicate, and solve design problems. The required properties can be automatically tested. We can now go on to the next step, a methodology.

# 3.1.3.3 Specifications to Methodology

A methodology consists of a set of procedures for producing specifications, automated tools to support the procedures, and rules as to the applicability of each procedure and tool. An <u>effective procedure</u> is one that can be carried out even if it will never complete. An <u>algorithmic procedure</u> is an effective procedure that will terminate in a finite time we will postulate that the procedures of our methodology must be effective at least. We cannot hope to make all such procedures algorithmic.

The range of the methodology procedure (viewed as implementations of relations) is a set of specifications. We can define a homogeneous methodology as a methodology whose procedures have domains that are a subset of their ranges. We can now define a homogeneous development process that is implemented by a homogeneous methodology as (D,S) where S is a system specification language and D is a set of predicates (defining the applicability rules) and relations (defining the methodology transformations). Such a development computation

starts with an initial system specification and finishes with a final system specification.

A homogeneous methodology is not very interesting if all specifications in the specification language have totally disjoint behaviors since there would be nothing in an initial system specification that is relevant to any subsequent system specification and thus it could just as well be bypassed. This repeated bypassing leads us to the trivial development process that we have already rejected as useless.

We will thus postulate that a specification language must have a specification for each member of some hierarchy of system abstractions for each final system specification in the specification language. The homogeneous development process can thus start with a very abstract system specification and end with a very detailed system specification. We now have an interesting development process model.

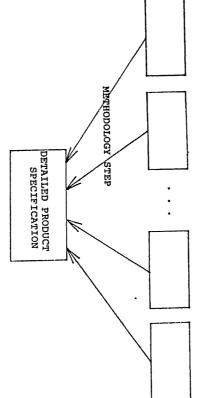

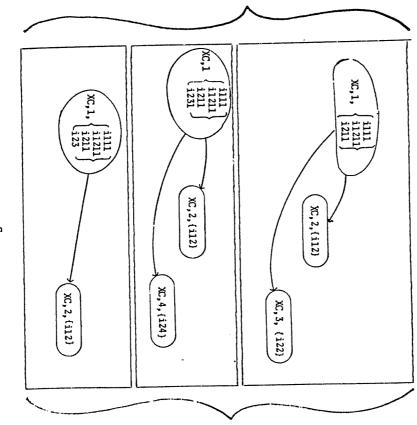

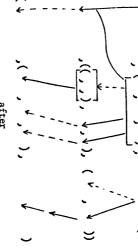

We can identify potential procedures for our methodology by working our development computations in reverse, as shown in Figure 3.1-2. In effect we can take a final system specification and ask "from what more abstract specification could we define a procedure that could get us this final specification?". Each such procedure is a potential candidate for our methodology. We can then iterate with the new starting point to find a more abstract starting point. One measure of the power of our methodology is the degree of abstraction

### POTENTIAL VERY ABSTRACT

### STARTING DESIGN STATES

PRECEDING STATES

ABSTRACT

Figure 3.1-2 Design Processes

Each state is a "sentence" in a specification. A development "computation" will be some path from a particular starting design state to a final detailed product design.

of potential starting points for which there exists a development computation supported by that methodology.

A weak methodology might require us to start with some final system specification and thus provide no assistance to the designer. A strong methodology might start with a very abstract system specification at the system requirements level and end in a detailed final implementation specification.

procedure. Suppose our specification language consisted of other forms of defining expressions, this procedure alone is clearly a candidate for our methodology. When augmented by defining  $P(X,Y) \equiv F(G(X), H(Y))$ . Thus a defining procedure primitive) is a way to get from P(X,Y) to F(G(X), H(Y)) by boration (defining a primitive function in terms of other F(G(X),X,Y be functions. Let F, G, and H be primitive functions and let simple arithmetic expressions involving primitive sets for primitive functions that allows function composition is by our defining methodology sufficient to allow us to start from P(X,Y) and develop an computation of the homogeneous development process implemented arbitrary arithmetic expression with two arguments using a Perhaps an admittedly trivial example will clarify this members of some primitive set of values. H(Y)) has a valid abstraction in the form of P(X,Y)is a new primitive function. The procedure of ela-The expression

The essential points of this methodology development procedure are that we need only study abstractions of a given specification language and that we can at least guarantee the existence of some development computation from any of the resulting set of abstract starting specifications. This does not guarantee that a designer will be able to discover a valid sequence. We must also develop some design principles to guide the designer.

We will postulate that there must exist a way to recognize that a procedure of the methodology has ended. We may place further constraints on such procedures but this one seems universally required. It is essential to demonstrate that a given computation step is finished before we can go on to the next one. The methodology procedure need not be algorithmic, since a designer may fail to complete the development step, fall back to some previous specification, and try another sequence of design decisions. We must at least know that it has produced a valid successor that we cannot recognize. In that case we must assume that it has not ended.

This seemingly obvious postulate has some important ramifications and is a serious constraint on our methodology. For example, a typical development process step in current use is that of writing a computer program to implement some program specification. We do not have (currently) any way in general

to decide if the resulting program is a valid successor and does implement the specification. Thus this "normal" step is disallowed in our methodology except for specialized cases where consistency between the program and the specification can be shown. This rules out most of the current programming activities. If our methodology is successful, contemporary programming techniques will be radically altered.

produce a better solution with less cost. using an algorithm for generating each potential solution. procedures. A heuristic procedure is an effective procedure alternatives. One of them is discussed below and uses heuristic let us hasten to point out that there are several viable while completing the computations step with any one of them. heuristic procedure is designed to generate all valid successor some designer to guide the generation sequences so We can also define interactive heuristic procedures that allow for generating a set of potentially desirable solutions that requires intensive guidance by the designer to In its most automatic form, the procedure simply generates the design choices and still generate only valid successor states states in a development process, the designer can make random practically useful. step in Lest the reader become discouraged by this realization, successor state first and we have an algorithm for our its least automatic form, we have an "idiot" procedure If the interactive as to

# 3.1.3.4 Methodology to Design Principles

Our research process will produce development processes whose computations start with an abstract system specification and end with a detailed system specification. Each computation corresponds to some sequence of application of our methodology procedures. Many of these sequences may be nonterminating may require too many resources to carry out, or may result in a poor final design specification. Indeed, it can be assumed that a development computation is quite impractical unless it has been carefully selected. We clearly need more in our design theory.

Our methodology just concerns itself with carrying out particular computation steps. We must also develop some design principles to select suitable starting points and sequences of methodology application. We can usefully distinguish three kinds of design principles.

The first kind consist of absolute laws that delimit what is possible and result in a waste of effort if not obeyed.

We have a rich source of such absolute design laws in the formal impossibility of most of our design tasks (unless we place serious constraints on both the developmental and the system processes). For each thing that cannot be done, we can derive a corresponding absolute law which says "don't do that thing" and accept the burden of accomplishing our design some other way. For example, we must not use an arbitrary

methodology procedure in a development process, since we cannot test its correctness.

condition which, if met, will guarantee that we violating one of the design laws. conditions as additional design principles. They are neither determine that we are not. not violating a design law. absolute laws (that say you must do it this way) nor unique step, the classically unsolvable "halting problem" less restrictive conditions or extremely useful special cases. find better ones. With analysis and research we may find For example, if we do not specify looping within a process The second kind of design principle is a sufficient we may find the more useful ones and use them until we may be many such sufficient conditions). With experi-We can accept such sufficient In general we may not be able We must know that we are are not

The third kind of design principles simply embody design experience. "We tried this in a similar case and it worked better than that." Our formal theory development will not discover many of these kinds of principles itself. It may, however, provide useful generalizations of such experience. It will also provide a formal way to embody such experience and transfer it to other designers or projects.

Having come this far we can use the resulting design theory to design and implement a design laboratory system for

interactive design. We can then use that laboratory to test and extend our design theory.

We can also iterate on our research approach and build more specialized design theories based on more specialized aspects of our development processes. This will then extend the power of our formal design theory to ensure essential properties.

### 3.1.4 Conclusions

The research approach described in Figure 3.1-1 will, if carried out, result in a design theory. It can be carried out. The "goodness" of the resulting design theory will be dependent on the skill and judgment of the researcher as well as on the complexity of the systems to be designed. Such goodness can be assessed by measuring the desired payoffs on application experiments. However even a poor theory will be better than no theory, and the last section points out how even a poor theory can evolve to a better one through research and experience.

The resulting design theory will be well defined, formal, transferable, and teachable. It will also provide a way to profit from design experience in a formal way. These are essential attributes for a viable design theory.

From experience, we can surmise that the last, application sensitive specializations should be made only by experienced application engineers and designers. Thus it may well be more

effective to teach our basic design theories to the engineers and leave it to them to finish the application specialization. This is also a practical consequence of our formalization of basic design theory.

There may be many other approaches to decomposing a research project to produce a design theory. Ours will work. How well it will work is up to the researcher. It is a suitable starting point for the development of a science of design. We have used this research approach to develop an initial theory of design for distributed data processing systems. It worked and opened up a large new domain of automatable design tools, and provided new insight into an emerging science of design.

# 3.2 Distributed Data Processing Systems

We now have an informal research plan for developing a design theory. Before we can specify the development process properties that we will use for this theory of design, we must look at the general application area of large scale real time control systems. We are particularly interested in the use of distributed data processing architectures in the design of such systems. We will compare some important development payoffs and some relevant distributed data processing characteristics via an impact matrix. We will then develop some initial critical issues (payoffs) for our DDP design theory.

## 3.2.1 Development Payoffs

The major areas in which the current state of the art imposes severe constraints in the development of large scale real time control systems are discussed below.

## 3.2.1.1 Life Cycle Costs

The life cycle costs for large scale systems are severely constraining and prohibit development of all but the most critical systems. Even many critical systems must be prohibited because cost and benefit tradeoff studies rule them out. We need to lower life cycle costs substantially if we are to usefully exploit the potential of such large scale control systems. An analysis of life cycle costs indicates that by far the biggest cost factors lie in nonhardware areas of specification, design,

implementation and "maintenance." This last factor is dominant and is clearly misnamed. Bits do not wear out. Instead, we could more accurately call this area correction, redevelopment, and evolution.

## 3.2.1.2 Mission Confidence

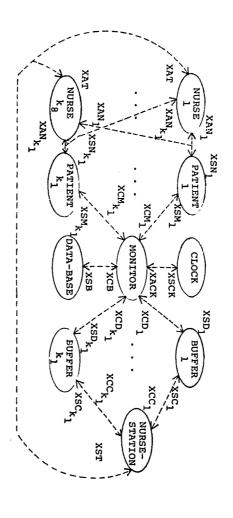

There are two aspects to mission confidence. The first is, "Will the developed system design, if properly implemented, perform the required mission?" The second is, "Will this system realization, if properly operated, perform the specific immediately required mission?" The answer to both questions requires an understanding of system flaws.