# THE FORMAL DESIGN AND ANALYSIS OF DISTRIBUTED DATA PROCESSING SYSTEMS

by

D. R. Fitzwater

Special Report-Preliminary Design Analysis

Computer Sciences Technical Report #279

October 1976

University of Wisconsin - Madison

Computer Sciences Department

THE FORMAL DESIGN AND ANALYSIS OF DISTRIBUTED DATA PROCESSING SYSTEMS

BY

#### D. R. FITZWATER

Special Report-Preliminary Design Analysis

Computer Sciences Technical Report #279

# Abstract

This research proposal is to support the development of the "science" behind software engineering in order to ensure required system properties, to compare current software engineering techniques, to develop specification for new designs and analysis tools, and to demonstrate the practicality of the "science".

A hierarchical design schema will be developed within which formal representations and analyses can be defined and the required solutions can be found. Since "worst case" problems are generally impossible to solve, sufficient design laws or constraints will be developed to ensure solvability of the critical problems.

# TABLE OF CONTENTS

| 1. | INT | NTRODUCTION                        |    |  |  |  |  |  |  |  |

|----|-----|------------------------------------|----|--|--|--|--|--|--|--|

|    | 1.  | INTRODUCTION                       | 4  |  |  |  |  |  |  |  |

|    | 2.  | OBJECTIVES                         | 21 |  |  |  |  |  |  |  |

|    | 3.  | RESEARCH PLAN                      | 23 |  |  |  |  |  |  |  |

|    | 4.  | SPECIAL REPORT                     | 24 |  |  |  |  |  |  |  |

| 2. | REQ | UIREMENTS SPECIFICATION            | 26 |  |  |  |  |  |  |  |

|    | 1.  | INTRODUCTION                       | 26 |  |  |  |  |  |  |  |

|    | 2.  | INFORMAL DECOMPOSITION/INTEGRATION | 31 |  |  |  |  |  |  |  |

|    | 3.  | FORMAL DECOMPOSITION/INTEGRATION   | 34 |  |  |  |  |  |  |  |

|    | 4.  | SYSTEM PARTITIONING                | 36 |  |  |  |  |  |  |  |

|    | 5.  | PRIMITIVE ELABORATION              | 40 |  |  |  |  |  |  |  |

|    | 6.  | REQUIREMENTS PROCESS SUMMARY       | 42 |  |  |  |  |  |  |  |

| 3. | FUN | CTIONAL PROCESS SPECIFICATIONS     | 44 |  |  |  |  |  |  |  |

|    | 1.  | INTRODUCTION                       | 44 |  |  |  |  |  |  |  |

|    | 2.  | SYSTEM SPECIFICATIONS              | 47 |  |  |  |  |  |  |  |

|    | 3.  | INTERACTION SPECIFICATIONS         | 53 |  |  |  |  |  |  |  |

|    | 4.  | SYSTEM COMPLEX SPECIFICATIONS      | 58 |  |  |  |  |  |  |  |

|    | 5.  | SUMMARY                            | 61 |  |  |  |  |  |  |  |

| 4. | REAL | L-TIME SYSTEMS 6                         | 3   |

|----|------|------------------------------------------|-----|

|    | 1.   | DEFINITIONS                              | 3   |

|    | 2.   | PATH BOUNDS                              | 5   |

|    | 3.   | NON-REAL-TIME TESTING 6                  | 8   |

|    | 4.   | SUMMARY                                  | 0   |

| 5. | DIS  | TRIBUTED DATA-PROCESSING SYSTEMS         | 1   |

|    | 1.   | INTRODUCTION                             | 1   |

|    | 2.   | SYSTEM DECOMPOSITION/INTEGRATION         | 2   |

|    | 3.   | BRIEF OVERVIEW OF THE NETWORK DESIGN     | 6   |

|    | 4.   | GENERALITY                               | 5   |

|    | 5.   | SUMMARY                                  | 5   |

| 6. | THE  | DESIGN SCHEMA                            | 7   |

|    | 1.   | INTRODUCTION                             | 7   |

|    | 2.   | DESIGN PROCESSES                         | 7   |

|    | 3.   | DESIGN STEPS                             | 9   |

|    | 4.   | DECOMPOSITION, OPTIMIZATION, INTEGRATION | 2   |

|    | 5.   | DESIGN PROCESS SUMMARY                   | 6   |

| 7. | CON  | CLUSIONS9                                | 8   |

|    | 1.   | SUMMARY                                  | 8   |

|    | 2.   | EVALUATION                               | 8   |

|    | 3.   | FINAL REPORT                             | 9   |

|    | 4.   | ACKNOWLEDGEMENTS                         | 1:9 |

| APPENDIX | A | <br>FUNCTIONAL PROCESS SPECIFICATIONS      | • | • | • | • | • |   | 100 |

|----------|---|--------------------------------------------|---|---|---|---|---|---|-----|

| APPENDIX | В | <br>CONDITIONS ON EXCHANGES                | • |   | • | • |   |   | 104 |

| APPENDIX | С | <br>VIRTUAL NETWORKS AND OPERATING SYSTEMS |   |   |   | • |   |   | 107 |

| APPENDIX | D | <br>EXAMPLE OF A FUNCTIONAL SPECIFICATION  |   |   |   | _ | _ | _ | 151 |

-3-

The Formal Design and Analysis of Distributed Data Processing Systems

#### 1. INTRODUCTION

This special report presents a summary of the current status of work under Contract DASG60-76-C-0080 with the Department of Defense, Army, Huntsville, Alabama. The intent of this report is to document the results of the review of the current state-of-the-art critical problems, development of a "top down" approach, and proposals for more detailed solutions.

All of the results here must be considered as preliminary and subject to change and elaboration as this work proceeds. The problems are complex and certainty of results comes (if then) only when the study is completed with respect to a set of properties.

## 1.1 Introduction

Experience has shown that the specification, design, implementation, and development of complex real-time weapons systems, such as ballistic missile defense systems, are very expensive, difficult to test adequately, slow to develop and deploy, and difficult to adapt to changing requirements. [Da 76] The introduction of distributed data processing concepts potentially complicates these problems even more. No development of

<sup>[</sup>Da 76] Davis, C. G., and Vick, C. R. "The Software Development System," Proceedings of the 2nd International Conference on Software Engineering, San Francisco, California (October 1976), p. 60.

science or design and testing tools will make such development automatic or simple. The engineering decisions will remain complex and dependent on experience and analysis. As in all other engineering fields, the development of a science of design, however incomplete, can be very valuable in guiding engineering decisions, analyzing consequences, providing design laws sufficient to guarantee some desirable system invariancies, and in avoiding "worst case" type designs thus making possible more powerful analysis tools.

Sponsored by The United States Army under Contract No. DASG60-76-C-0080

# 1.1.1 Critical Issues

There are many critical issues in the process of developing and deploying a major system. We cannot hope to address directly most of them. We must address some of them in a way that minimally constrains potential solutions to the others. If we can't solve all of the problems (and we can't), we mustn't prevent others from doing their best on unsolved problems while expoiting our results on those problems we have attacked. We will look first at the problems of making and testing engineering decisions with the goal of making the development process more manageable and engineering decisions more testable at earlier stages of development. We believe that such results could have a major (but indirect) impact on many other critical issues. Even if this were not the case, we believe that a relatively minor investment in better models, design laws, and testing tools will have a large payoff in both the resources involved in development, in speeding up the deployment, and in improving the adaptability of the resulting system<sup>[Dr 76]</sup>. The final validation of this belief will rest on use of the processes developed in this work.

We will first give an informal characterization of a developmental process. A formal specification of a particular set of desirable developmental processes is one of the intermediate goals of this work. We will start with a very general concept and gradually develop it into a formal and practical scheme for system development.

If the development is to be formalized, the current state of the development must be well defined at the beginning and at least at the end. The passage from one well-defined state to the next will be called a step of the process. Most useful developmental processes will proceed

<sup>[</sup>Dr 76] Dreyfus, J. M., and Karacsony, P. J. "The Preliminary Design as a Key to Successful Software Development," Proceedings of the 2nd International Conference of Software Development," San Francisco, California (October 1976), p. 206.

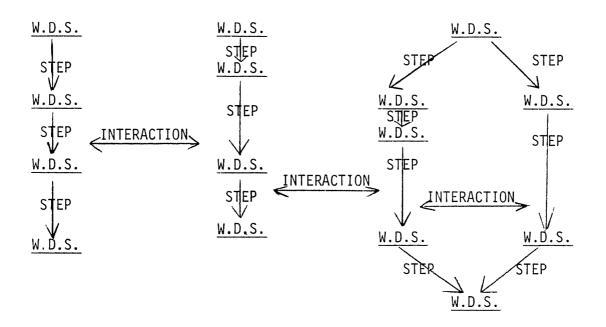

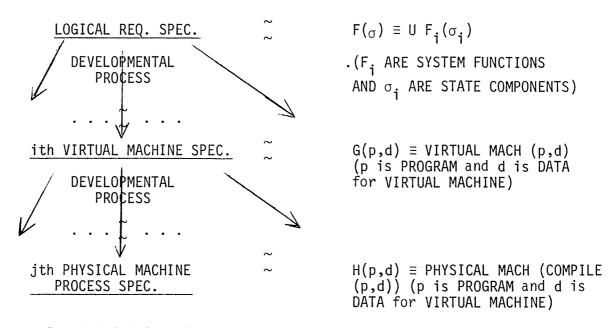

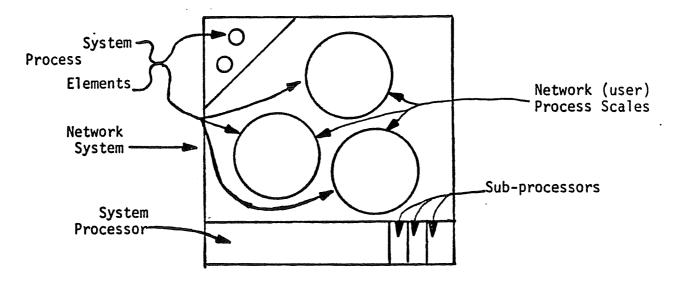

via many successive intermediate well-defined states. Of course there may exist any algorithm for carrying out a given process step, and most developmental processes are not guaranteed to succeed, given arbitrary originating requirements. Thus the developmental process is similar to ordinary digital processes, except that its steps may not be effective (i.e. there is no automatic way to carry out a given step) as is shown in Figure 1. Developmental processes may be decomposed into independent or interacting processes, just as can digital processes. Indeed the most general model of developmental processes is just that of digital processes. The notion of "interaction" must be formalized as well as that of well-defined state.

Of course many digital processes do not model a desirable (or even feasible) developmental process; we must still sort through our models to find those with desirable properties.

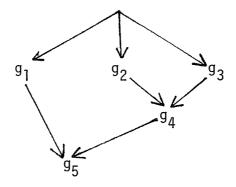

FIG. 1: An interacting set of digital processes with interacting and non-interacting steps. The process is effective if each step is effective. W.D.S. represents "well-defined state".

We can identify at least the following processes involved in a system development process:

- . Requirement (of the designed system)

- . Design (of the specification of the system)

- . Implementation (of the specified system)

- . Evolution (changes in design during operation)

- . Operation (of the implemented system).

Each process has its own unique requirements for kinds of engineering decisions, of analysis, and of testability. However, all of these processes have much in common, and a general model with properties useful to all of them can be developed. At that high level of abstraction, all such results can be used for any of the above processes. In developing such an abstraction, we must find requirements for all such processes. Finding these becomes a "meta-process" itself.

We will address the relevant critical issues arising from the processes above in the order given. Thus this preliminary report will be most concerned with the top two processes and the "meta-process".

# 1.1.2 Requirements Process

The requirements process starts with some (possibly incomplete, vague, and informal) originating requirements for a system that approximate the desired system, and finishes when the modified and elaborated requirements have been encoded (in a form suitable for the subsequent design process) and tested (to the satisfaction of the system engineers and the "customer"). The steps in the requirements process are of three types: the elaboration of requirements for an approximating system, the modification of requirements to those for a better approximation of the desired system, and the decomposition of the overall desired system into more manageable sub-systems.

There are critical issues involved with both the starting point and the ending point as well as for each type of step in the process.

- 1.1.2.1 At least the following critical issues are involved in the startand ending points of the requirements process:

- . What should be required?

- e.g., Behavior in real world being affected by system,

Behavior at interface of real world and system

Functional structure of system

- . What attributes should be constrained?

- e.g., Which are bound by requirements?

Which are strongly coupled (engineering decisions cannot be factored)?

Which are loosely coupled (engineering decisions can be made independently within a parametric range)?

- . How should requirements be encoded?

- e.g., To make possible the testing of the requirements

To make possible the design of the required system

To maximize applicability of tools and analysis

To check for consistency, completeness, etc.

To ensure that designed system is testable with respect to requirements.

Under worst case conditions, none of the above questions have satisfactory answers, so we must find design laws for requirements that make satisfactory answers possible.

- 1.1.2.2 At least the following are involved in a decomposition step:

- . Decompose into what parts?

- e.g., Abstractions

Sub-systems

Levels

- . How can requirements be allocated and tested?

- e.g., Testable in part

Testable only on collection of parts

Coupling between engineering decisions between parts

- . How can parts be integrated?

At which stage of elaboration

With minimal testing during integration

The decomposition must consider the subsequent integration and must make integration possible while maximizing the probability that requirements will be met.

- 1.1.2.3 At least the following are involved in a "better approximation" step:

- . How good an approximation is it? (It should satisfy customer.)

- e.g., How to test behavior of required system

How to compare with desired behaviors

How to compare two approximating systems

- . How can deficiences of approximation be corrected?

- e.g., Given analysis data, what are the deficiencies?

Should we change requirements or the desired system?

What can we change to correct deficiency?

What is impact of change on other requirements?

- . How can the impact of change be determined?

- e.g., Either desired system or approximating system may change

What other requirements are impacted?

Which need to be changed?

Which need to be retested?

Since the question of "...better approximation to what?" must remain formally unanswered (or we would just change our starting point to an earlier form of requirement), we can not hope to use formal correctness proof techniques on originating requirements. Consequently we can only maximize the analysis information available to the customer and system engineers.

- 1.1.2.4 At least the following are involved in an elaboration of requirements step:

- . Which process is constrained by the requirement?

- e.g., Requirements

Design

Implementation

Etc.

- . What type of testing is required?

- e.g., Stochastic

Analytical

Simulation

Operational

Etc.

- . How can requirements be elaborated to a testable level?

- e.g., Which parts to elaborate

How to elaborate only part

Minimal design exploration

It is clear that, for a system engineer, the nature of this type of step is essentially the same as for later design steps on the resulting requirement specification. Thus there can be no qualitative dividing line between requirements specification and design specification processes. If possible, the requirements process must be carried far enough in design

to satisfy the system engineers (and the customer) that requirements are satisfactory and can be met.

The issues involved in requirement specifications are here addressed in quite general and imprecise terms just to indicate the scope of the problems. We will elaborate on many of these issues in a more formal way after we introduce the appropriate models and tools.

# 1.1.3 Design Process

The design process "starts" with some encoding of the requirements (satisfactory to the customer and systems engineer) and completes with the production of some encoding which meets design requirements and is suitable for implementation designers. Requirements may have been decomposed into relatively independent design requirements. There are six types of design steps: change of requirements, the elaboration of design decisions, the optimization of the specification, the decomposition into more manageable parts, the integration of the decomposed parts, and the interaction with other design processes. There are critical issues associated with both the initial design requirements and the resulting implementation specifications, as well as the design steps.

- 1.1.3.1 At least the following critical issues are involved in the starting and ending points of the design process:

- Is the state of design well defined?e.g., Is it consistent, complete, unambiguous and testable?

- Is it suitable as input to subsequent development processes?

e.g., Can we decode information needed for development step?

Can the development process steps be carried out?

Can we decide if they have been carried out?

We can not hope to give algorithms for developmental processes, but we can at least insist that the current state of a developmental process is well defined and that we can decide when a given step has been carried out.

- 1.1.3.2 At least the following are involved in the interaction between decomposed design processes:

- . Is the interaction well defined?

- e.g., Is it consistent, complete, unambiguous, and testable?

- . When should interaction occur?

- e.g., What independence of design decisions is allowed with loosely coupled design processes?

How to test for and when to synchronize interaction

- . What should interaction be?

- e.g., What information should be exchanged?

When is interaction completed?

The decomposition of the system requirements leads to semi-independent design processes, but some loosely coupled attributes may require interdesign process interactions.

- 1.1.3.3 At least the following are involved in an integration process step:

- . How can decomposed system be integrated into one system?

- e.g., Are both simply connected by interactions?

Does one interpretively simulate the other?

Is one translated into processes of the other?

- . Is the integrated system well defined?

- e.g. Is it consistent, complete, unambiguous, and testable?

- Does integration preserve designed properties?

- e.g. If separate systems are "correct", is the integration

"correct"?

- Is it at least probable that individual design decisions remain valid?

Since we will control, as part of our formal methods, the types of decompositions, we can hope to resolve these issues with algorithms for integration.

- 1.1.3.4 At least the following are involved in a decomposition step:

- . Are the decomposed systems well defined?

- e.g. Are they consistent, complete, unambiguous, and testable?

- . Can they be integrated?

- e.g. Can issues above be resolved?

- . Can associated non-decomposable requirements be tested?

- e.g. For consistency during decomposed design processes

For satisfaction after integration step.

There may exist some requirements that can not be decomposed and can only be tested at system integration time.

- 1.1.3.5 At least the following are involved in an optimization step:

- What are invariancies characterizing an equivalence class?e.g. What must be preserved?

- . What property of members of the equivalence class is to be optimized?

- e.g. Given two equivalent members, which is preferred?

- . Is it decidable if a proposed member is better than the currently designed member?

- e.g. Can we quit an optimization step because we are ahead?

We may be able to require more of some specific optimization steps. In general, we can not require less and know when the steps can be considered completed.

- 1.1.3.6 At least the following are involved in a design elaboration step:

- . Is the result a well-defined sytem?

- e.g. Is it consistent, complete, unambiguous and testable?

- Does it preserve validity of previous tests?

- e.g. Does validity of this system imply validity of previous system?

- . What design decisions are made?

- e.g. Elaboration encodes design decision in more detailed structures.

- . To what requirements are design decisions traced?

- e.g. What tests must be carried out on result of step to verify and validate decisions?

- . How can the design by elaborated to a testable level?

- e.g. Which parts to elaborate

How to elaborate only part

Minimal implementation

Ideally, all design decisions should be testable at the completion of the design step.

- 1.1.3.7 At least the following are involved in a "change in requirements"

step:

- · What originates the change?

- e.g. Design decisionsChanges in an originating requirementCorrection of error

- · What is the change?

- e.g. How defined?

How testable?

- · What is impact of change?

- e.g. Local to step

Local to design

Local to subsystem

- . Should change be made?

- e.g. Is cure worse than disease?

Are there alternatives?

- . How can change be made?

- e.g. With minimal impact on current and completed design processes

Changes will occur. We must deal with them effectively and with minimal impact.

The design process ends when the designer has produced well defined specifications for the systems that will collectively meet design process requirements and that can plausibly be implemented. This may require exploratory development beyond the design process prior to producing the final design. Thus we can not hope to draw neat formal lines between the various parts of the development processes. We can, however, hope to characterize the steps of the entire developmental process, leaving decisions such as where dividing lines should be drawn for a given project to the manager who should make them.

# 1.1.4 Computer Sciences

It is clear that the computer sciences are potentially as useful to system developers as physics and mathematics are to engineers. Little of this potentiality has been realized in practice because of the complexity of current systems and because of some unique problems in justifying scientific systems research.

The areas in computer sciences have developed only recently from application efforts in many disciplines. As a result computer sciences

departments in each university have been created in differing administrative frameworks and with a wide variety of emphasis on areas of specialization. This is not surprising for a science that is so new and so potentially useful to society, as well as to the university community itself. Although there is general agreement that the area, as an academic discipline, exists quite apart from the many applications of computers to problem solving, it is only beginning to justify the use of "sciences" in its title.

There seems to be general agreement that the area of "systems" is at the heart of computer sciences. There is little agreement on what constitutes the systems area and what the university effort should contribute to this area. It is clear that a substantial body of knowledge concerning the design, specification, implementation, measurement, and control of digital systems has been developed. Such knowledge is potentially useful in providing tools and application systems for all users of computers.

Because of the current lack of a consensus on the nature and standards of this new area of "systems", some special problems have arisen in exploiting research contributions by professors in this area. The major problem in systems research evaluation is intrinsic to the area. Perhaps an analogy will clarify the problem. A mathematician may study artificial universes with a formal rigor that carries its own justification. A physicist may study our real universe without hope of formal rigor, and may justify his studies by the insights and control of natural phenomena. An engineer may use both mathematical and physical tools in designing applications useful to society, and may justify them by that usefulness. Com-

puter sciences has analogs to each of the above areas. For the mathematician we have the "foundations" area, which is concerned with problems of formal systems. For the physicist we have a developing science of the design of artificial systems, which is concerned with technology-independent system universes too complex to have been formalized. For the engineer we have the implementation of systems in given technologies. We can distinguish both hardware and software engineering as subfields of systems engineering.

The justification of the foundations area is much the same as for mathematics, and the justification of the engineering areas is as usual. The system area, however, suffers from a serious problem in finding its justification. Because the system universes are artificial, we can not say (as does physics) that any insight or control into that universe is justified. Physics has a unique, self-justifying universe. The system research does not. Neither can such work be justified as mathematics, since the artificial system universes being studied are too complex (so far) to be formalized. The system researcher has a double burden. He must not only justify his solution to a problem, he must also justify the universe within which it is a solution.

Most of the contemporary systems research has been carried out in the context of different, local, universes—the locally available computer system. Each such system defines a set of constraints which creates many problems local to that system. This localization has fragmented system research into rather isolated user groups. The problems and solutions of one group are of little direct use or interest to other such groups. The informed, interested peer group to such system researchers may be very small indeed, perhaps including only local co-workers. With time, these isolated efforts will sig-

nificantly contribute to the contribution of more abstract (machine-independent) system universes within which a substantial community of workers may produce broadly applicable results. A universe is neither created nor justified in a day or by a few applications.

The complexity of requirements for contemporary and future system developments is so great that there is serious question of how to deal with it. Indeed, the principle result of computer sciences today is to demonstrate how impossible worst-case developmental processes are to specify and carry out. That is not much help. We can not deal with worst-case complexity. Thus we must accept as a primary postulate that if something can't be done, then we must accept sufficient effective design laws so that we don't have to do it. There are a number of corollaries to this postulate, such as:

- . Never work with arbitrary systems

- . Encode so that required decoding is possible

- . Never accept unconstrained design decisions

- . Generate only well-behaved structures

- . Only replace a restrictive design law by another that is still sufficient.

- . Satisfaction of design law must be practically testable

- . If an algorithm is too computationally complex, then it can't be carried out.

- . We must constrain the system being required, not just the form or its description.

- . Detection of arbitrary cases is usually not possible. Prevention is then the only cure.

One of the major reasons contemporary system engineers have not resolved the critical issues mentioned previously is that, in terms of arbitrary systems requirements, they have no solution.

We resolve these issues if we accept the above postulate, but at the risk of restricting the system domain to trivial systems. A major goal of this work is to show that we don't really lose anything essential from our systems domain by accepting that postulate. Unfortunately, much work remains to be done before we reach this goal. Surprisingly, our major hope of reaching this goal rests on the complexity of the applications. We can not hope to analyze value manipulations in any general way, and so we must encode most requirements and design decisions in a structural way. Even so, the intrinsic problems are so complex that unless we can make the development steps formally trivial, they will be at least computationally impossible, even algorithms are not enough for us.

Thus our major problems are extrinsic (that of how to define the problem structures and processes) rather than intrinsic (that of finding a solution to the defined problems). We can't possibly use most of the sophisticated analysis techniques because of combinatoric computational complexities in large complex systems. If we define our problems correctly, the solutions are not hard. We may balk a bit at some of the resulting design laws, but this will serve as a motivation for developing better design laws and developmental processes.

In effect, we must approach the developmental process not as a

mathmatician (the complexity is too great for analytic solutions) but as a physical scientist interested in system invariancies. We can develop a hierarchical approach that will ensure the most basic and essential design properties and provide the foundation for future elaboration.

The formulation of such design laws provides a common basis for surveying, comparing, and evaluating current and proposed methodologies.

Indeed, the most immediate impact of this study will lie in such critical evaluation and identification of potential improvements of high payoff. Ultimately, the system restrictions should make possible the creation of new developmental processes and tools applicable within that restricted domain.

# 1.2 Objectives

The objectives of this proposal are to develop the following hierarchical approaches:

- . to the "science" of design behind software engineering,

- . to demonstrate the practicality of the science,

- . to compare current software engineering approaches,

- to develop specifications for new design and analysis tools.

In order to reach these objectives, it is necessary to develop design schemata, required system properties, and formal models. Each of these areas will, of course, require cycles of study and elaboration into hierarchies of greater depth. No one area could be completed without commensurate studies on the others. A significant amount of work in at least the following areas will be required to meet the objectives above.

# 1.2.1 Design Schemata

The design process itself must be formalized to provide a framework within which problems can be studied and solved. The goal is to allow maximum factorization of the design process itself into independent designs, while providing a suitable level in the design schema for making all required decisions. For each design, a suitable design schema should encompass the functional, process, and implementation design problems. The formalization of such a schema requires the creation of system universe models within which decisions and laws may be defined.

## 1.2.2 Required Properties

Some properties of a particular system are valid only for that system and must be ensured by means appropriate to that system. Many required properties seriously impacting the possibility of achieving performance, integrity, evolution, and design automation can be identified and used to drive the creation of design laws and models. The hierarchical classification of these properties is essential for designers to select the level of the design laws appropriate to each design step. The certification of real time systems alone, requires a substantial number of required properties to be present. Debugging can only display errors, rather than show that there are no errors.

#### 1.2.3 Formal Models

Each hierarchical design schema applied to a factored design problem will require an appropriate model and formal system for representing design laws and decisions.

It is clear that the design problems are insoluble in terms of unconstrained models. We must find the reasons for such impossible solutions and "pass" effective design laws sufficient to make them solvable. Ultimately, such laws will be incorporated in high level design and analysis languages to free the designer from unnecessary details, and to ensure consistency.

The models and design laws should be sufficient to allow algorithmic analysis of design to show presence of required properties, to allow creation of useful tools and techniques for design otimization at each level and for translation to the next level, and to reduce computational complexity of design, analysis, and transformation tools to practicality.

#### 1.3 RESEARCH PLAN

There are five major problems that must be addressed as a set:

- . What are developmental process requirements in general?

- . What hierarchy of system properties should be established?

- . What sufficient design laws are needed to support the hierarchy?

- . What developmental process can best incorporate the design laws?

- . What encoding of the state of a developmental process should be used?

To limit the scope of the current work in a "top down" fashion, we will restrict the hierarchy of system properties to be studied here to only a few, most basic ones relevant to critical issues of real-time, distributed data processing systems. We will treat the developmental pro-

cess by first considering requirements specification and then design processes. After completion of this restricted study of the above set of problems, we will have a basis from which to address the remaining objectives. At that point we will develop a research plan to extend the relevant hierarchy of properties, to extend study to later stages of the developmental processes, to compare potential system engineering approaches, to develop specifications for new design and analysis tools, and to assess potential payoff for the results.

Because of the tight coupling between the potential solutions to the above problems, we can not solve them in order. We will instead develop approximate solutions to each and iterate until all are consistent. This iteration is not completed as yet and so current results must be tentative. We will do this first for the requirement specification process. Even so, we must less formally explore subsequent developmental process stages to assess the validity of requirements methodology. In effect we are in a developmental process for developing developmental processes.

#### 1.4 SPECIAL REPORT

The purpose of this special report is to document the current status of the research in order to consolidate and form a firmer basis for the future work, and to facilitate the decomposition of this work into more manageable sub-problems. Up to this point, the concepts and results have been changing too rapidly to document. This report con-

tains an overall framework and enough detail to identify and factor the problem into relatively independent parts.

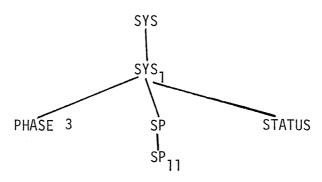

We will develop a model for the requirements process in section 2, and a model with a detailed instance of a formal specification of the state of a developmental process will be presented in section 3. A brief characterization of real-time data-processing systems from the point of view of requirements specifications and relevant properties will be given in section 4. A similar treatment of distributed data processing systems is given in section 5.

With the previous results in hand, we will then turn our attention to the design process in section 6. Our current conclusions and plans for remaining work on this current contract will be discussed in section 7.

Of course, results from these later sections will have to be fed back into the requirements methodology and used to critically compare current methodologies. This has not been carried out as yet because we first needed the firmer foundation provided by this report.

#### 2. REQUIREMENT SPECIFICATIONS

We will develop, in this section, a model for the requirements specification process based on general principles applicable to any system.

Subsequent sections will extend the model to real-time and distributed data-processing systems.

## 2.1 Introduction

The starting point for a requirements process must inevitably be some informal, incomplete, and possibly inconsistent desired behavior for a system. The requirements process must produce a well-defined, complete, consistent, unambiguous, and testable set of system requirements ensuring that system behavior will be satisfactory to the customer and that the required system can plausibly be designed and implemented. The resulting requirements specification must also be suitable for the remainder of the developmental process.

#### 2.1.1 Formal Approximations

Clearly we can do nothing formally with the originating informal requirements; we face the "worst-case" problems. After development of requirements design laws from our later study of developmental processes we can hope to improve the suitability of originating requirements.

After all, there is no unique set of requirements for a given system and if we understand what makes one set better than another, we could use the better set to avoid some problems. In any case, the following arguments remain valid.

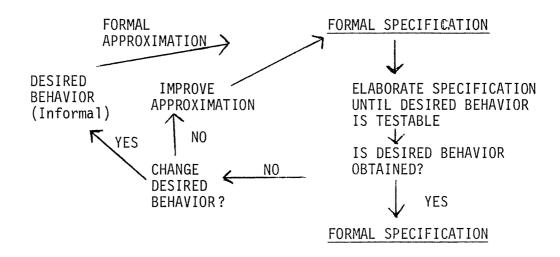

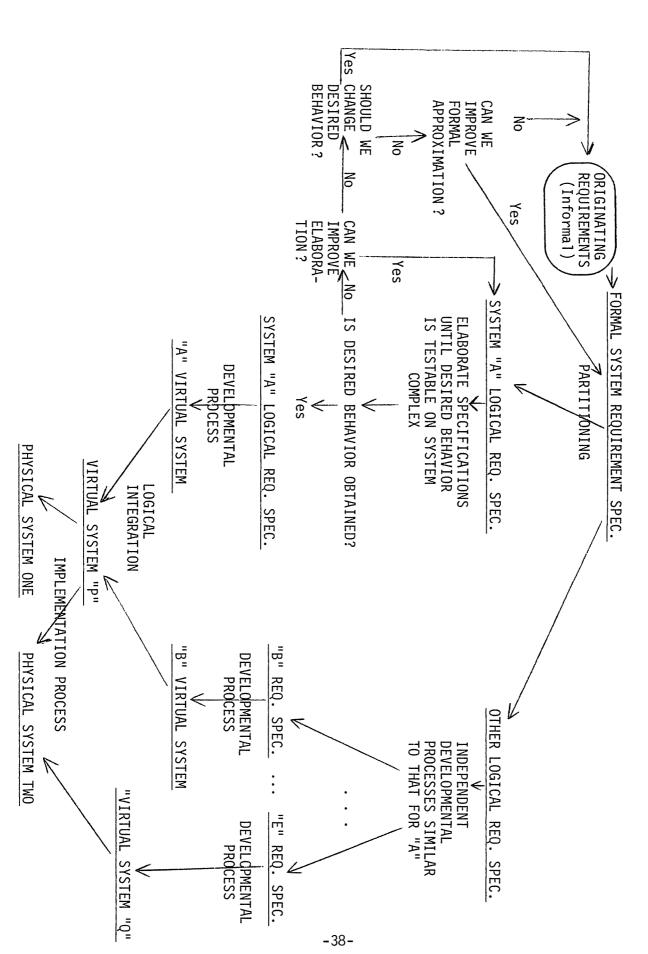

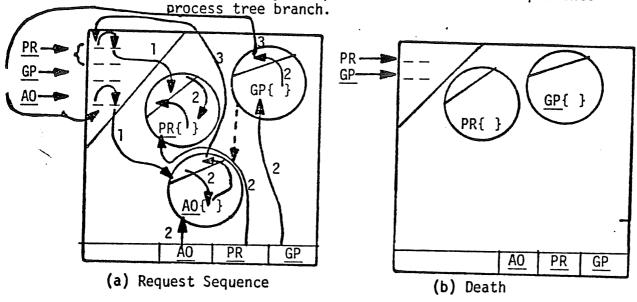

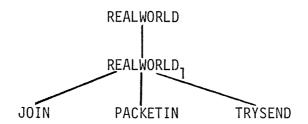

Clearly we must develop an approximate set of requirements which we then refine by elaboration and testing until the requirements process is completed. If we interpret "approximate set" as a vague, informal set, we can offer little or no formal assistance in carrying out the process. We can, however, require that the "approximation set" precisely and formally specify a system whose behavior approximates the desired behavior. In this case we can offer substantial formal assistance to the process since the approximating system is well defined. The resulting process is described by Figure 2. We can thus proceed from one well-defined requirement set to another, using formal analysis tools at each step, until the desired requirements have been produced.

FIG. 2: REQUIREMENTS SPECIFICATIONS PROCESS

We do not hope to deal formally with all attributes of a system. Only some will be constrained by our formal requirements specification. The remainder are not formally treated, and any desired methodology can be utilized for their elaboration and testing. Our formal tools will not replace all other methods. In fact, their role will be supplemental and optional. They may very likely become the framework within which an arbitrary methodology can be embedded.

## 2.1.2 Required Properties

We can immediately derive a number of properties our formal requirements specification must have if this process is to be carried out. Some of these are clearly the following:

- . Well-defined: we must be able to decide if proposed approximation is suitable for our analysis tools.

- . Consistent: behavior must be well-defined.

- . Unambiguous: which behavior must be specified.

- . Complete: all behavior, at a given level of detail, must be specified for those attributes to be formally treated.

- . Effective: it must be possible to determine if a specified behavior is possessed by the required system.

- . High level: the primitives of the specification must be as complex as desired since level of detail is an important management and analysis parameter.

- . Traceable: changes must be traceable in their impact on current "approximate" specification.

- . General: system engineers should not be unnecessarily constrained in the systems they can require. Some constraints will be necessary to avoid worst-case problems.

We can provide automated analysis tools to decide if a proposed approximation does indeed have these properties. We will accept the need for these tools as a constraint in developing our formal specifications.

### 2.1.3 Elaborating Specifications

We may use combinations of any of the process steps described in section 1.1.2 to elaborate the requirements until the desired behavior can be tested. Clearly this could be a complex and lengthy process. It is, however, simply the developmental process we are producing. Potentially, each approximate requirements specification may have to be carried arbitrarily far through the developmental process prior to testing. We would like to develop design laws and developmental processes that minimize such effort. The primary attack will be to factor and only elaborate to the level of detail specifically required for testing. Details of this approach are developed in later sections, and some forms of decomposition and partitioning will be discussed in this section.

We will be able to exploit our entire formal design process results in assisting in this part of the requirements specification process.

#### 2.1.4 Testable Requirements

The requirement that the specification must be effective has significant impact on both the form of the specification and the form of the informal requirements. There is no problem with simple requirements which can be tested in an <u>ad hoc</u> analytic fashion, but most requirements will be too complex to be tested without simulation. "Effective" is thus equivalent to a simulation specification. Ideally, all types of simulation should be applicable to our formal specification, and our requirement specification is equivalent to a simulation model. This equivalence must either be an identity or there must exist a practical algorithm for deriving the simulation model from the requirements specification.

Because of our data processing background, we view the simulation model as a digital simulation. The extreme versatility of digital simulation techniques made this hypothesis plausible even if some suspicion remained that it was not a satisfactory decision for non-data-processing systems. A closer look at contemporary requirements processes, however, substantiates the validity of the hypothesis. Even radar designers frequently prefer to start with (and elaborate) a digital simulation that encodes the requirements in an effective way. Digital simulation is the most common tool used in developing requirements.

It is also worth noting that the testability requirement applies to all stages of the developmental process. Thus we have not, as yet, developed any reason for using different formal specifications at each stage. The difference from stage to stage lies in the level of specified detail rather than in a qualitative difference.

The originating requirements may be for an open or for a closed system. The specification of a closed system includes the "environment" in which all interactions take place. An open system may include an interface specification to the "environment" but does not include that "environment". An open system is not testable without a specification of an environmental driver.

The requirements specification must be closed to be testable. This may be done either by specifying system, interface, and driver or by simply specifying the closed system that includes the environment. Both options must be possible. However, we can maximize the scope of our

formal techniques if the formal requirements approximation is the closed system. The partitioning of the closed system into system, interface, and "driver" could be done subsequently in a formal way if desired. Such a partitioning may not always be feasible or desirable, particularly at the initial informal level. The closed system specification is a complete and consistent specification whereas the open system, interface, and driver specification (informally arrived at) need be neither complete nor consistent and undetectably so in the worst case. We will, therefore, start our formal specification as that of a closed system.

Requirements elaboration can thus take place jointly in the environment and system models with a homogeneous technique. We can "design" and test the detailed environment at the same time and in the same manner as the system interacting with the environment.

Thus we can provide substantial and automated assistance in verifying behavior of the required system. Indeed the requirements process does not end before the customer is satisfied with displayed behavior.

# 2.2 <u>Informal Decomposition/Integration</u>

A large system development will have many attributes that are only very loosely coupled, for example, the physical site design and the data processing design. Design decisions local to different design processes are not sensitively coupled and, within predesignated limits, may be made quite independently. Thus some forms of decomposition can be carried out at the earliest stages, thus factoring the development process into independent processes until the corresponding system integration occurs.

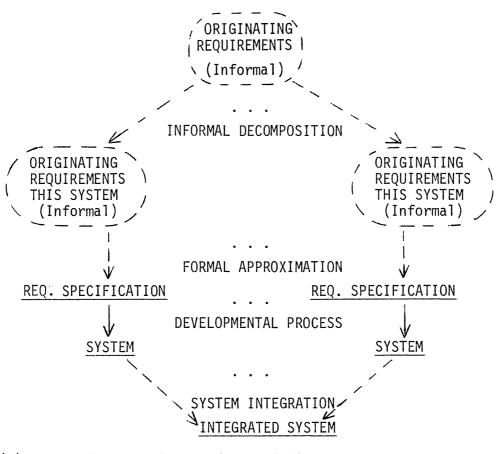

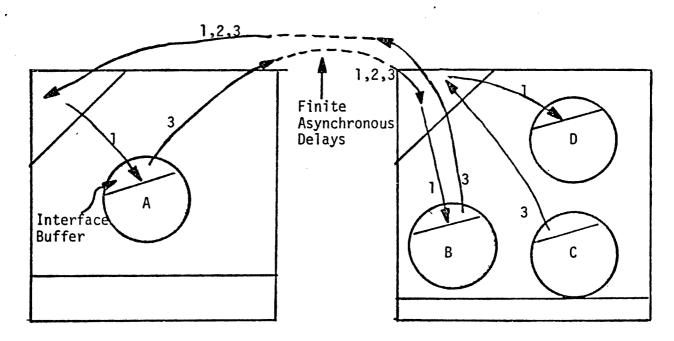

The earliest possible point of decomposition is in the informal originating requirements as shown in Figure 3a. Following the arguments of section 2.1.4, we will decompose into closed systems by identifying tightly coupled subsets of attributes that are only loosely coupled with other subsets. Then by partitioning the attributes we can specify a closed system approximation for each attribute subset. The decomposition of a closed system is thus into a set of closed systems, each representing the original system from a different viewpoint.

The number of such decomposed systems is clearly application-dependent and sensitive to the identification of loosely coupled subsets of attributes. Some, such as physical site systems, logistic systems, logical systems, etc. are clearly loosely coupled since, within predetermined limits, design decisions are essentially independent. Those limits can be built into the requirements for each decomposed system. The application of our developmental process may now be made independently (and tested independently as well).

There may be some originating requirements that can not be analyzed for attribute coupling that prevent such decompositions. Since the originating requirements are not usually unique expressions, perhaps one can find a better set of requirements which can be decomposed. In any case, some non-decomposable requirements may still remain. These requirements thus can only be tested on the resulting integrated system. If such a requirement is tightly coupled to attributes scattered across the decomposed system, then the decomposition itself is probably ill-advised since system integration may produce expensive test failures. Perhaps one can

(a) INFORMAL DECOMPOSITION/INTEGRATION

(b) FORMAL DECOMPOSITION/INTEGRATION

FIG. 3: System decomposition/integration. Solid lines represent formally defined entities. Dashed lines represent informally defined entities.

find another equivalent set of originating requirements that can be more completely decomposed.

We can minimize the risk caused by non-decomposable requirements by carrying the separate developmental processes only far enough so that integration at that level (perhaps a different level for each system, or even within each system) makes the non-decomposable requirement testable. We must then deal with multi-level abstract system integration and testing in our requirements process.

Another serious problem arises from the informal nature of these decompositions. The subsequent integration must also be informal. Since there is no formal characterization of how they were taken apart, we are unlikely to formalize how they are put back together. In any event only <u>ad hoc</u> techniques can be used. Note that if a formal decomposition can be made as in Figure 3b, this problem can be avoided by doing it that way.

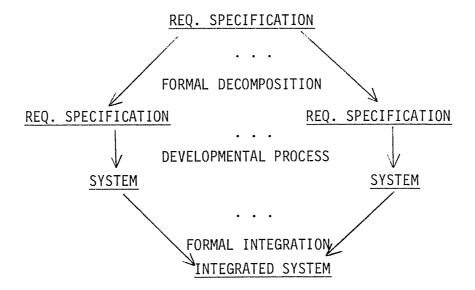

#### 2.3 Formal Decomposition/Integration

A formal requirements specification can be decomposed in the same way as informal decomposition, except that the decomposition can be formally characterized and the possibility of subsequent formal integration can be tested a priori. The essential difference between formal and informal decomposition lies in the formal specification of the system being decomposed in the former case. We can thus precisely characterize the decomposition (even if we have no effective procedure for carrying it out) and establish sufficient conditions to ensure the correctness of the decomposition. Both the decomposition and the integration may be substantially aided by design

automation tools. Indeed, we can accept sufficient design laws on the form of the decomposition to ensure that integration can be done and tested automatically. We should still support integration at many levels of design detail to minimize risk from non-decomposable requirements.

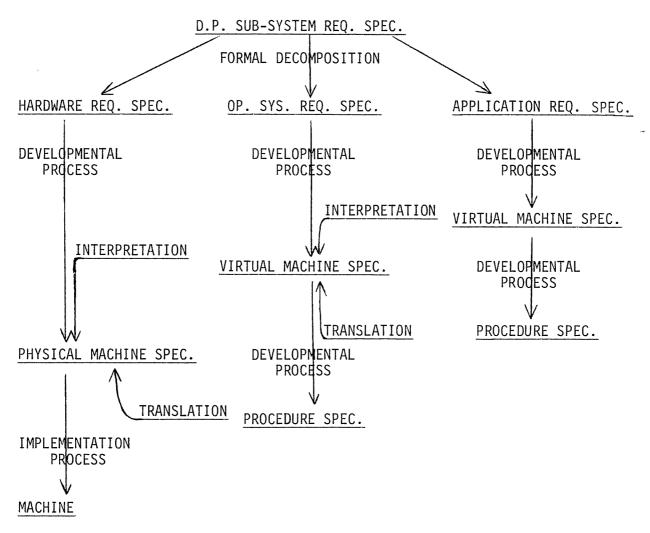

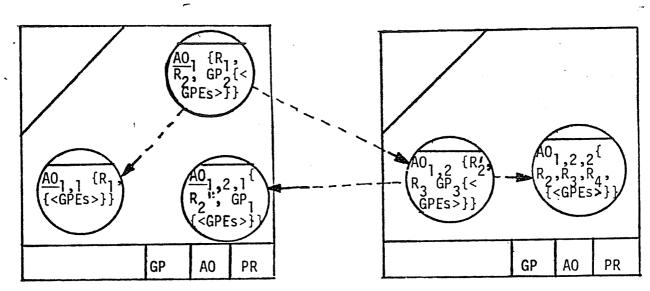

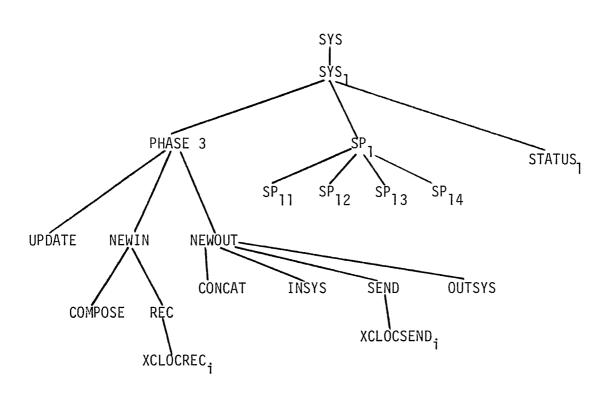

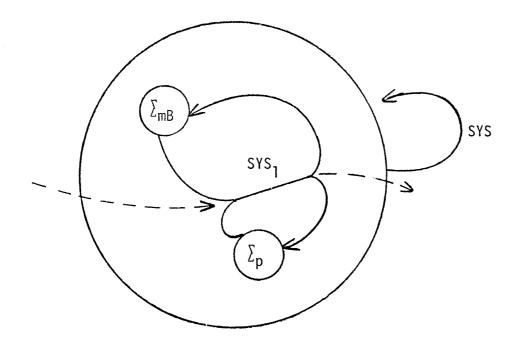

An example of a possible data processing system decomposition and integration is given in Figure 4.

FIG. 4: An example of formal system decomposition/integration. The effective property of each formal specification ensures that the specified system is in a form interpretable by a formally universal interpreter (the simulating system). Translation (compilation) steps may improve efficiency of the testing of resulting implementation. The example developmental process does not exhaust all possibilities but is intended as an illustration.

In this case we can develop translators and translator writing systems to aid the integration of the decomposed systems.

This type of decomposition may be very powerful in isolating the effects of changes to one of the decomposed systems. Similarly, because of the loose coupling between such systems (or they would not be decomposed), some of the components may be directly usable in other applications, or easily adaptable to changes in an application.

Because of the critical nature of some performance requirements and the extreme difficulty of meeting them, there must be some "escape mechanism" that allows application system designers to require direct hardware implementation of some application algorithms. Thus some need for interactions between developmental processes may exist and should be supported. Such interactions can be well-defined steps of the developmental process.

# 2.4 System Partitioning

So far we have not looked at the required internal structure of a single, formal system requirement specification. In section 2.1.4 we discuss and justify the use of closed system specifications on the basis of testability and closure. Thus we implicitly assume there exist at least two systems to be specified, the environment and the environmental-manipulating system. The requirements process may, of course, require elaboration of both systems to reach an acceptable level of testability. Our formal specifications of a system must be able to require an interacting system complex with formal specification, not only of the systems in the complex, but also of their interactions. The partitioning of logical functions among the systems in the

complex does not necessarily imply the same partitioning of physical systems in the implementation. This point is illustrated in Figure 5.

The logical partitioning of Figure 5 involves only a part of the formal requirements. For our purposes, we can factor system requirements into the following:

- . Performance: how well must the system work?

- . Resources: what kind and how many can the system use?

- . Logical: what functions must the system support?

We are disregarding here the valid need for similar requirements on the requirements process itself, and we are not formalizing the testing of those requirements. This is a potentially important exception, and the need for better management tools for the developmental process is recognizable. We feel that formalizing the developmental process and the testing of developing systems are essential first steps in solving management problems.

The testability of a partitioned logical requirement specification is still dependent on the existence of the other logical specifications since only then do we have a testable closure. We can use for this purpose the currently most suitable of the other specifications in the partitioned set. Figure 5 thus becomes an elaboration of Figure 2. If the performance and resource requirements are loosely coupled, we could use formal decomposition instead, and make the testing even more factored and localized as in Figure 3, but that would not be a partitioning step.

We must thus assume that performance and resource requirements are not practically decomposable into relatively independent requirements for each system in the partitioned set. Any attempted decomposition would run into "the requirements allocation problem" which in these terms is insoluble. Thus we won't try to solve it, but we don't need to in order to carry out the requirements process of Figure 5.

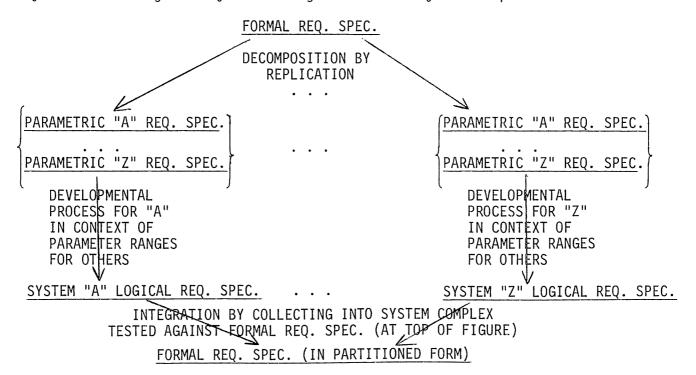

We may be able to do even better if we can develop parametric logical specifications for each member of the partitioned set. We can then use the decomposition and integration steps of Figure 6. All testing can now be done independently within parametric ranges.

Each of the decomposed systems is a system complex representing the entire system and is thus a testable entity. Interactions between the decomposed requirements processes are now required only when parameter ranges must be exceeded to meet specifications, and when the partitioned systems are integrated by collecting them into a system complex.

FIG. 6: Parametric partitioning

# 2.5 Primitive Elaboration

We will assume that the formal requirements specification will be defined using a functional formalism designed to provide a sufficiently general model for all systems of interest. There previously was no such model available, primarily because of the need to functionally model asynchronous interactions which was not met in available models. We have developed such a model and it is described in section 3. In this section we will ignore the requirements for formal interactions, although after section 3 they can be dealt with without change in the discussion presented here.

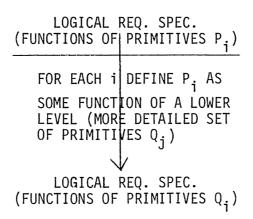

The initial formal requirements specifications will use rather high-level primitive functions in precisely specifying the system. Primitive functions are not formally defined but rather are informally characterized (e.g., in English descriptions). Each such initial primitive may eventually be elaborated by the developmental process into many processes or procedures spread over an entire network of implemented (physical) systems. The initial definition is thus as some mathematical expression of the high-level primitives.

The level of formally defined detail (primitives are only informally defined) may not be sufficient to formally encode all of the originating requirements or to formally test against the originating requirements. The required elaboration of detail is obtained, as shown by Figure 7a, by formally defining the high-level primitives in terms of lower level ones, thus formally encoding in the defining expressions at least part of what was previously encoded informally in English. This results in an elaboration step as shown in Figure 7b.

The degree of such elaboration increases as we move along the developmental process. The requirements process ends when all requirements have been formally encoded and tested for suitability. Figure 7c describes some possible intermediate states in the developmental process. The virtual systems are used (as discussed in section 5) to factor the developmental process and are defined by some interpretation function (processor) operating on a pair of program and data (system state) to define a computation of the virtual (not physical, but logical) machine. Eventually the virtual machine programs and data may be compiled to implementation (physical) machine initializations. This design process is further described in section 6.

$$P_{1}(x,y,z) = P_{1}(P_{2}(P_{3}(x), P_{4}(y)), P_{5}(x), y)$$

$$P_{1}(x,y,z) = Q_{1}(Q_{2}(x), Q_{3}(y), z) \qquad P_{5}(x) = Q_{3}(Q_{2}(x), x)$$

(a) Function Definition Tree

(b) Primitive Elaboration Step

# (c) Levels of Primitive Elaboration

## FIG. 7: Elaboration of a Functional Specification

# 2.6 Requirements Process Summary

The informal originating requirements must be encoded formally in some functional specification whose behavior approximates that of the desired system. The behavior must be testable and, if unsatisfactory, either the originating requirements or the formal functional specification must be changed to improve the degree of approximation. The level of detail formally encoded may need to be elaborated prior to testing. The requirements process ends when the current originating requirements are formally encoded and the specified system has satisfactory behavior. This may have required partial completion of the remainder of the developmental process.

We have identified several types of requirements process steps (e.g., approximation, decomposition, integration, partitioning and elaboration) and discussed the issues involved in their formalization.

We have studied the issues of formal testability and have described an approach to their resolution by the formal, functional, effective specification of the requirements for closed systems.

We have identified a number of important properties a formal system specification must have in general, and laid a foundation for the subsequent work in section 3. Other required properties will be developed, after the formalism is established, as design laws which ensure that the tools and tests discussed in this section can actually be provided. Further design laws will be derived from studies described by the remaining sections. This is the first pass through this material, and feedback of results obtained in later sections will be incorporated in the final report due in January 1977.

#### 3. FUNCTIONAL PROCESS SPECIFICATIONS

#### 3.1 Introduction

The requirements for a system require needed behaviors or restrict behavior to certain limits. It is the behavior of the system being designed which our formal specifications must relate to the requirements. We must be able to verify that a specification corresponds to required behavior. For this verification we must be able to observe the specification's behavior, which entails the ability to observe the well-defined states and interactions of the specified systems. We may think of these well-defined actions as state transitions of a digital process, and the well-defined interactions as interface transitions. The state transitions can be defined as algorithms (possibly nondetermininstic) for the successor state.

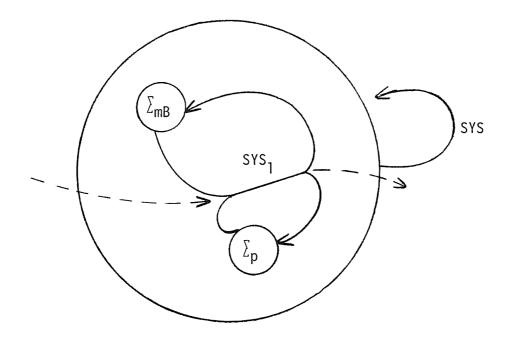

Many required systems have behavior which is primarily factored into the behaviors of several components, particularly for geographically distributed processing. However, these components are required to communicate and coordinate behavior via some form of interactions—the states of one component have an effect on the states of the other component. It is also important that these interactions may occur asynchronously, as the indispensibility of interrupts has shown. We must have a formal model for such complex processes.

# 3.1.1 Basis for Functional Specification

From the goals for modelling system behavior and for observing and verifying specified behavior, we have the concepts of state, algorithmic state transition, and interacting component processes of a system. Our

formalism begins with these concepts and develops according the goals and properties required for a specification formalism.

There is a generally accepted concensus that a process can be defined by a set  $\Sigma$  of process states and a (possibly nondeterministic) successor function f. The application of f to a process state  $\sigma$  to produce a process state  $\sigma'$  is known as a process step. When we wish to specify a a more complex process in which internally asynchronous or independent transitions occur, there is no longer a consensus, and more work is needed. Ramamoorthy and So [RAM 76] have said that a functional process specification should be "(1) comprehensible, (2) unambiguous, (3) verifiable, and (4) machine processable". These goals are certainly justified by the need for a requirement methodology: (1), (2), and (3) are needed for correctly and consistently formalizing functional requirements, (2) and (3) are needed for correctly developing and implementing specifications, and (4) is needed for accuracy, for the volume of the work, and for simulation testing. These goals may be met by a formalism based on a mathematical notation of functions and sets which has been subject to constraints which quarantee (3) and (4) and which allow sufficient expressive power for (1).

A further goal is to ensure properties which we desire the specified system transitions to have, such as: algorithmic implication (computations terminate without blocking), the ability to test real time systems by nonreal time simulation, and the ability to model any characteristics of a real system by our specifications (completeness from 2.1.2). In general, a specification should be such that each of a set of relevant properties is

<sup>[</sup>RAM 76] Ramamoorthy, C.V. and So, H.H., "Survey of Principles and Techniques of Software Requirements and Specifications", Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, 1976.

either guaranteed by the form of the specification, or is efficiently decidable on it. Furthermore we should be able to limit the information in a specification to that necessary to ensure these properties or their efficient decidability. We would also like our specification formalism to allow expansion of this goal as useful new properties are discovered and included in the relevant set (for example properties relating to the evolutionary development of existing systems).

Specifications based on mathematical function notation allow concentrating on relevant areas of a system and hiding the rest within primitive functions; this is the high level property mentioned in section 2.1.2. Such specifications also permit guaranteeing properties or their easy decidability by axiomatic constraints on function combinations, using much of what is already known about function behavior. Simple primitives for interactions may be inserted into the formalism of mathematical functions quite naturally, and these interaction primitives may also be handled by axiomatic constraints. Such a formalism also ensures the consistency and unambiguity of a specification if only minimal care is taken.

# 3.1.2 Properties of a Specification

In justifying the mathematical form of a functional process specification we have made reference to desirable properties for a specification as well as to more general goals in the development of functional specifications.

The properties include:

- (1) observable and verifiable behavior of a specification.

- (2) generality for asynchronously interacting processes.

- (3) algorithmic implication (all state transitions will complete).

- (4) testability--particularly of real time distributed processes by simulation.

- (5) completeness of specification with respect to characteristics of required system.

- (6) ability to superimpose developmental and evolutionary processes on the specification formalism.

- (7) ability to concentrate only on areas of the system relevant to desired analysis, leaving low-level details within primitives.

- (8) consistency and unambiguity of specification.

In addition to these properties there are two mentioned in section 2.1.2:

- (9) effective decidability of the behavior of a system specification.

- (10) traceability of the impact of changes in a system specification. The decidability of behavior must be in terms of analyzing asynchronous interactions, which will be discussed later. Tracing the impact of changes depends upon the change being local to an area of the specification, which in turn depends upon a correct design decision in factoring the specification.

## 3.2 System Specifications

We start our discussion of formal specifications by introducing some basic definitions. (A more rigorous and complete treatment is given in Appendix A.)

<u>Definition</u>. A <u>value space</u> V is a set of values v which are not here further defined.

<u>Definition</u>. A state space  $\Sigma$  is a product  $\Sigma_1 \times \Sigma_2 \times \cdots \times \Sigma_m$  of state component spaces, i.e.  $\sigma \in \Sigma$  if and only if  $\sigma = (\sigma_1, \sigma_2, \cdots, \sigma_m)$  where  $\sigma_i \in \Sigma_i$ ,  $i = 1, 2, \cdots, m$ .

<u>Definition</u>. A <u>process</u> is a pair  $(\Sigma,f)$  where  $\Sigma$  is a state space and f is a possibly nondeterministic state successor function.

The state successor function f may possibly be decomposed into  $\underline{\text{component}}$   $\underline{\text{successor}}$   $\underline{\text{functions}}$   $f_i$  where the  $f_i$  are set functions. A component successor function  $f_i$  may possibly be further decomposed into  $\underline{\text{value}}$   $\underline{\text{successor}}$   $\underline{\text{functions}}$   $f_{ij}$  where the  $f_{ij}$  are not set valued functions but are value space valued functions. Note that either the  $f_i$  or the  $f_{ij}$  may be nondeterministic. The definitions of the function decompositions are developed in the next section.

A <u>computation</u> of a process  $(\Sigma,f)$  is a sequence  $\sigma_0,\sigma_1,\sigma_2,\cdots,\sigma_i,\cdots$  such that  $\sigma_i \in \Sigma$   $(i \geq 0)$  and  $\sigma_{i+1} \in f(\sigma_i)$   $(i \geq 0)$ , and  $\sigma_0$  is an <u>initial state</u> of the computations. Thus a process and an initial state define a computation.

#### 3.2.1 Process Graphs

Suppose that we have a successor relation f which we wish to decompose into simpler relations. Since only finite specifications of f are useful, writing a different relation for each single state will fail if there are an infinite number of states. The solution is to gather states into a finite number of equivalence classes and write a separate successor relation for each class.

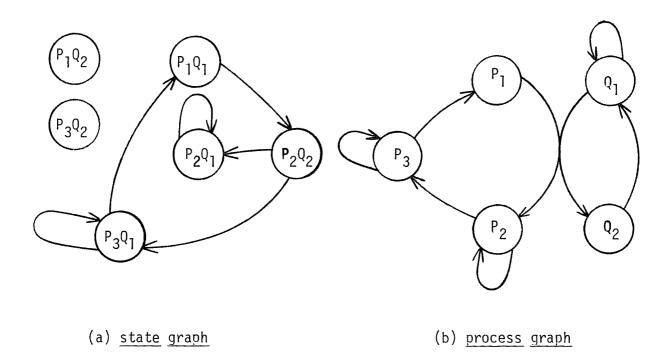

If the equivalence classes are represented as nodes of a graph and the successor relations as arcs, the result is known as a state graph. The

corresponding state successor relation can then be defined as a finite state machine. State graphs may be useful for forming specifications, even for small systems, only as long as the designer has a single locus of control transitions. To see how state graphs fail when a process has the potential for internal parallelism, consider a process which is the composition of two loosely coupled processes P and Q. As P cycles through m state equivalence classes and Q cycles through n state equivalence classes, the composite process will be cycling through a state graph of mn nodes. For each of the m possible values of component P, there will be a different variant of the component successor relation for Q. State graphs also fail because they quickly become unworkably complex as the number of state equivalence classes increases.

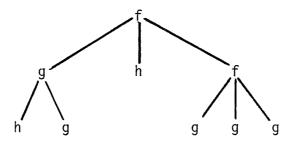

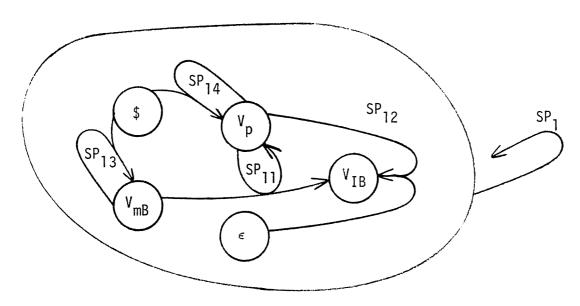

A state of the composite process could be represented as having two state components, one giving the state of P and the other giving the state of Q. This indicates a better way to graph the composite process: the nodes of the graph will be a finite set of equivalence classes of state components, and the arcs will represent successor relations on state components. This kind of graph will be called a <u>process graph</u>. The state and process graphs for the composite process are shown in Figure 8.

The process graph is a better characterization of what is going on in the composite process, and is much simpler, especially when m and n are large. Given the definition of the state successor function the two graphs are functionally equivalent. The state graph explicitly encodes information that the process graph only implicitly encodes, such as the fact that  $P_1Q_2$  and  $P_3Q_2$  are unreachable, for instance. However, this information is irrelevant to the problem of specifying f. If that information is relevant

Figure 8: State successor function graphs.  $P_i$  and  $Q_i$  are components of sub-processes P and Q respectively.

to some analysis, it may be either be obtained by studying computations via the process graph or it could not have been obtained in the first place. A formal definition of process graphs is given in Appendix A.

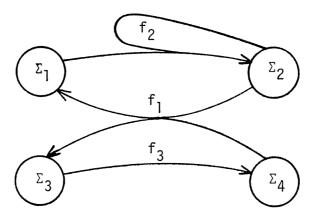

## 3.2.2 State Successor Function Decomposition

The decomposition of a state successor function f into component successor functions can be represented by a process graph. Each node of the graph represents a state component space and each arc represents a component successor function  $f_i$ . The arc is drawn from the component spaces in the domain of  $f_i$  to the component spaces in the range of  $f_i$ . For example, suppose we have the state successor function  $f: \Sigma \to \Sigma$  where  $\Sigma = \Sigma_1 \times \Sigma_2 \times \Sigma_3 \times \Sigma_4$ . Suppose further that f can be decomposed into component successor functions  $f_1$ ,  $f_2$ ,  $f_3$  given by:

f<sub>1</sub>:

$$\Sigma_2 \times \Sigma_4 \rightarrow \Sigma_1 \times \Sigma_3$$

f<sub>2</sub>:  $\Sigma_1 \times \Sigma_2 \rightarrow \Sigma_2$

f<sub>3</sub>:  $\Sigma_3 \rightarrow \Sigma_4$ .

Then f can be represented by the process graph in figure 9.

Figure 9: A process graph with component selector functions.

## 3.2.3 Functional Elaboration

The f<sub>i</sub> and f<sub>ij</sub> in a functional specification may be left as primitives or may be decomposed into lower level primitives. The functional specification must be based on primitive functions of the designer's choosing. These primitive functions may be arbitrarily simple or arbitrarily complex. The more complex the primitives are, the simpler the resulting specification structure will be, and the less help the designer will receive in analyzing it. The primitive functions must of course obey the design laws, in order to ensure the overall specification properties which the designer desires.

The ability to select these primitives freely lets the designer avoid the formalism if he wishes. He may elect to define f as a primitive, in which case there are no restrictions on it. Neither, of course, will be receive much help in analyzing it.

We must now decide what basic operations on functions we must have in creating the functional specification structure. From recursive function theory we know that all algorithms can be defined in terms of a few primitive functions and the operations of composition, primitive recursion, and selection. The operation of function composition must be included; with it we decompose f into the  $f_i$ , the  $f_i$  into  $f_{ij}$  and high level primitives into lower level primitives. We include the operation of primitive recursion because it gives us the capability for iteration. By the definition of primitive recursion this iteration is bounded because the recursion is guaranteed to stop after a finite number of function evaluations. Finally we use the operation of function selection, which is defined as follows:  $s(p_1;g_1,p_2;g_2,\cdots,g_k)$  evaluates to the value of the first  $g_i$  such that  $p_i$  evaluates to true (the  $p_i$  are predicates which evaluate to true or false). This selector function s gives us a model of control.

It is worth noting that the basic form of a component function is that of a tree of nested functions with primitives as leaves. This form is established by the composition schema. Recursion and selection do not alter the tree form of the structure which is finally evaluated, but only delay its binding until evaluation time. Recursion finally expands to a fixed depth nesting, and selection simply reduces to the selected subtree.

At this point we can model an arbitrary algorithmic state successor function for a single system. We now need to introduce a functional model

for interactions to deal with nearly decomposable component functions (decomposed with residual interactions) and with multiple interacting systems.

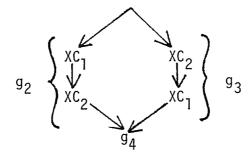

## 3.3 Interaction Specifications

We now define a class of primitive functions which will allow the designer to specify interactions. These exchange functions have the unique property that under certain conditions they will exchange values of arguments with a matching exchange function elsewhere in the specification. The exchange of arguments between a pair of matching exchange functions is accomplished by having each of them evaluate to the argument of the other. Exchange functions are labelled with subscripts and only exchange functions with the same label can match. The set of exchange functions with a given subscript is referred to as a class. Thus exchanges may only occur between members of the same class.

The three exchange functions XC, XA, XS are defined as follows:  $XC_{i}(\alpha) = \beta \qquad \text{if there is an outstanding} \quad XC_{i}(\beta) \text{ or } XA_{i}(\beta) \text{ which has}$  been waiting for a matching exchange function

or

if this  $XC_i(\alpha)$  has been waiting for a matching exchange function and an  $XC_i(\beta)$ ,  $XA_i(\beta)$ , or  $XS_i(\beta)$  is evaluated.

$XA_i(\alpha) = \beta$  if there is an outstanding  $XC_i(\beta)$  which has been waiting for a matching exchange function to be evaluated

or

if this  $XA_i(\alpha)$  has been waiting for a matching exchange function and an  $XC_i(\beta)$  or  $XS_i(\beta)$  is evaluated.

- $XS_i(\alpha) = \beta$  if there is an outstanding  $XC_i(\beta)$  or  $XA_i(\beta)$  which has been waiting for a matching exchange function to be evaluated.

- $= \alpha$  otherwise.

#### 3.3.2 Evaluation

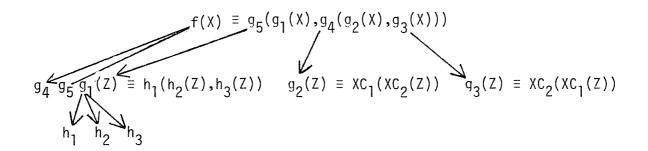

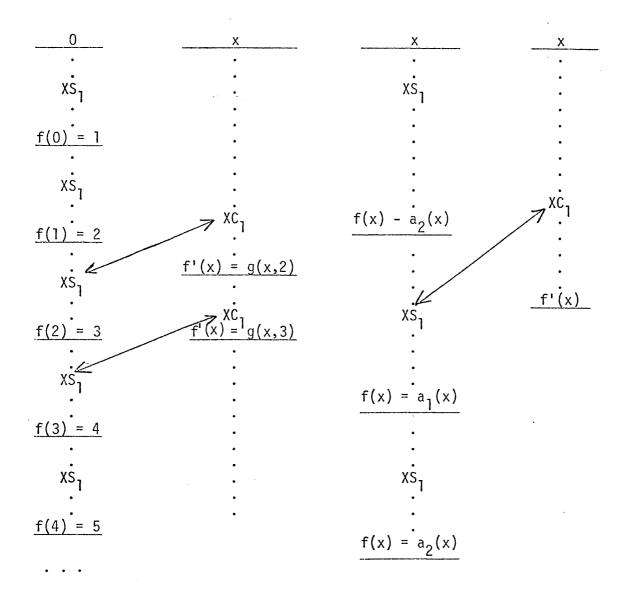

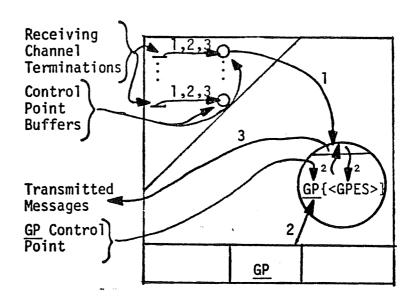

Any state successor function can be defined by a definition tree as shown in figure 10a and automatically transformed into a corresponding precedence graph as shown in Figure 10b. The precedence graph simply displays the constraints on possible evaluation sequences. The use of exchange functions imposes additional (and potentially incompatible) synchronization constraints and allows values to be exchanged.

The exchange functions can be analyzed as normal (possibly nondeterministic) functions in their local context while still providing a high level (non-procedural) model for asynchronous conventional process specification to internally and externally asynchronous processes.

An internally asynchronous interaction could be defined as matching exchanges between component successor functions. An externally asynchronous interaction could be defined as matching exchanges between state successor functions (each defining an independent system). Thus all interface interactions are modelled directly and homogeneously by our functional specifications.

Using an immediate exchange, XS, we can also model what we will call unsynchronized systems as containing only XS type inter-system interactions. Such systems never wait on any interactions and are essential for many real

time systems and for modelling the environmental system or real, physical world. An XS function cannot be used an an intra-system interaction since there cannot be sufficient constraints in a precedence graph to ever force its instantaneous matching with another exchange. Such use is therefore not allowed.

Unfortunately, this enormous generality of functional interaction specification comes at the price of some new design laws governing the use of exchanges. Arbitrary usage can lead to inter- or intra-system deadlocks (as must be true for any general interaction model). An example of an intra-system deadlock is given in figure 10c when no other exchanges of those classes are present. However it is possible to place restrictions on the form of the specification such that no process will be blocked in this way. Each restriction will correspond to a design law which must be followed in order to guarantee completion. Such restrictions are given in Appendix B.

## 3.3.3 Examples

A few trivial examples may help explain the use of exchanges.

We could define a pair of interacting systems by state successor functions f and f' as given in Figure lla.

In this example the evaluation of f' is delayed until the exchange  $XC_{\uparrow}$  has been completed by a subsequent evaluation of  $XS_{\uparrow}$  in f. Thus the evaluation of f is not so constrained, since  $XS_{\uparrow}$  will exchange with itself in order to continue without delay. f' could thus be interpreted as a system synchronized to the system f, that uses values from f in its own computations. The system f could be interpreted as a simple real-time clock that goes on with its

(a) A definition tree for  $f(X) \equiv g_5(g_1(X), g_4(G_2(X), g_3(X)))$  where  $g_1(Z) \equiv h_1(h_2(Z), h_3(Z))$ .  $h_1, h_2, h_3, g_2, g_3, g_4$  and  $g_5$  are all primitives

(b) The precedence graph for f(X) in terms of  $g_i$ .

(c) A blocked precedence graph for  $g_4(XC_1(XC_2(A)), XC_2(XC_1(B)))$  control cannot pass the first  $XC_1$ ,  $XC_2$  functions.

Figure 10: Use of exchanges in a function.

$$f: \epsilon \rightarrow \epsilon$$

$f(x) \equiv First (suc(x), xs_1(x))$

$f': \epsilon \rightarrow \epsilon$   $f'(x) \equiv g(x, xc_1(0))$

Where first  $(x,y) = x$  and  $suc(x) = x+1$

FIG 11: Simple Exchange Examples

# (b) Interrupt system

$$f: \epsilon \rightarrow \epsilon \quad f(x) \equiv (XS_1(F): a_1(x), T: a_2(a))$$

$f': \epsilon' \rightarrow \epsilon' f'(x) \equiv g(x, xc_1(T))$

Where  $T \equiv True$  and  $F \equiv False$

cycling (ticking) without delays or synchronizations with another system. A sketch of the computations of f and f' is given in Figure 11a.

As a second example, f and f' can be defined as in Figure 11b. In this example f' is synchronized as before. The system f can now be considered to cycle through evaluations of  $a_2(x)$  unless an  $XC_1$  is outstanding. In that case, the value of  $XS_1$  will be T and the function  $a_1(x)$  will be evaulated instead. The system f could thus be described as having been interrupted by system f', to perform function  $a_1$ .

# 3.4 System Complex Specifications

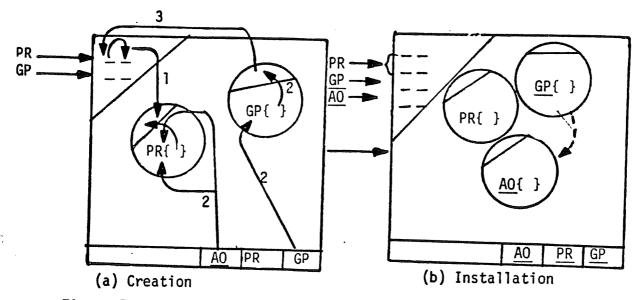

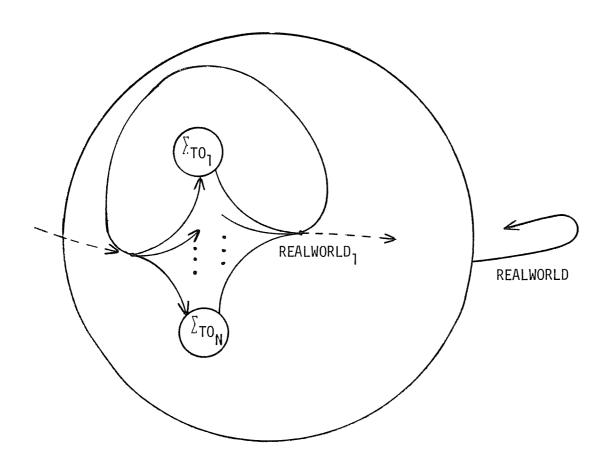

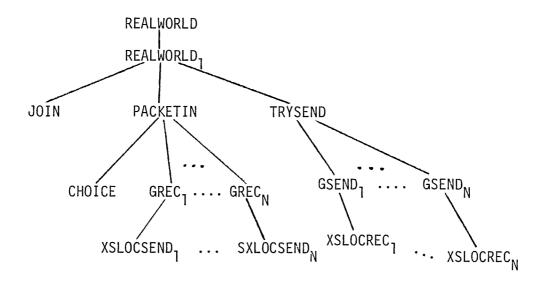

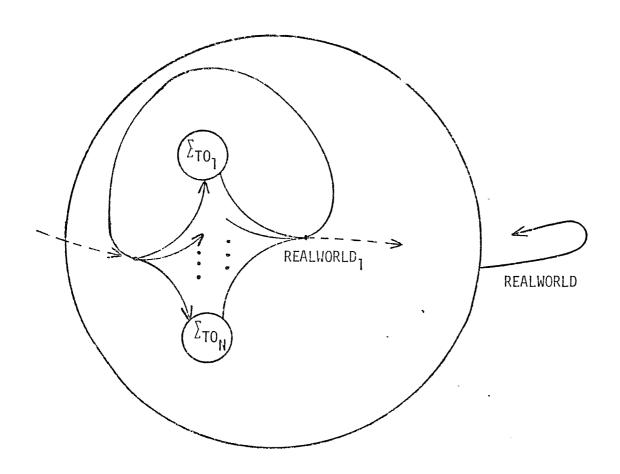

## 3.4.1 System Specification Domain