Non-Volatile Memory

Overview

New storage technologies such as Intel's 3D XPoint memory, Phase-Change Memory (PCM or PCRam), Memristors, and flash promise to change how programs and operating systems interact with storage. Our research focuses on new uses for these technologies outside traditional file storage.Support

This work is supported by NSF grants CSR: Small: Advancing Operating System Interfaces to Solid-State Storage (CNS-1218485) and CSR-DMSS, SM: Operating System Abstractions for Modern Hardware (CNS-0834473) and gifts from Google.Non-volatile Memory

Emerging non-volatile memory (NVM) techinologies provide the interface of memory but the persistence of disks. NVM promises low-latency storage, which is becoming increasingly important in data-centric applications. However, existing OS interfaces fail to expose the full capabilities of NVM as they are designed for a strict bifurcation of devices into memory and storage. We define Persistent Memory (PM) as NVM accessed with byte addressability at low latency via normal memory instructions.

WHISPER

Persistent-memory applications ensure the consistency of persistent data by inserting ordering points between writes to PM allowing the construction of higher-level transaction mechanisms. An epoch is a set of writes to PM between ordering points. To put systems research in PM on a firmer footing, we developed and analyzed a PM benchmark suite called WHISPE Rthat comprises ten PM applications we gathered to cover all current interfaces to PM. A quantitative analysis reveals several insights: (a) only 4% of writes in PM-aware applications are to PM and the rest are to volatile memory, (b) software transactions are often implemented with 5 to 50 ordering points (c) 75% of epochs update exactly one 64B cache line, (d) 80% of epochs from the same thread depend on previous epochs from the same thread, while few epochs depend on epochs from other threads. This is joint work with HP Labs.

WHISPER web site.

HOPS

Based on our analysis, we propose the Hands-off Persistence System (HOPS) to track updates to PM in hardware. Current hardware design requires applications to force data to PM as each epoch ends. HOPS provides high-level ISA primitives for applications to express durability and ordering constraints separately and enforces them automatically, while achieving 24.3% better performance over current approaches to persistence.

Aerie NVM file system

Non-volatile memory technologies present a radically different interface to storage than existing block devices. As a result, they provide a unique opportunity to re-examine storage architectures. We find that the existing kernel-based stack of components, well suited for disks, unnecessarily limits the design and implementation of file systems for this new technology. We designed Aerie, a flexible file-system architecture that exposes storage-class memory to user-mode programs so they can access files without kernel interaction. Aerie can implement a generic POSIX-like file system with performance similar to or better than a kernel implementation. The main benefit of Aerie, though, comes from enabling applications to optimize the file system interface. We demonstrated a specialized file system that reduces a hierarchical file system abstraction to a key/value store with fewer consistency guarantees but 20-109% higher performance than a kernel file system.

Mnemosyne: Lightweight Persistent Memory

Mnemosyne provides programmers with direct access to the durability of SCM through the persistent memory abstraction. With persistent memory, programmers can make common in-memory data structures, such as lists and trees, persistent without having to convert them to a serialized format. Data structures can be made persistent at the speed of the device rather than the speed of the operating system.

NVM Publications

- Sanketh Nalli, Swapnil Haria, Mark D. Hill, Michael M. Swift, Haris Volos, Kimberly Keeton. An Analysis of Persistent Memory Use with WHISPER. In 22nd ACM International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS 2017).

- Swapnil Haria, Sanketh Nalli, Mark D. Hill, Michael M. Swift, Haris Volos, Kimberly Keeton. Hands-Off Persistence System (HOPS) . In 8th Annual Non-Volatile Memories Workshop (NVMW 2017), February 2017.

- Sanketh Nalli, Swapnil Haria, Mark D. Hill, Michael M. Swift, Haris Volos, Kimberly Keeton. How Applications Use Persistent Memory. In 8th Annual Non-Volatile Memories Workshop (NVMW 2017), February 2017.

- Haris Volos, Sanketh Nalli, Venkatanathan Varadarajan, Sankaralingam Panneerselvam, Prashant Saxena and Michael M. Swift. Aerie: Flexible File-System Interfaces to Storage-Class Memory. In Proceedings of EuroSys, April 2014.

- Haris Volos, Sanketh Nalli, Venkatanathan Varadarajan, Sankaralingam Panneerselvam and Michael M. Swift. Storage-Class Memory Needs Flexible Storage APIs. In 4th ACM SIGOPS Asia-Pacific Workshop on Systems (APSys), July 2013.

- Haris Volos and Michael Swift. Storage Systems for Storage-Class Memory. In 2nd Annual Non-Volatile Memories Workshop, March 2011.

- Haris Volos, Andres Jaan Tack and Michael M. Swift. Mnemosyne: Lightweight Persistent Memory. in Proceedings of the 16th International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), March 2011.

Flash

The availability of high-speed solid-state storage has introduced a new tier into the storage hierarchy. Low-latency and high-IOPS solid-state drives (SSDs) cache data in front of high-capacity disks. However, most existing SSDs are designed to be a drop-in disk replacement, and hence are mismatched for use as a cache.

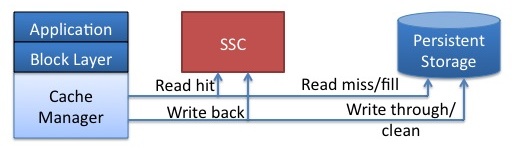

This work proposes FlashTier, a system architecture built upon solid-state cache (SSC), a flash device with an interface designed for caching. Management software at the operating system block layer directs caching. The FlashTier design addresses three limitations of using traditional SSDs for caching. First, FlashTier provides a unified logical address space to reduce the cost of cache block management within both the OS and the SSD. Second, FlashTier provides cache consistency guarantees allowing the cached data to be used following a crash. Finally, FlashTier leverages cache behavior to silently evict data blocks during garbage collection to improve performance of the SSC.

We have implemented an SSC simulator and a cache manager in Linux. In trace-based experiments, we show that FlashTier reduces address translation space by 60% and silent eviction improves performance by up to 167%. Furthermore, FlashTier can recover from the crash of a 100GB cache in only 2.4 seconds.