Optimizing Inter-Instruction Value Communication through Degree of Use Prediction

by

Jeffrey Adam Butts

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy (Computer Sciences)

at the University of Wisconsin–Madison 2004

© Copyright by Jeffrey Adam Butts 2004 All Rights Reserved

### Abstract

The design of high-performance value communication structures represents a significant challenge in the implementation of future microprocessors. The complexity of these structures namely, the register file, the bypass network, and the instruction window—dwarfs that of the actual instruction execution hardware and has become the predominant factor in determining the maximum operating frequency. Being wire-dominated, these structures also benefit less from technology scaling than the execution circuitry, increasing the importance of this problem.

Value communication structures are complex because they are overly general. Each of these structures is built to support the most general possible communication pattern for each value. However, examining value communication in actual programs reveals that most values are involved in simple communication, such as producer to single consumer. This dissertation proposes an alternate model for inter-instruction register value communication in which values may be handled differently by mechanisms optimized to their individual needs.

The foundation for this model is knowledge of communication on a per-value basis. The communication resource requirements of a value are summarized by its degree of use, which is simply the number of consumers of that value. Accurate degree of use information may be obtained speculatively via a prediction mechanism. This information may then be used to handle each value in the most efficient manner available.

This dissertation makes three major contributions to the development of this communication model. First, an in-depth study of register value communication in terms of the degree of use is presented in order to demonstrate the opportunity for alternative communication mechanisms. Second, methods for the accurate prediction of degree of use are presented and characterized. Finally, two proof-of-concept applications of the degree of use knowledge are developed. Useless instruction elimination exploits the occurrence of degree of use zero values, which have no consumers. Avoiding the execution of instructions generating such values reduces resource utilization, and, under resource contention, improves performance. Use-based register caching applies degree of use information to the management of a register cache. The resulting insight into each value's communication behavior allows the limited cache space to be used more effectively than previously proposed register caches.

### Acknowledgements

Above all others, I want to thank my wife, Susan Kalis. A Ph.D. candidate herself, she has been remarkably understanding of the afflictions associated with being a grad student: strange hours, long binges at the computer, lack of motivation, inability to maintain a social life, and general malaise. Especially during the past several months, she has put her own needs aside in order to support me during my final push to graduate. I am looking forward to returning the favor. It is said that it is easier to suffer together than to suffer alone—truly, I would endure any hardship so long as she was there with me. I would not be here, nor would I want to, without her, so this work is dedicated to her.

I owe a tremendous amount to my parents, Jeffrey and Stephanie. Rooted in the pacific northwest, they have seen little of me since I left to attend college in the midwest 11 years ago. However, knowing that I had a home always open to me has been a source of strength. It is their upbringing to which I credit being one of the most emotionally stable people I know. They have always encouraged me to excel and provided an environment in which I could do so. I can only aspire to someday be as good a parent as each of them was to me.

My advisor Guri Sohi has been instrumental in making me the researcher that I am today. He spent the better part of the last six years trying to break me of my engineering mentality, encouraging me to step back and look at the bigger picture instead of getting bogged down in gates and propagation delays. He has taught me a great deal not only about the field of computer architecture, but about the practice of performing good research. I am also grateful for his inhuman patience with my . . . flexible approach to time management.

In a very real sense, I have had many research advisors. An incredible strength of the computer science department at the University of Wisconsin is the engagement of the faculty in the development of each and every graduate student. I have benefitted from discussions with Ras Bodik, Charlie Fischer, Jim Goodman, Mark Hill, Susan Horwitz, and Mary Vernon. David Wood in particular has been a tremendous resource in matters both technical and otherwise. I am also happy to count him among my friends (and fellow left wings).

All of the members of my thesis committee deserve credit for the research contained herein (although I bear full responsibility for its shortcomings). In addition to Guri and David, Charlie

Fischer, Mikko Lipasti, and Jim Smith all contributed to my development as an architect. Aside from their direct input on my research both past and present, I have learned from their own research. Perhaps most of all, though, I have benefited from the opportunity to observe them on others' committees and at conferences, where I was exposed to their thought processes and analyses of different research ideas.

For reasons still opaque to me, Amir Roth, Craig Zilles, and Milo Martin befriended me back when I was a know-it-all first-year student, despite being several years my senior. They are three of the smartest people I have ever met, and it was an invaluable experience to watch them progress through and succeed in graduate school. I have tried hard to emulate them, which has probably been a significant factor in my own graduation.

Many other current and former students and staff in the computer science department at Wisconsin have also been friends and collaborators including Ross Dickson, Brian Fields, Allison Holloway, Carl Mauer, David Parter, Erik Paulson, and Ravi Rajwar. David Parter has my extra thanks for opening his home to me as my Madison base since I relocated to Chicago last year.

My graduate school experience would have been less productive and much less fun were it not for the great company of so many other graduate students. Of these, Brandon Schwartz and Paramjit Oberoi deserve special mention. Brandon was my roommate for most of graduate school, and, in addition to sitting and discussing microarchitecture in front of the 4-by-8 foot dry erase board in our apartment, we engaged in endless post-midnight discourses on computer science, physics, philosophy, psychology, sociology, political science, and hockey among other topics. Param and I had many equally wide-ranging discussions, especially after he became my officemate. Param also endured having me as a partner for not one class project, but every project in all four classes we took together. Both Brandon and Param helped me refine nearly every idea in this work and many more that are not.

A conservative estimate puts the total computer time spent obtaining the data in this document at over 100,000 hours (almost 11.4 *years*), although it was generated in only a few months of calendar time. The Condor system made this possible, and I am grateful to the members of the Condor team for providing and supporting this service. They often went the extra mile to scrounge additional machines to help me meet various deadlines. I am also extremely thankful for all of the people, those I know personally and otherwise, who maintain the amazing research support infrastructure in the computer science department. The staff of the computer systems lab performs the monumental—and often thankless—task of keeping the computers and the network up and running. It is a testament to their success that I find it difficult to express the extent of their role: everything just works, allowing people to concentrate fully on their research.

I still find it remarkable that I was able to get paid to learn for the past six years. For this I am deeply indebted to the Fannie and John Hertz Foundation and Intel Corporation. In addition to its generous financial support over five years, the Hertz Foundation has also been a valuable source of contacts and an advocate for my personal career. For the final year of my graduate career, it was a fellowship from Intel that allowed me to maintain focus on my research instead of the source of my next meal.

Finally, I would be remiss if I did not at least mention several others who have helped me reach this point. Kathy Pfaendler, George Delegans, Nels Doeleman, Richard Green, Ken Houle, Carl Simonsen, Youssef El-Mansy, Greg Taylor, and Jeff Smith have all had profound effects on my life and intellectual development.

| Abstract i                                                         |

|--------------------------------------------------------------------|

| Acknowledgements ii                                                |

| Table of Contents v                                                |

| List of Figures x                                                  |

| List of Tables xii                                                 |

| Chapter 1. Introduction                                            |

| 1.1. Inter-Instruction Value Communication                         |

| 1.1.1. Inter-instruction communication in sequential architectures |

| 1.1.2. Register value communication                                |

| 1.1.3. Meeting the demands of parallelism                          |

| 1.1.4. The problem                                                 |

| 1.2. Degree of Use                                                 |

| 1.2.1. An example                                                  |

| 1.2.2. Classifying values using degree of use                      |

| 1.2.3. The need for prediction                                     |

| 1.3. Contributions                                                 |

| 1.4. Methodology                                                   |

| 1.4.1. Benchmarks 11                                               |

| 1.4.2. Simulators 11                                               |

| 1.4.3. Model architecture and microarchitecture 12                 |

| 1.5. Dissertation Outline                                          |

| Chapter 2. Characterizing Value Degree of Use                      |

| 2.1. Degree of Use Characteristics                                 |

| 2.1.1. Mean, median, mode, and maximum 15                          |

| 2.1.2. Degree of use of input values                               |

| 2.2. Classifying Values                                            |

| 2.2.1. Classification by instruction type                          |

| 2.2.2. Classification by register type                             |

| 2.3. Temporal Characteristics                                      |

|                                                                      | vi |

|----------------------------------------------------------------------|----|

| 2.4. Working Set Behavior                                            |    |

| 2.4.1. Number of possible degrees of use                             |    |

| 2.4.2. Relative likelihood of possible degrees of use                |    |

| 2.4.3. Temporal locality in per-instruction degrees of use           |    |

| 2.5. Mathematical Models                                             |    |

| 2.5.1. Degree of use distribution                                    |    |

| 2.5.2. Independent derivation of the mean degree of use              |    |

| 2.6. Summary                                                         |    |

| Chapter 3. Degree of Use Prediction                                  |    |

| 3.1. Predictor Evaluation                                            |    |

| 3.2. Encoding Degree of Use Information                              |    |

| 3.2.1. Maximum predictable degree of use                             |    |

| 3.2.2. Biasing                                                       |    |

| 3.2.3. Default predictions                                           |    |

| 3.2.4. Grouping                                                      |    |

| 3.3. Static Degree of Use Prediction                                 |    |

| 3.3.1. Formulating degree of use determination as a dataflow problem |    |

| 3.3.2. Solving the degree of use dataflow problem                    |    |

| 3.3.3. Results                                                       | 53 |

| 3.3.4. Applying profile information                                  | 54 |

| 3.3.5. Communicating static predictions to the hardware              |    |

| 3.4. Dynamic Degree of Use Prediction                                |    |

| 3.4.1. Simple predictor: last observed degree of use                 | 60 |

| 3.4.2. Adding confidence                                             |    |

| 3.4.3. Using control-flow information                                | 65 |

| 3.4.4. Aliasing in degree of use predictors                          | 71 |

| 3.4.5. Comparative evaluation                                        | 74 |

| 3.4.6. Training                                                      |    |

| 3.4.7. Verifying degree of use predictions                           |    |

| 3.4.8. Predictor bandwidth                                           |    |

|                                                            | vii  |

|------------------------------------------------------------|------|

| 3.5. Hybrid Prediction Schemes                             | . 88 |

| 3.6. Summary                                               | . 88 |

| Chapter 4. Useless Instruction Elimination                 | . 90 |

| 4.1. Characterizing Useless Instructions                   | . 92 |

| 4.1.1. Origin                                              | . 92 |

| 4.1.2. Prevalence                                          | . 94 |

| 4.1.3. Role of the compiler                                | . 98 |

| 4.1.4. Useless instruction resources                       | 100  |

| 4.2. Useless Instruction Elimination                       | 103  |

| 4.2.1. Elimination candidates                              | 105  |

| 4.2.2. Normal operation of useless instruction elimination | 106  |

| 4.2.3. Misprediction detection and recovery                | 107  |

| 4.2.4. Retirement backup                                   | 109  |

| 4.2.5. Loads                                               | 109  |

| 4.2.6. Instructions with side effects                      | 110  |

| 4.2.7. Deadlock avoidance                                  | 112  |

| 4.3. Results                                               | 113  |

| 4.3.1. Parameter sensitivity analysis                      | 115  |

| 4.3.2. Resource utilization                                | 117  |

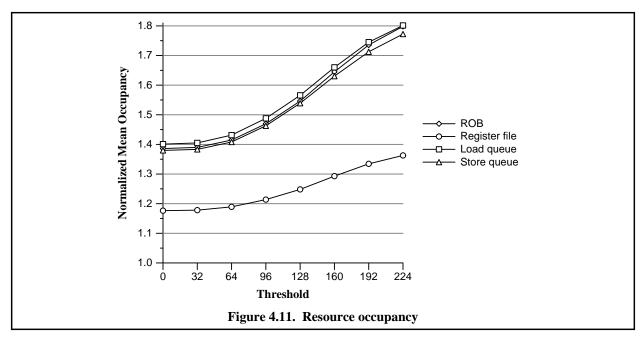

| 4.3.3. Resource occupancy                                  | 119  |

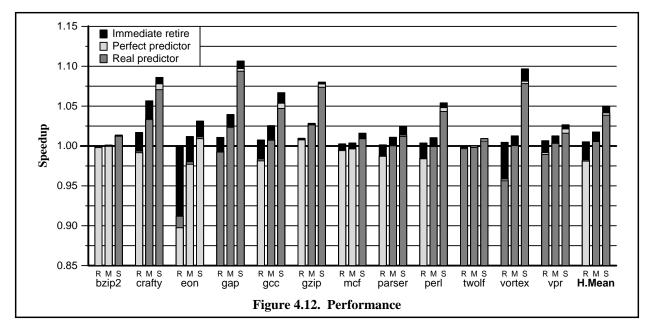

| 4.3.4. Performance                                         | 120  |

| 4.4. Related Work                                          | 122  |

| 4.5. Summary                                               | 123  |

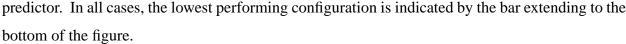

| Chapter 5. Use-Based Register Caching                      | 125  |

| 5.1. Introduction                                          | 125  |

| 5.2. Register Cache Operation                              | 129  |

| 5.3. Use-Based Register Cache Management                   | 133  |

| 5.3.1. Register cache insertion policy                     | 134  |

| 5.3.2. Register cache replacement policy                   | 136  |

| 5.3.3. Counting remaining uses                             | 137  |

|                                                                  | viii |

|------------------------------------------------------------------|------|

| 5.3.4. Incorrect use information                                 | 139  |

| 5.4. Evaluation                                                  | 140  |

| 5.4.1. Processor model                                           | 141  |

| 5.4.2. Register cache size                                       | 142  |

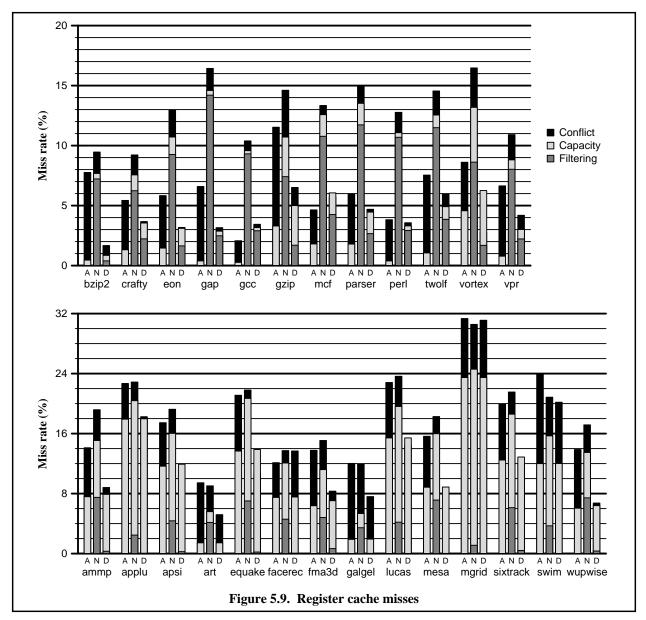

| 5.4.3. Misses                                                    | 143  |

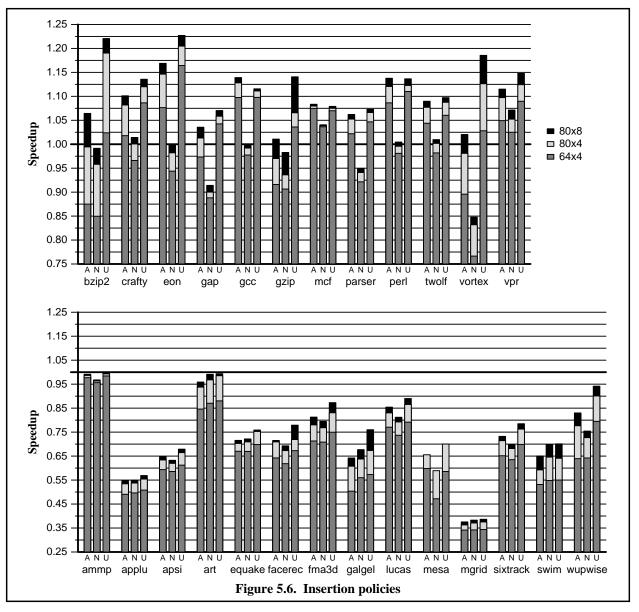

| 5.4.4. Comparing insertion policies                              | 146  |

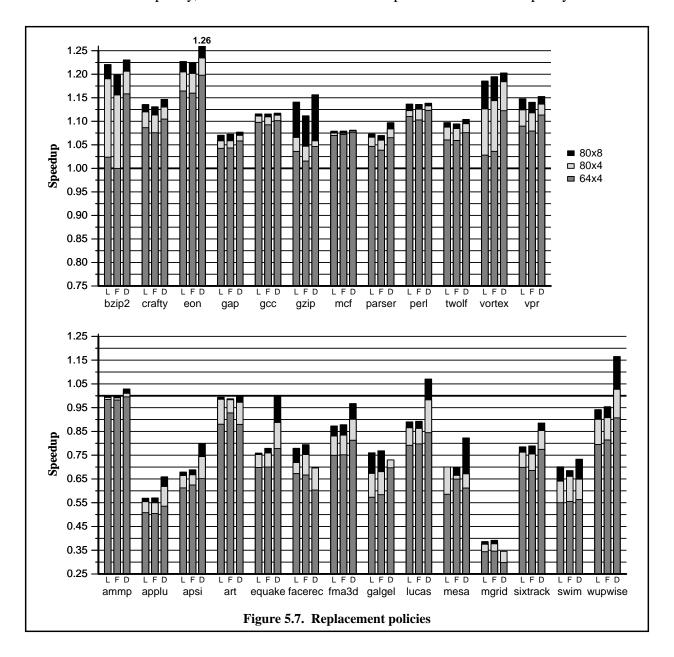

| 5.4.5. Comparing replacement policies                            | 150  |

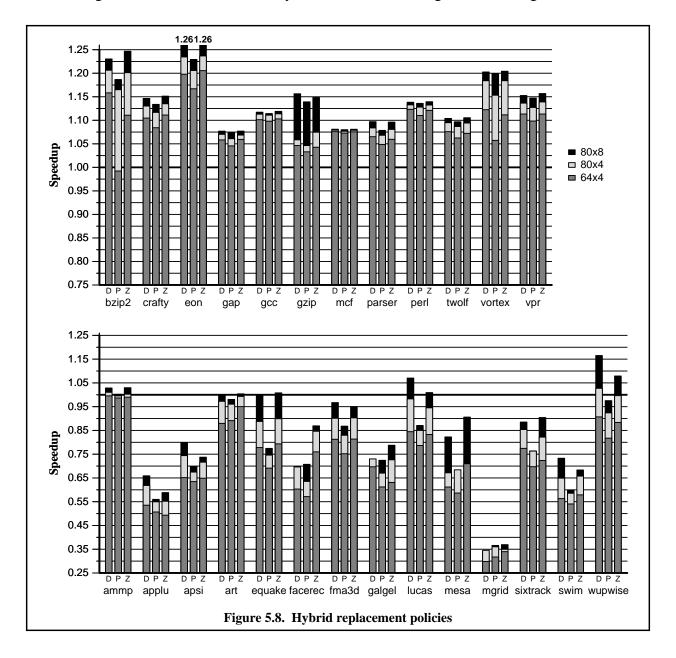

| 5.4.6. Miss breakdown                                            | 152  |

| 5.4.7. Sensitivity studies                                       | 154  |

| 5.5. Related Work                                                | 156  |

| 5.6. Summary                                                     | 158  |

| Chapter 6. Conclusions                                           | 160  |

| 6.1. Contributions and Key Results                               | 161  |

| 6.1.1. Degree of use characterization                            | 161  |

| 6.1.2. Degree of use prediction                                  | 162  |

| 6.1.3. Useless instruction elimination                           | 163  |

| 6.1.4. Use-based register caching                                | 163  |

| 6.2. Additional Applications of Degree of Use Knowledge          | 164  |

| 6.2.1. Early register reclamation                                | 164  |

| 6.2.2. Registerless communication                                | 165  |

| 6.2.3. Collapsing dependent operations                           | 165  |

| 6.2.4. Direct consumer scheduling                                | 166  |

| 6.2.5. Widely-used values                                        | 166  |

| 6.3. Costs and Benefits of Use-Based Communication Optimizations | 167  |

| References                                                       | 169  |

| Appendix. Methodology                                            | 179  |

| A.1. Benchmarks                                                  | 179  |

| A.1.1. Input data                                                | 179  |

| A.1.2. Multiple-input benchmarks                                 | 180  |

| A.1.3. perl test input                                           | 180  |

| ix                                             |

|------------------------------------------------|

| A.2. Benchmark Compilation                     |

| A.2.1. Compilers                               |

| A.2.2. Optimization levels                     |

| A.3. Binary Dataflow Analyzer                  |

| A.3.1. Precision considerations                |

| A.3.2. Operation of binary analyzer            |

| A.4. Simulation                                |

| A.4.1. Execution-driven simulation             |

| A.4.2. Functional versus timing simulation     |

| A.4.3. System call emulation                   |

| A.4.4. Static linking                          |

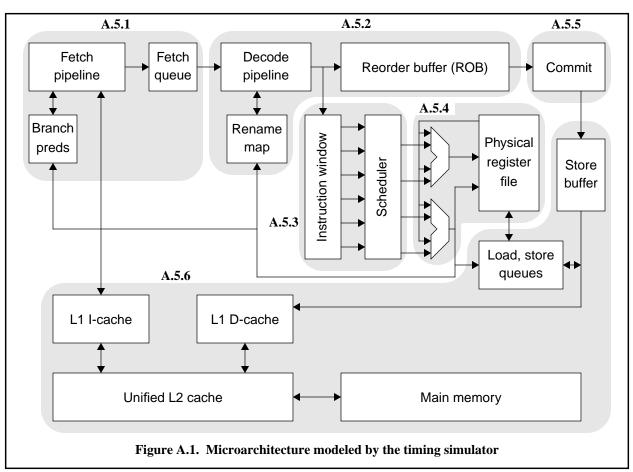

| A.5. Timing Simulator Microarchitectural Model |

| A.5.1. Fetch pipeline (front end)              |

| A.5.2. Decode pipeline                         |

| A.5.3. Instruction window and scheduler        |

| A.5.4. Register file and execution             |

| A.5.5. Commit                                  |

| A.5.6. Memory system 196                       |

# List of Figures

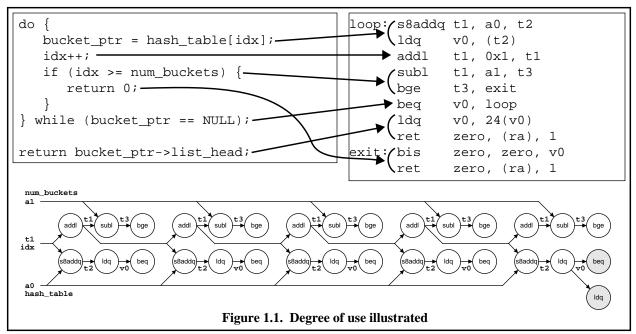

| Figure 1.1.  | Degree of use illustrated                                                         | 7  |

|--------------|-----------------------------------------------------------------------------------|----|

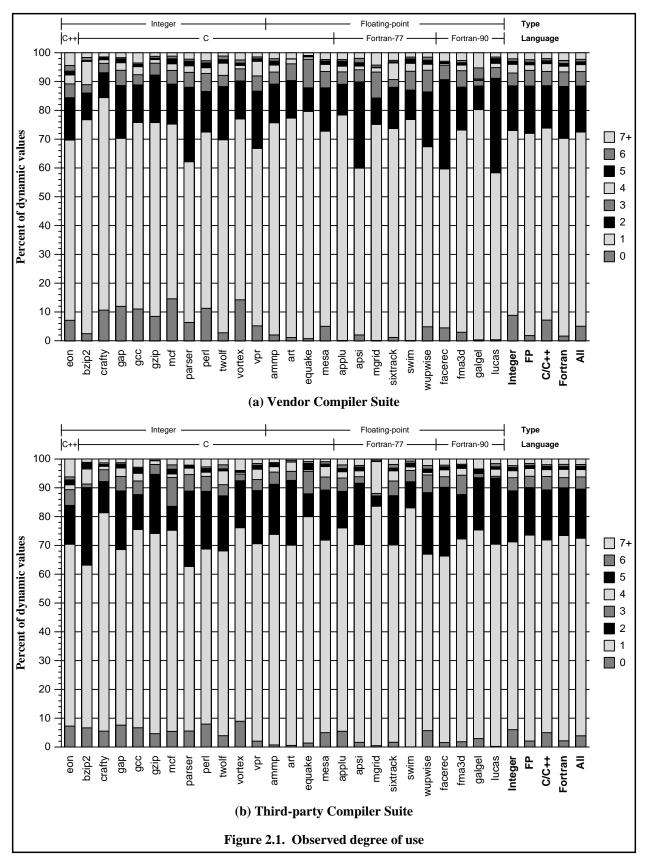

| Figure 2.1.  | Observed degree of use                                                            | 16 |

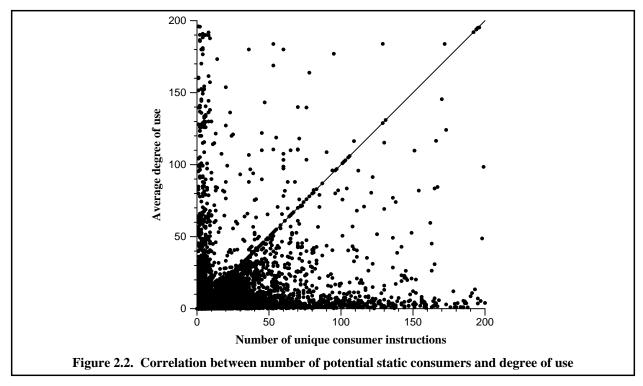

| Figure 2.2.  | Correlation between number of potential static consumers and degree of use        | 8  |

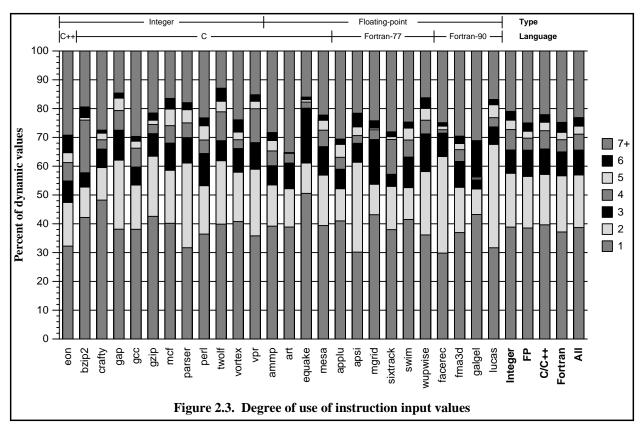

| Figure 2.3.  | Degree of use of instruction input values                                         | 20 |

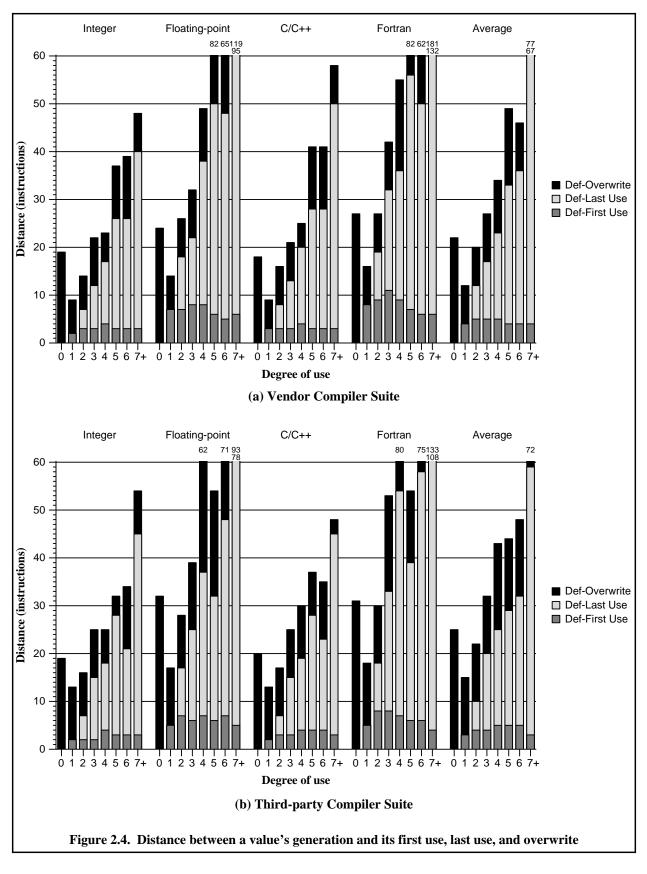

| Figure 2.4.  | Distance between a value's generation and its first use, last use, and overwrite? | 26 |

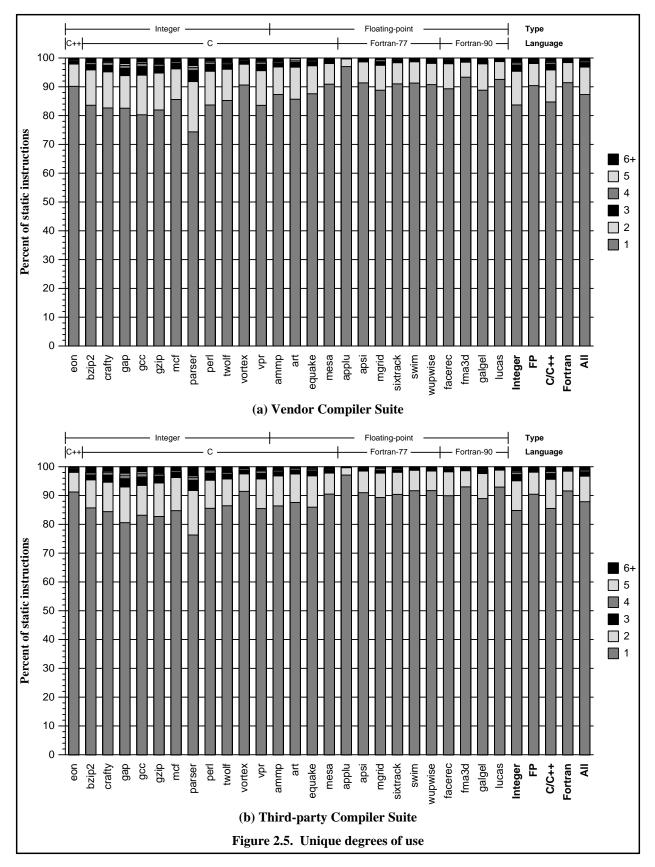

| Figure 2.5.  | Unique degrees of use                                                             | 28 |

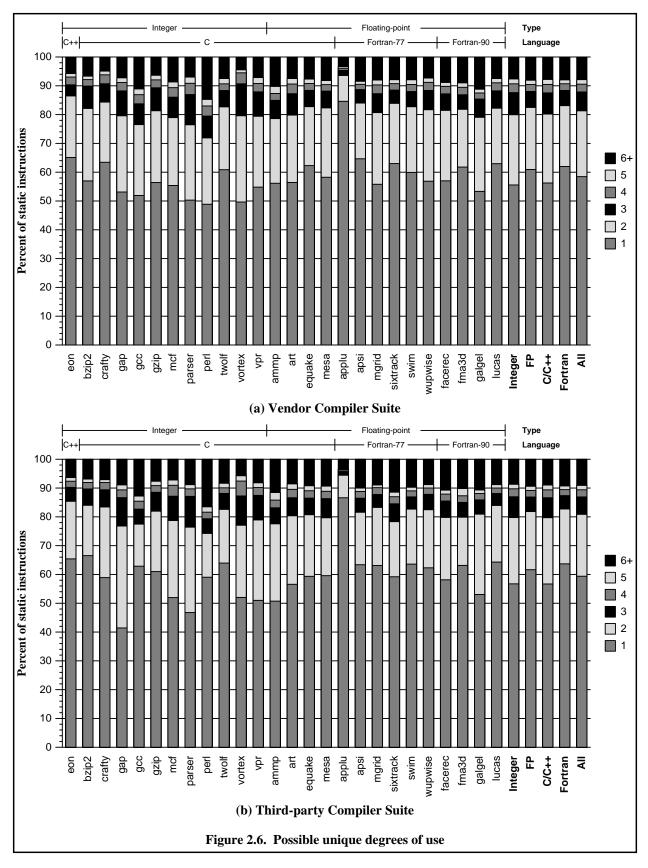

| Figure 2.6.  | Possible unique degrees of use                                                    | 29 |

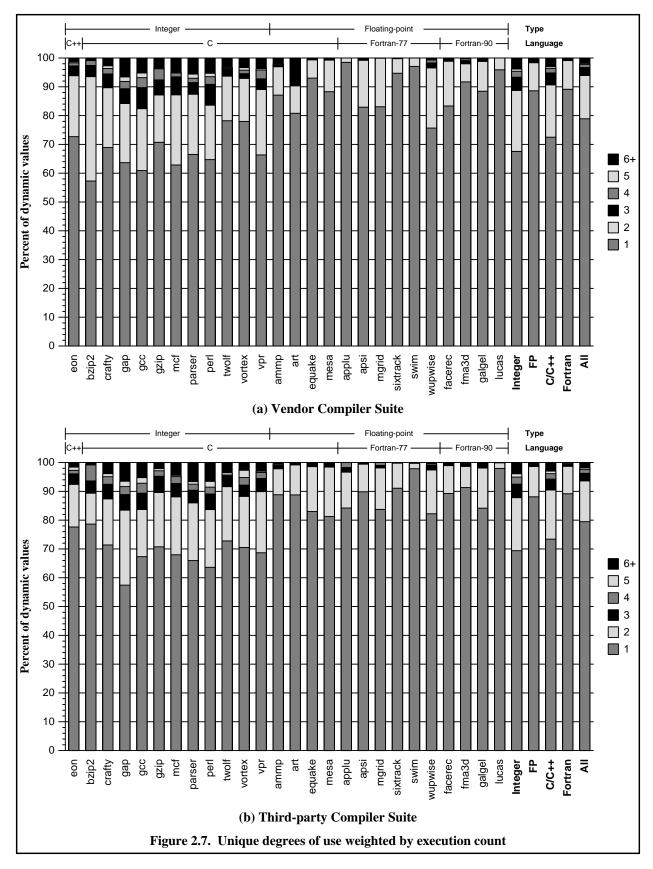

| Figure 2.7.  | Unique degrees of use weighted by execution count                                 | 31 |

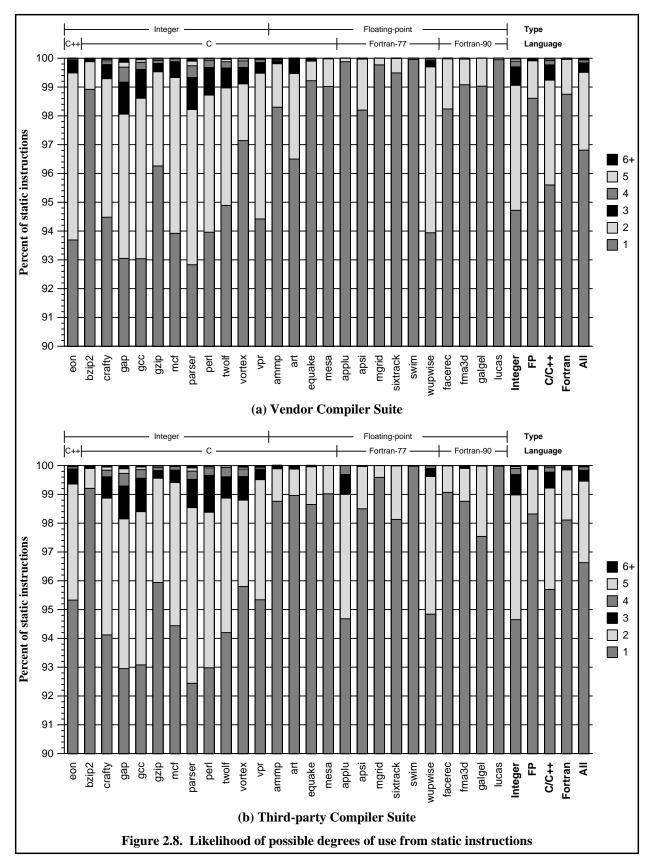

| Figure 2.8.  | Likelihood of possible degrees of use from static instructions                    | 32 |

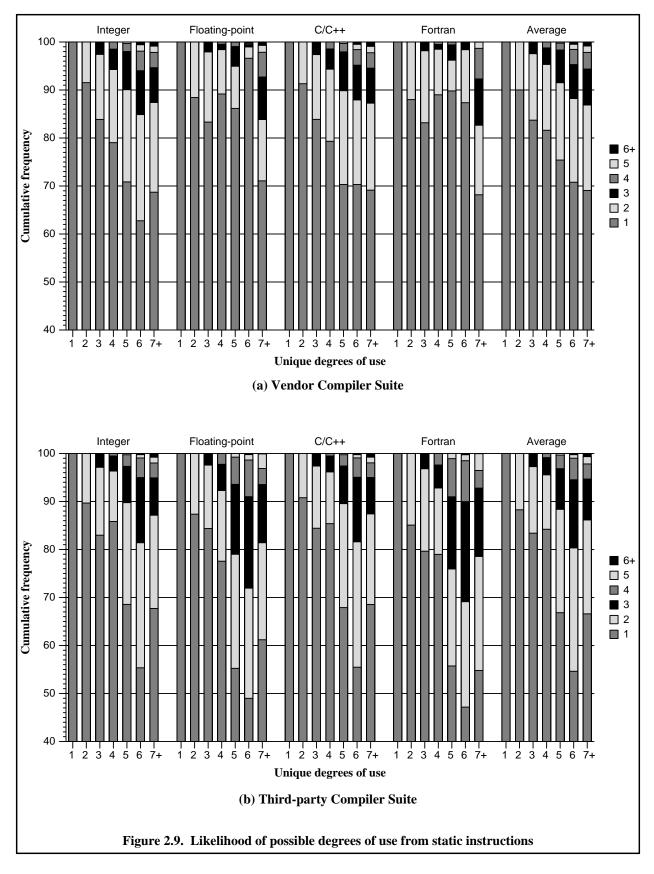

| Figure 2.9.  | Likelihood of possible degrees of use from static instructions                    | 33 |

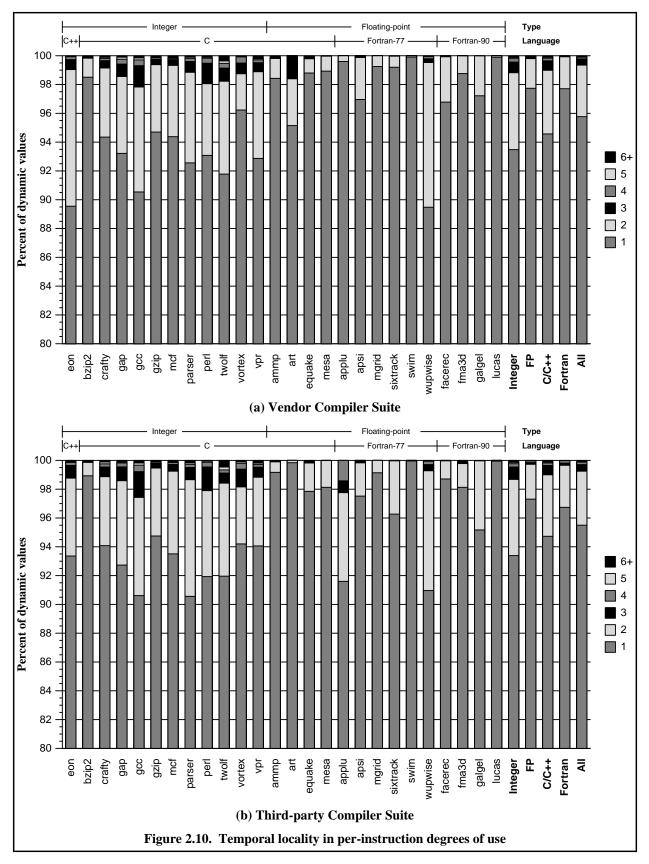

| Figure 2.10. | Temporal locality in per-instruction degrees of use                               | 35 |

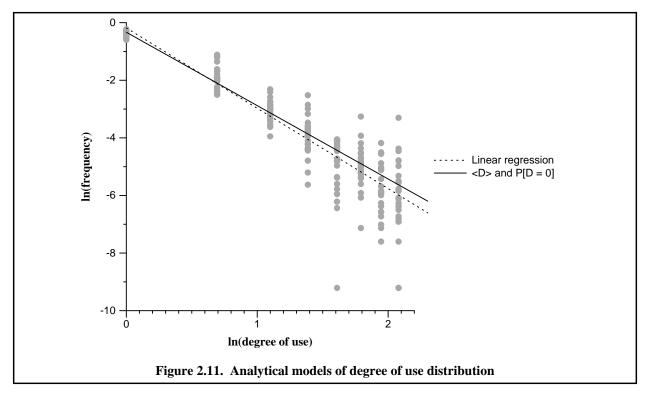

| Figure 2.11. | Analytical models of degree of use distribution                                   | 38 |

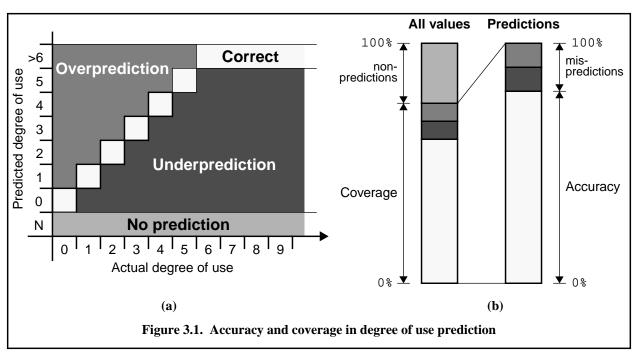

| Figure 3.1.  | Accuracy and coverage in degree of use prediction                                 | 14 |

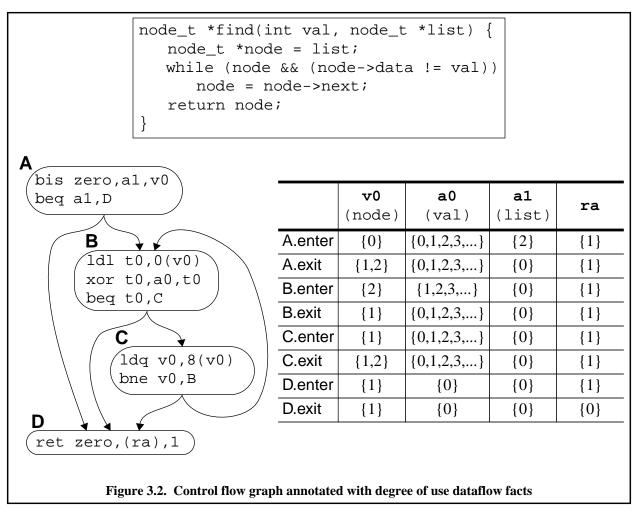

| Figure 3.2.  | Control flow graph annotated with degree of use dataflow facts                    | 52 |

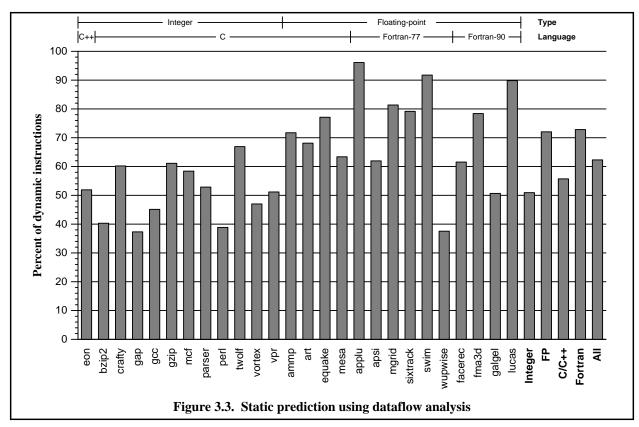

| Figure 3.3.  | Static prediction using dataflow analysis                                         | 54 |

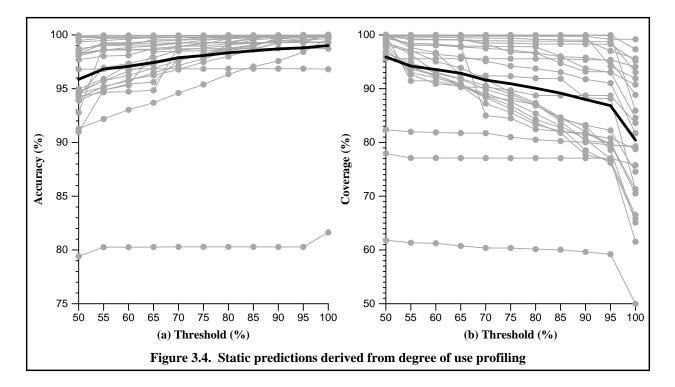

| Figure 3.4.  | Static predictions derived from degree of use profiling                           | 56 |

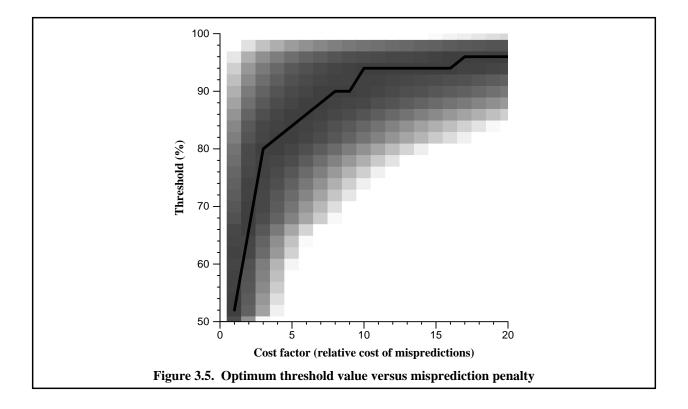

| Figure 3.5.  | Optimum threshold value versus misprediction penalty                              | 57 |

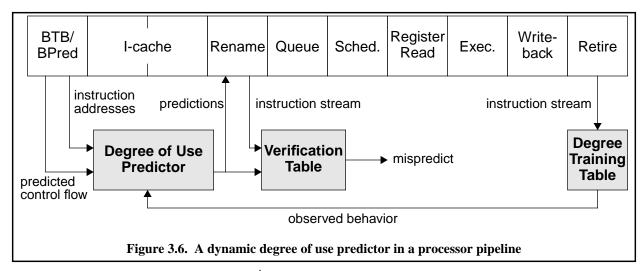

| Figure 3.6.  | A dynamic degree of use predictor in a processor pipeline                         | 59 |

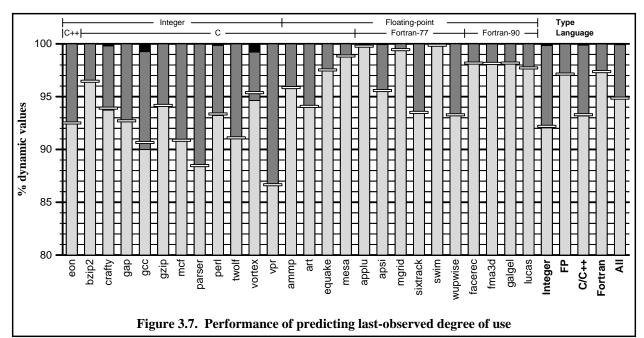

| Figure 3.7.  | Performance of predicting last-observed degree of use                             | 51 |

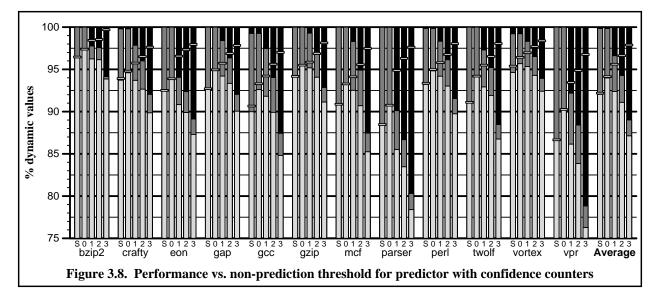

| Figure 3.8.  | Performance vs. non-prediction threshold for predictor with confidence counters . | 54 |

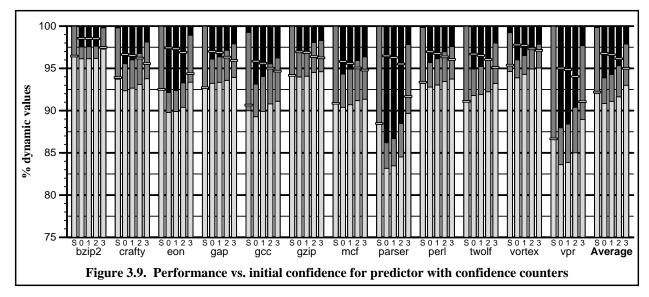

| Figure 3.9.  | Performance vs. initial confidence for predictor with confidence counters         | 55 |

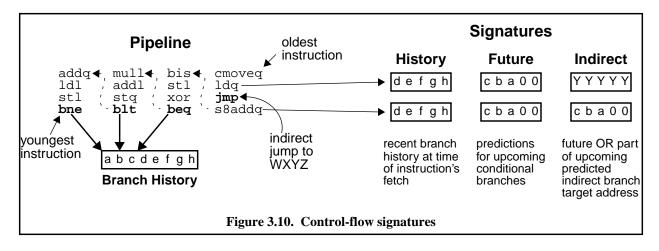

| Figure 3.10. | Control-flow signatures                                                           | 57 |

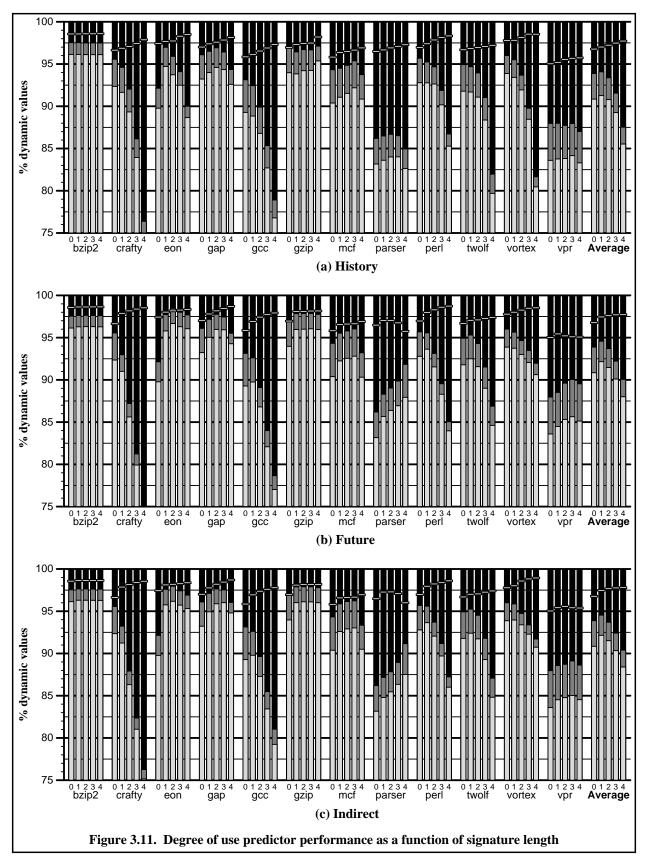

| Figure 3.11. | Degree of use predictor performance as a function of signature length             | 59 |

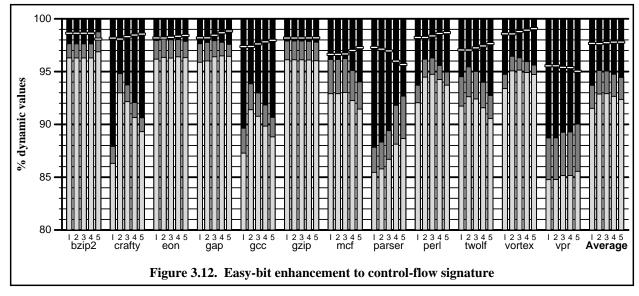

| Figure 3.12. | Easy-bit enhancement to control-flow signature                                    | 71 |

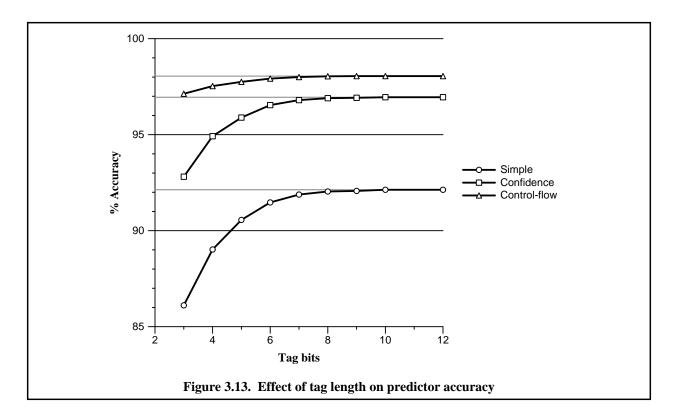

| Figure 3.13. | Effect of tag length on predictor accuracy                                        | 73 |

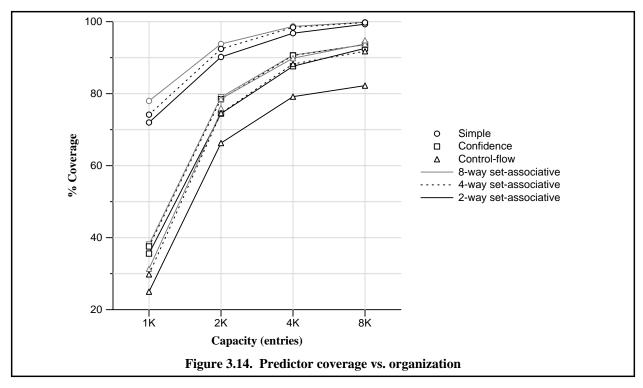

| Figure 3.14. | Predictor coverage vs. organization                                               | 75 |

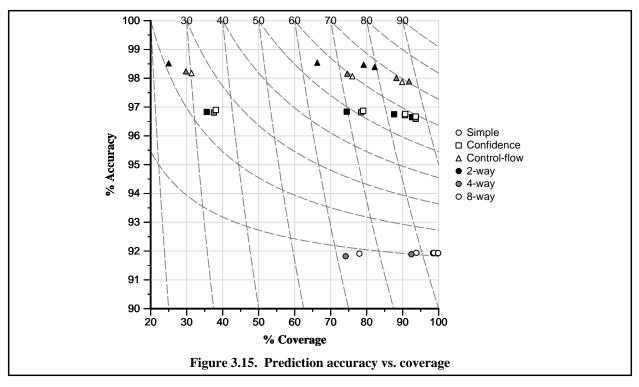

| Figure 3.15. | Prediction accuracy vs. coverage                                                  | 76 |

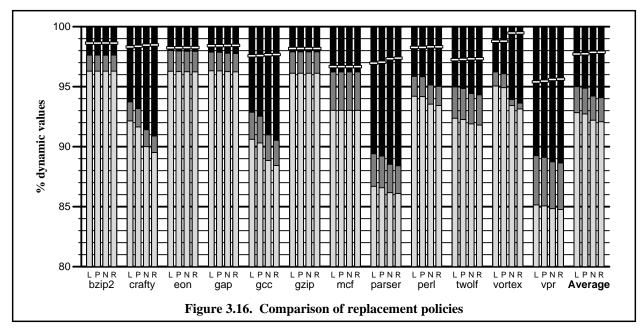

| Figure 3.16. | Comparison of replacement policies                                                | 77 |

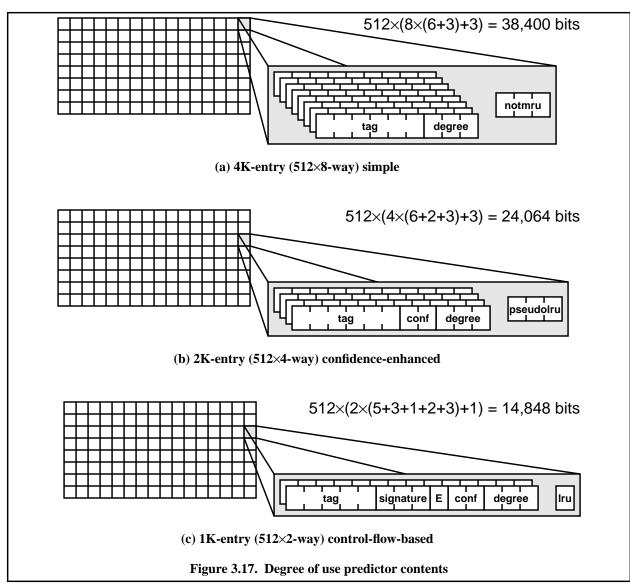

| Figure 3.17. | Degree of use predictor contents                                                  | 79 |

|                                                                                 | xi  |

|---------------------------------------------------------------------------------|-----|

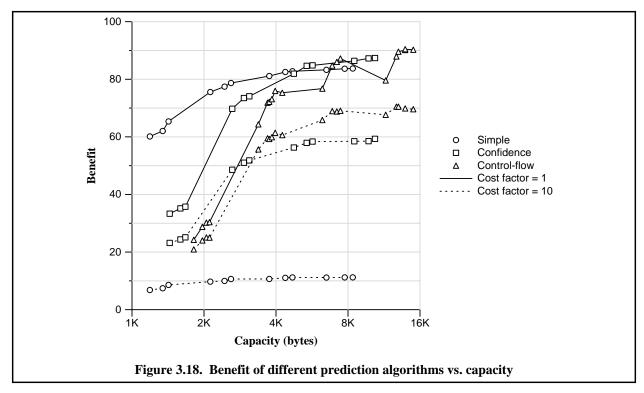

| Figure 3.18. Benefit of different prediction algorithms vs. capacity            | 80  |

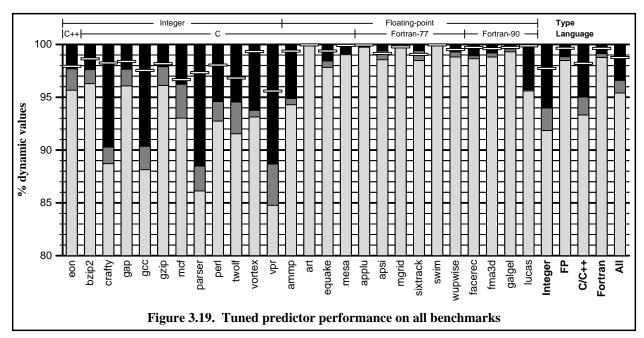

| Figure 3.19. Tuned predictor performance on all benchmarks                      | 81  |

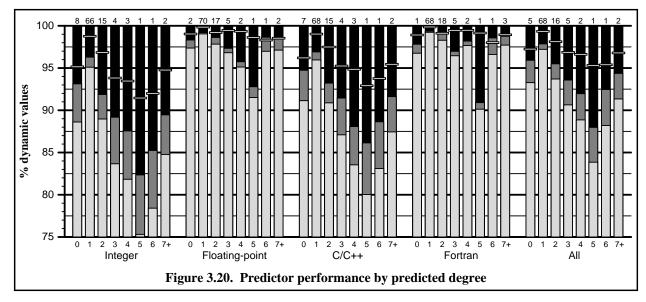

| Figure 3.20. Predictor performance by predicted degree                          | 82  |

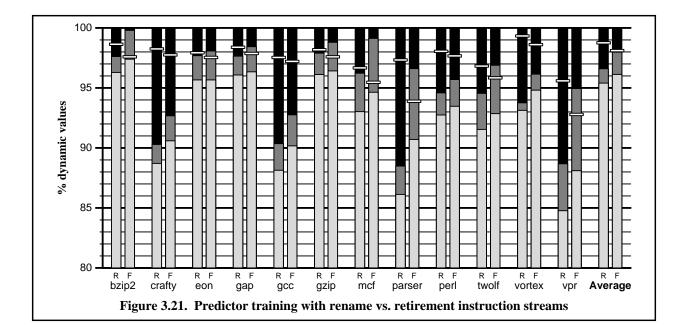

| Figure 3.21. Predictor training with rename vs. retirement instruction streams  |     |

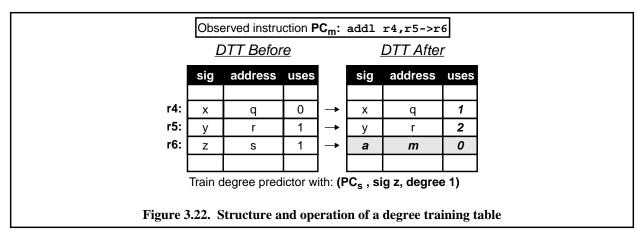

| Figure 3.22. Structure and operation of a degree training table                 | 85  |

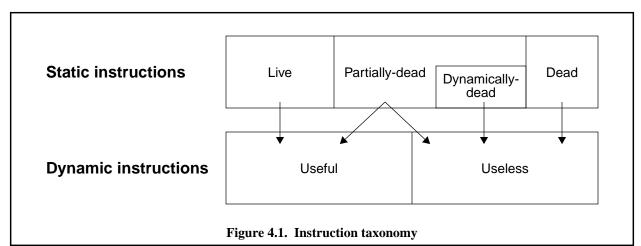

| Figure 4.1. Instruction taxonomy                                                |     |

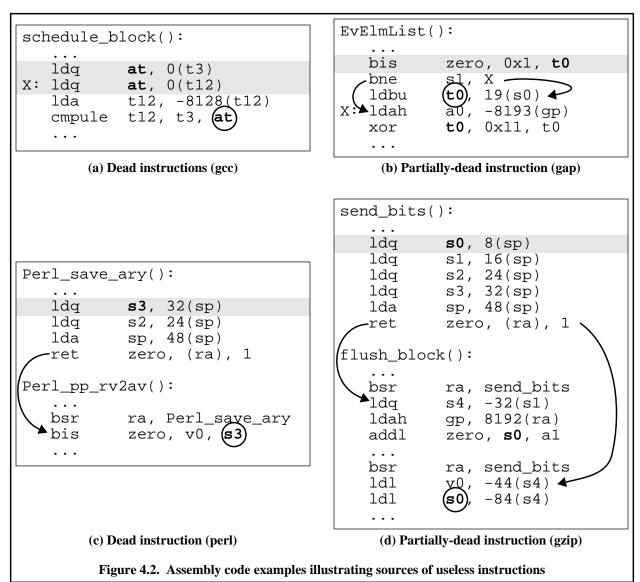

| Figure 4.2. Assembly code examples illustrating sources of useless instructions |     |

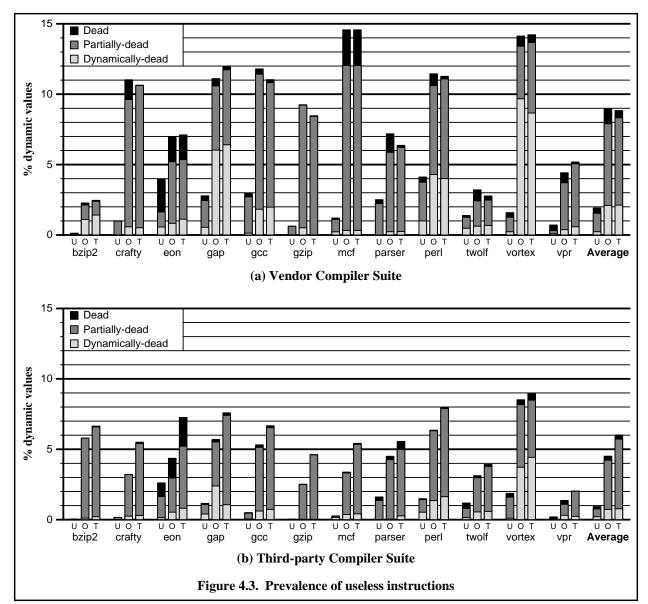

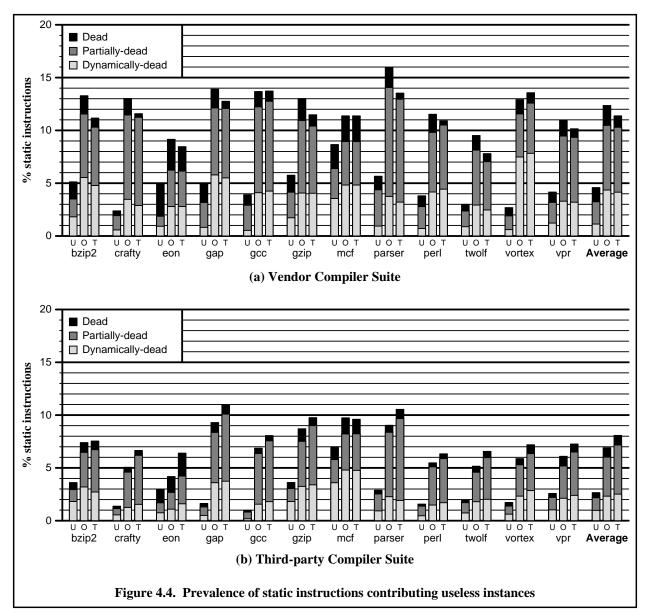

| Figure 4.3. Prevalence of useless instructions                                  | 95  |

| Figure 4.4. Prevalence of static instructions contributing useless instances    |     |

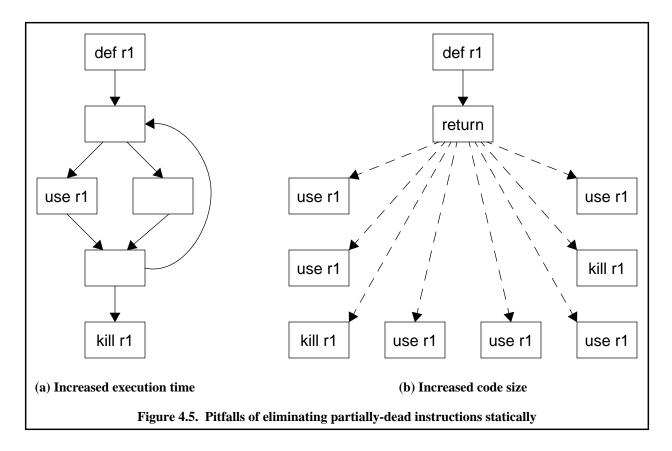

| Figure 4.5. Pitfalls of eliminating partially-dead instructions statically      | 99  |

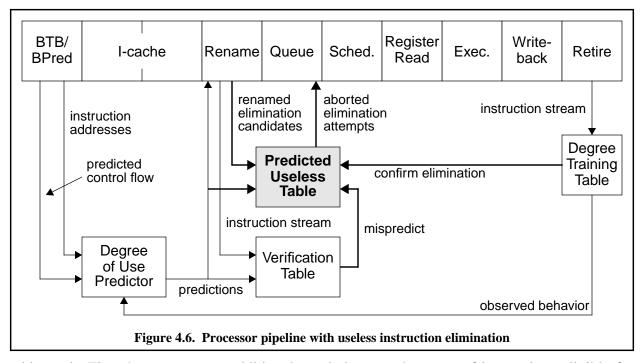

| Figure 4.6. Processor pipeline with useless instruction elimination             | 105 |

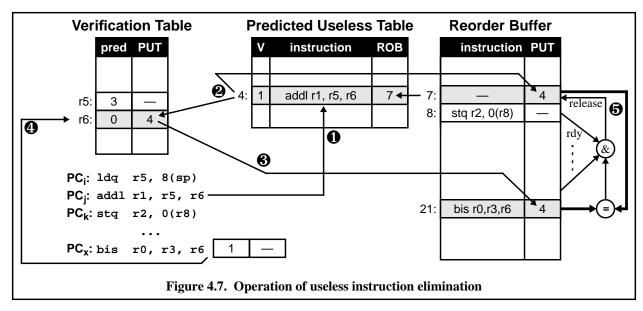

| Figure 4.7. Operation of useless instruction elimination                        | 107 |

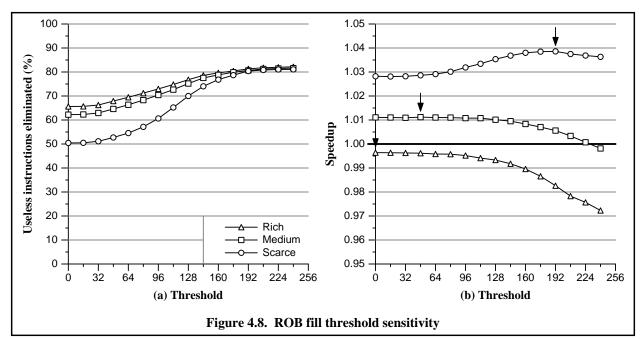

| Figure 4.8. ROB fill threshold sensitivity                                      | 116 |

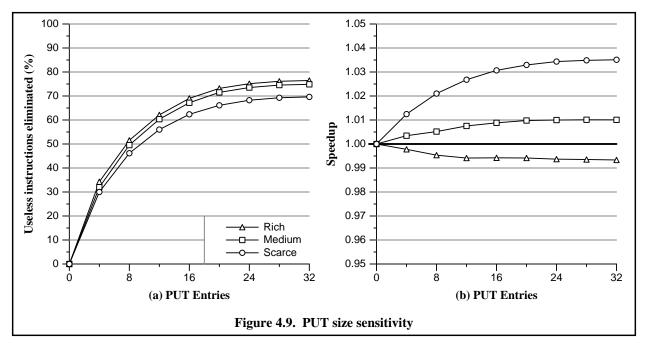

| Figure 4.9. PUT size sensitivity                                                | 117 |

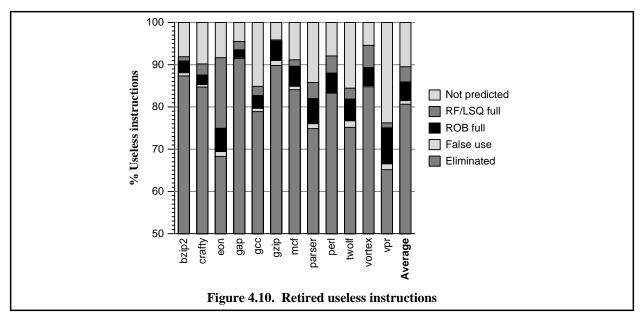

| Figure 4.10. Retired useless instructions                                       | 119 |

| Figure 4.11. Resource occupancy                                                 | 120 |

| Figure 4.12. Performance                                                        | 121 |

| Figure 5.1. Contents of physical register file                                  | 127 |

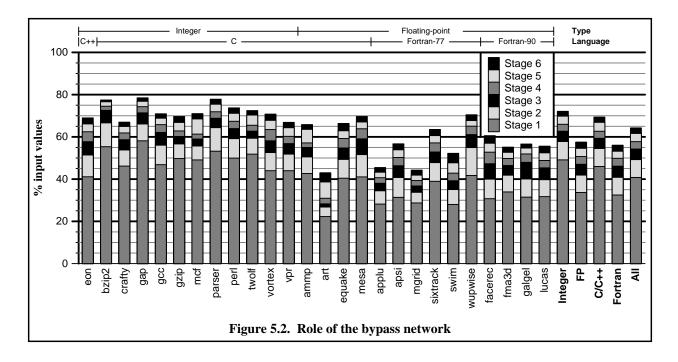

| Figure 5.2. Role of the bypass network                                          | 127 |

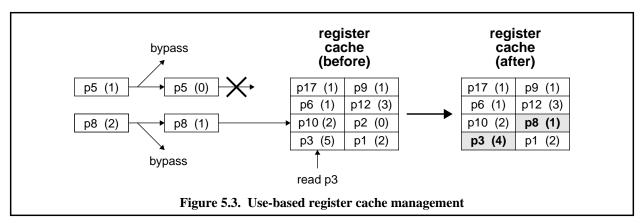

| Figure 5.3. Use-based register cache management                                 | 129 |

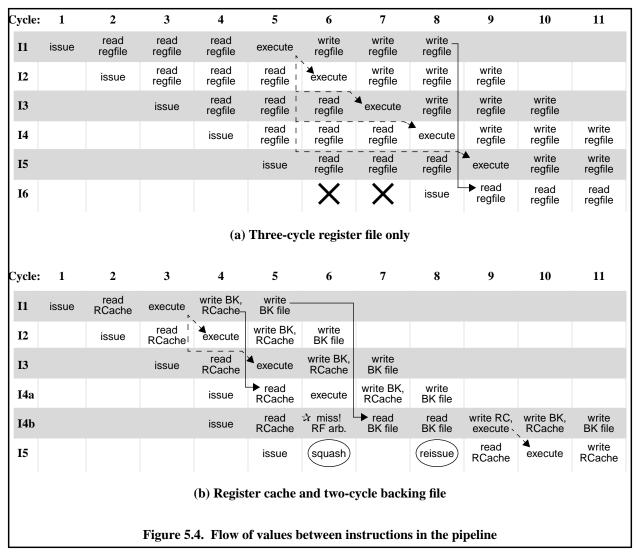

| Figure 5.4. Flow of values between instructions in the pipeline                 | 131 |

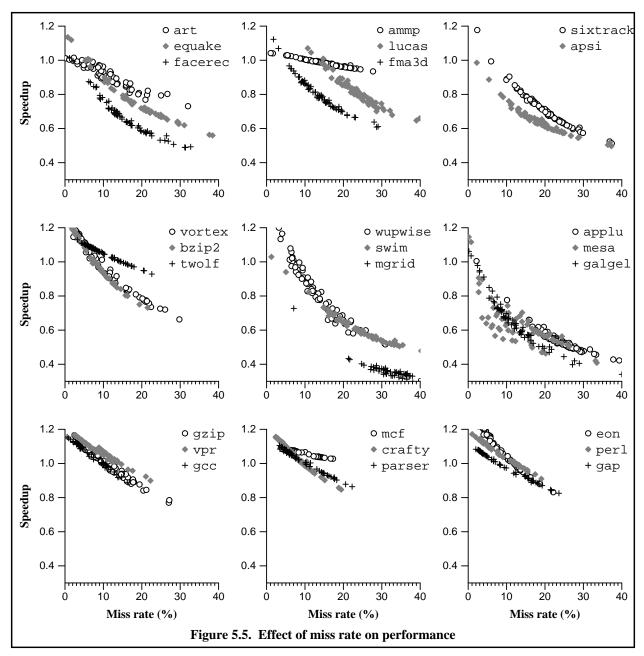

| Figure 5.5. Effect of miss rate on performance                                  | 144 |

| Figure 5.6. Insertion policies                                                  | 146 |

| Figure 5.7. Replacement policies                                                | 150 |

| Figure 5.8. Hybrid replacement policies                                         | 151 |

| Figure 5.9. Register cache misses                                               | 153 |

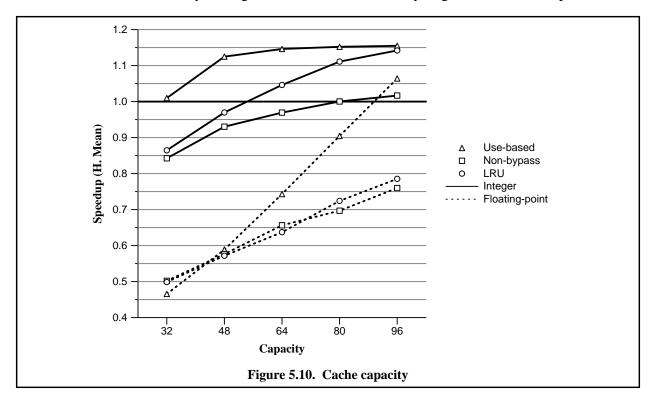

| Figure 5.10. Cache capacity                                                     | 154 |

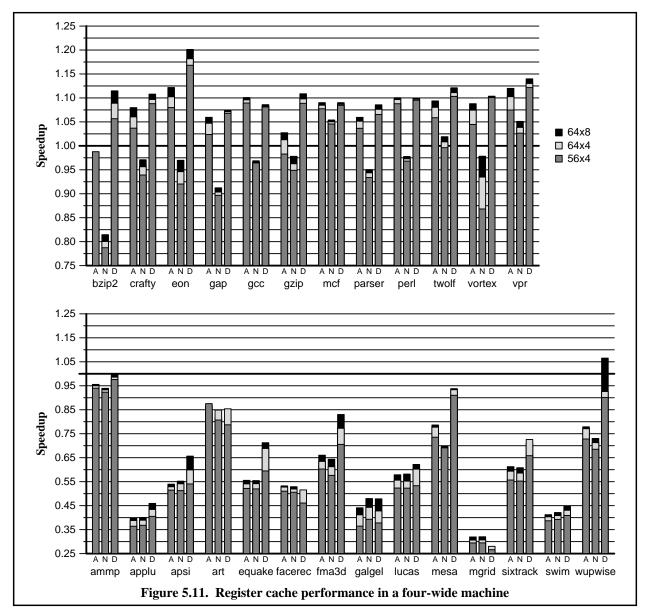

| Figure 5.11. Register cache performance in a four-wide machine                  | 156 |

| Figure A.1. Microarchitecture modeled by the timing simulator                   | 190 |

# List of Tables

| Table 2.1: | Degree of Use Characteristics                         |

|------------|-------------------------------------------------------|

| Table 2.2: | Degree of Use Properties of Instruction Groups        |

| Table 2.3: | Average Degree of Use by Register Class               |

| Table 2.4: | Analytical Model Parameters                           |

| Table 3.1: | Aliasing Rates                                        |

| Table 4.1: | Types of Useless Instructions                         |

| Table 4.2: | Number of Inputs of Useless Instructions 104          |

| Table 4.3: | Simulated Processor Parameters                        |

| Table 4.4: | Functional Unit and Issue Port Configurations         |

| Table 4.5: | Utilization Impact of Useless Instruction Elimination |

| Table 5.1: | Simulated Processor Parameters                        |

| Table 5.2: | Evaluating Use-Based Filtering                        |

| Table A.1: | Compiler Suites                                       |

| Table A.2: | Tuned-Benchmark Compilation Options                   |

| Table A.3: | Fetch Pipeline Parameters                             |

| Table A.4: | Decode Pipeline Parameters                            |

| Table A.5: | Instruction Window and Scheduler Parameters 194       |

| Table A.6: | Register File and Execution Parameters                |

| Table A.7: | Commit Parameters                                     |

| Table A.8: | Memory System Parameters                              |

# **Chapter 1**

# Introduction

At a very high level, the operation of a general-purpose computer can be broken into two tasks: the manipulation of data by individual instructions and the communication of data values among the appropriate instruction instantiations. Of these two tasks, inter-instruction value communication is vastly more difficult and is the origin of much of the complexity found in high-performance processors today.

This dissertation explores the relationship of a value's degree of use to the nature of its communication. A value's degree of use is simply the number of times the value is used as an input by the successive instructions of the program, and it is an indicator of the resources needed to distribute that value to its consumers. Most values exhibit very simple communication patterns, yet current implementations handle all values uniformly. The resulting communication inefficiency manifests as inflated complexity, communication latency, and power dissipation.

The application of speculative degree of use information allows for the handling of each value to be tuned to its particular characteristics. Two such optimizations are presented: one completely avoids the creation of a value when it will not be communicated to any subsequent instructions, while the other applies degree of use knowledge to manage the set of values kept in a small, lowlatency register cache.

## **1.1 Inter-Instruction Value Communication**

Inter-instruction value communication is a need common to all general-purpose processing architectures. All such architectures provide primitives—instructions—for the manipulation of certain data representations. The operation of a computer entails the execution of instructions on a set of data according to a program. The actions specified by the individual instructions are generally simple and have changed little since the introduction of the first programmable computers. The versatility of a computer results from the ability to describe arbitrarily-complicated operations in terms of these simple instructions. Regardless of the variety and richness of the available instructions, however, nearly all tasks of interest will require the sequential application of multiple primitives. Thus, *the communication of data values between the instructions constituting a program is a fundamental aspect of computing*.

The primary motivation for this work is that this task of inter-instruction value communication is difficult. While part of this difficulty is inherent to the actual communication of values, much of it results from how communication mechanisms are implemented in current architectures. The sequential, register-based architecture is the basis for the majority of modern general-purpose processor implementations. Most value communication in this architecture occurs through a limited number of storage locations called registers, and it is this class of communication that is the focus of this dissertation. Achieving high performance under this model requires complex value communication mechanisms. Technology trends will render current methods of register value communication inadequate for future high-performance implementations.

#### **1.1.1** Inter-instruction communication in sequential architectures

In a sequential architecture, inter-instruction communication is specified in a program via named storage locations. Each instruction *addresses* (i.e., specifies) storage locations where its inputs may be found and where its output should be placed. Thus, value communication is specified indirectly: instructions do not name the consumers of their result, nor do the consumers name the producers of their inputs. Instead, a value may be communicated between two instructions if they name a common storage location. This condition is necessary but not sufficient. The two instructions must occur in the proper temporal sequence, with the producer of the value occurring prior to the consumer. Additionally, no intervening instruction can place its result in the storage location.

tion or it would become the producer. The sequence of instructions within the program, descriptively called *program order*, is therefore fundamental to the specification of value communication, and this is what gives the sequential processing model its name.

It is important here, and throughout the remainder of this document, to distinguish between two different types of instructions. A *static instruction* is an atom of a program; it specifies a single kind of supported operation (e.g., addition), and the locations of its input(s) and output(s). As its name implies, it does not change during the execution of the program.<sup>†</sup> A given static instruction may execute many times on different values by virtue of the storage location(s) it specifies containing different values each time. One such instance of a static instruction is called a *dynamic instruction*. A dynamic instruction only occurs once; its inputs are fixed to the contents of the named storage locations at the time of its instantiation.

#### 1.1.2 Register value communication

Two different classes of storage locations may be named by the static instructions of the program: registers and memory. Registers comprise a small number—architecture dependent, but on the order of a few tens—of storage locations that are named directly. In other words, given a static instruction that names a particular register as an input, *every* dynamic instance of that instruction will also receive its input from the same register. The capacity of memory is vastly larger (ideally infinite). The number of individually-addressable memory locations hinders the direct addressing of particular memory location (although some architectures support it); generally, a memory location is named with the aid of a value stored in a register.

This dissertation focuses on the value communication occurring through registers because it is the dominant mode of inter-instruction communication, in spite of the much smaller register namespace. Register-based architectures are aptly named: nearly every useful instruction specifies at least one register as a source or destination. *Load-store architectures* are a subclass of register-based architectures in which only two specific classes of instructions can address memory. A *load* moves a value from memory to a register, while a *store* performs the reverse operation. In each case, another register contains a value used in addressing the memory location. While all

<sup>&</sup>lt;sup>†</sup> Stored-program computers do not distinguish between instructions and other kinds of program data. A few architectures allow running programs to modify their program code; the occurrence of such *self-modifying code* is rare even where supported.

other types of operations may communicate only via registers, these memory operations still use two registers each, illustrating the importance of register value communication. Architectures such as the IA-32 allow instructions to specify a memory location as a source or destination; however, most implementations convert these instructions into a sequence of simpler ones communicating via registers and using loads or stores as needed [44].

#### **1.1.3** Meeting the demands of parallelism

Achieving high-performance in a sequential architecture necessitates overcoming an inherent disadvantage of the programming model. While a sequential program imposes a total ordering among all instructions, a given instruction frequently does not depend on the execution of all prior instructions. The useful consequence of this fact is that the execution of instructions that are independent of one another can take place simultaneously, reducing the total time required to execute all of the operations specified by the program. The existence of independent instructions within a program is referred to as *instruction-level parallelism*.

Exploiting parallelism for high-performance using register-based communication demands: (1) many register storage locations, (2) high register access bandwidth, (3) many communication endpoints, and (4) low access latency. Each simultaneously-executing instruction requires input values from storage (some of which may be shared) and storage for its result, requiring more total register storage than if execution occurred one-instruction-at-a-time. Even if few unique register names are available, register renaming enables more physical storage locations to be in use concurrently than the number of register names would otherwise support.<sup>†</sup> The adoption of simultaneous multi-threading [85], which increases available parallelism by offering multiple execution contexts with their own register namespaces, requires even more register storage [13]. While the quantity of register storage grows with the degree of parallelism, so too does the access bandwidth required of that storage. Each instruction must access the register storage to retrieve its input operands and store its result value; simultaneously-executing instructions must perform these

<sup>\*</sup> Where parallelism exists, it can be obscured by false dependences introduced as a result of a limited register namespace. Sequences of instructions belonging to otherwise independent computations are serialized merely by virtue of specifying the same register at some point. Register renaming maps the limited number of names for register locations (the architectural registers) to a much larger—and implementation dependent—number of storage locations for actual values (the physical registers). Physical register identifiers are substituted for architectural register names such that real data-dependences are preserved.

accesses concurrently. Furthermore, the instructions will occupy different execution resources, each of which needs its own connections to the register storage. Finally, the latency of the access to register values must not suffer unduly: the benefit of executing many instructions at a time is diminished if the instructions take much longer to obtain their input values.

Much of the complex circuitry in current processors exists to support these demands of register value communication. Besides the register file itself, this circuitry includes the bypass network and the instruction scheduling hardware (in dynamically-scheduled processors, which are the focus of this work) [66]. The bypass network provides direct interconnection among different execution units so that latency-critical value communication may occur without traversing the register storage. The instruction scheduler enforces program data-dependences by allowing instructions to execute only after their input values are available; thus, its design is heavily impacted by the nature of inter-instruction communication. In some instances, the instruction scheduling apparatus even stores register values [11, 67, 83]. The resources spent supporting inter-instruction value communication with these structures represents a significant challenge facing future designs.

#### 1.1.4 The problem

Value communication mechanisms benefit less from technology scaling than other types of circuitry because they are large, centralized, and wire-dominated [66]. First, the quantity of storage accessible in a fixed period of time relative to the latency of a fixed computational operation (e.g., addition) is decreasing [1]. Thus, the relative latency of the access to a fixed amount of register storage will increase. If the amount of register storage must also increase, the effect will be correspondingly larger. Supporting more simultaneous accesses to the register storage has a penalty similar to that of increasing its capacity. A second—and not unrelated—trend is the smaller relative improvement in the speed of wires versus transistors as semiconductor technology moves forward [10].<sup>†</sup> Slow interconnection imposes a cost for increasing the number of execution units that must access the value storage structures. In addition, it reduces the effectiveness of bypass-

<sup>†</sup> Physical limitations to scaling, while of increasing importance, should not prevent the continuous improvement of CMOS semiconductor technology through at least the end of the decade. Further scaling depends on the development of and transition to non-classical CMOS technologies [45].

ing, which attempts to reduce the impact of register access latency by passing result values directly among execution units. Finally, the emergence of static and dynamic power dissipation as architectural constraints demands efficient implementation of the large amount of value-communication circuitry [16, 65].

The complexity of value communication structures arises from their generality. They are designed to support arbitrary data-dependence relationships among all in-flight instructions. Thus, their complexity depends primarily on details of the *implementation* (e.g., the pipeline width and depth), even as the value communication called for by a given program remains constant. As a result, the overhead of current value communication mechanisms increases as pipelines grow to exploit parallelism.

Moving forward, novel value communication mechanisms must be devised to exploit parallelism more efficiently. Specialized mechanisms, optimized for specific value communication patterns, can fill this role. Rendered independent of the scaling of the pipeline, they will be more resistant to the negative effects of technology trends. A prerequisite for the application of these alternative mechanisms, however, is a way of classifying the communication requirements of each value.

# **1.2 Degree of Use**

The thesis of this work is that a value's *degree of use* provides the most pertinent information regarding that value's communication requirements. Degree of use is simply the number of consumers of a particular register value. It is a dynamic property—that is, successive instantiations of the same instruction in the program may lead to values with different degrees of use. Values that have a high degree of use (i.e., many consumers) must be widely available (e.g., to multiple functional units) at low latencies for long periods of time. In contrast, values that are used but once do not require such a powerful (and expensive) communication mechanism. The best communication mechanism for a value depends on the needs of that value relative to the capabilities of the various available communication mechanisms. The relative proportions of these classes of values will determine the forms of and relative needs for these different mechanisms.

To avoid unwieldy sentences, the degree of use "of an instruction" or "of a register" will be used occasionally throughout this dissertation. Of course, degree of use is a property of a specific dynamic value. These phrases are shorthand for the degree of use of the value generated by a particular instruction or the degree of use of the value in a particular register, respectively.

#### 1.2.1 An example

Figure 1.1 illustrates some of the interesting properties of degree of use using a short example function that returns the first occupied bucket in a hash table. The C source code example appears on the left and the corresponding Alpha [5] assembly code on the right. A portion of the dynamic dataflow graph corresponding to a particular execution of the function appears at the bottom of the figure.

Alpha assembly code will appear throughout this dissertation, so a brief explanation is provided here. Most instructions with a register destination (e.g., arithmetic and logical operations) name that register on the right. The sole exceptions are load instructions, which name the destination register on the left. All load instruction mnemonics begin with ld (the lda and ldah instructions perform address computations and do not access memory, although their destination registers still appear on the left). Memory addresses for loads and stores appear on the right and consist of a fixed offset to be added to the contents of a base register appearing within parentheses. Control instructions can be identified by the presence of a label, except for the indirect jumps jmp, jsr, and ret, which branch to an address stored in a given register (appearing within parentheses).

The figure illustrates several interesting aspects of degree of use. First, many values are used only once. Values assigned to  $\pm 2$  and  $\pm 3$ , for example, will always exhibit a degree of use of one. Of the 23 values represented in the dataflow graph, 14 of them are used only once. Second, some static instructions always generate values with the same degree of use (e.g., the s8addq and subl instructions). Instructions whose results are live across one or more conditional branches can have different degrees of use depending on the particular path taken through the program. For example, the value in  $\pm 1$  has a degree of use of one in the final loop iteration, but a degree of use of three in all prior iterations. Finally, note that it is possible for a value to have a degree of use of zero (i.e., never be used). Had the loop terminated due to the bge being taken (rather than the termination of the while loop as shown), the two shaded nodes in the dataflow graph would not be executed and the value generated by the ldq instruction would not be used.<sup>†</sup>

#### 1.2.2 Classifying values using degree of use

The example clearly demonstrates how degree of use provides information about the communication of a dynamic value lost as a consequence of the programming model. The level of indirection inherent to register-based architectures obscures this information for the sake of compact instruction encoding. Thus, the ultimate fate of an instruction's result is hidden when that result is generated: it may be read from the destination register once or many million times or any number in between. Without additional information, all value-producing instructions have no choice but to place their results into the specified registers. Also, the microarchitecture must ensure that all registers can support being read any number of times. These consequences are at the root of the inefficiencies in current inter-instruction communication mechanisms.

Degree of use information restores knowledge about the fates of individual dynamic values. Using this knowledge, it is possible to identify values that have different communication needs and handle them in an optimized manner. In fact, degree of use offers the most direct measure of communication, as it quantifies the actual flow of a value to its consumers. Therefore, it is a property solely of the value's dataflow (and, by extension, the value's role in the program). Possible

<sup>&</sup>lt;sup>†</sup> Because of the focus on register value communication, values are not tracked through memory. Store instructions are terminal: from the perspective of register values, a store represents one use of each of two register values (one containing an address and another the data to be written to memory). Subsequent loads of this stored value would each be considered to create a new value.

alternative measures are influenced by other factors than the communication structure of the program, such as dynamic events. For example, consider classifying a value's communication by its lifetime: values generated by the same instruction and communicated in the same manner may have significantly different lifetimes in consecutive executions due to an unrelated L2 cache miss.

#### **1.2.3** The need for prediction

Using a value's degree of use to optimize its communication requires knowledge of the future. The degree of use of a particular value is calculated by counting its uses; thus, it is not certain until the last use has been observed. Prediction is a well-understood technique for obtaining information that would not normally be available (e.g., the direction of a conditional branch prior to its execution). Based on the predicted information, actions can be taken speculatively, and the prediction verified later. Given high enough prediction accuracy, the effect is the same as having future knowledge.

This work describes *degree of use prediction*, which supplies high-accuracy speculative degree of use information for values early in the processing of their producer instructions. Degree of use prediction is successful because the dataflow patterns in programs are predictable. As demonstrated by the example, many instructions generate values that always have the same number of uses. Determining the degrees of use for values from these instructions is trivial. Even where control flow can affect the degree of use of values from a particular instruction, the predictability of control flow (demonstrated by the success of branch prediction) leads to similar predictability in the degree of use. As with branch prediction, past behavior is a very good predictor of the future.

### **1.3** Contributions

The initial work on degree of use arose in connection with the Multiscalar project [78]. In this work, Franklin and Sohi presented the distribution of degree of use (coining that term in the process) of dynamic values [32]; they observed the dominance of single-use values and used their observations to propose an alternative value-communication mechanism—namely, a distributed register file. These observations (low average number of uses, many single-use values) have since been used to justify certain design decisions or motivate complete optimizations (e.g., [8, 24, 43,

50]), but none has yet exploited knowledge of number of uses of a particular value because of the unavailability of this information. This dissertation addresses how to obtain that information, its relationship to the role of a value within the program, and how it can be exploited.

The first major contribution of this work is a thorough exploration of the degree of use properties of register values. The observations of Franklin and Sohi are confirmed and expanded upon; the use of a different architecture as well as different benchmarks and compilers broaden the scope of their initial study. Correlations between the role of a value within a program and its degree of use help to explain some of the consistency that is observed with respect to the distribution of different degrees of use. An in-depth characterization of the stability of the degree of use of individual instructions demonstrates the feasibility of history-based dynamic prediction schemes. Finally, the distribution of values with different degrees of use is examined analytically. A previously-proposed analytical model is extended, and the mean degree of use is derived from considerations of the instruction mix.

The demonstration of accurate static and dynamic degree of use prediction is the second contribution of this work. The degree of use of a value is determined by its role in the program; since the role of a given instruction of the program is fixed, the possible degrees of use of values produced by that instruction are pre-determined. A formulation of the degree of use dataflow problem is presented, which, when solved with standard interprocedural dataflow analysis techniques, allows assignment of the set of possible degrees of use to each static instruction of the program. This assignment is the basis for static degree of use prediction. Dynamic degree of use prediction, on the other hand, is based on run-time profiling of degree of use. Here, the novel concept of forward control flow is introduced, which offers short-range path look-ahead as a direct consequence of pipelining. In more advanced dynamic predictors, this information can be used to distinguish among different previously observed degrees of use for the same instruction.

The third significant contribution of this work is *useless instruction elimination* (UIE). This technique avoids the execution of instructions that produce values that will not be used (i.e., degree of use zero values). UIE is representative of the class of optimizations that uses degree of use information to affect the handling of the producer instruction. The performance benefit of UIE is limited by the frequency of occurrence of useless values and the importance of resource contention. Nonetheless, resource utilization is reduced, which can lead to lower power dissipa-

tion. A minor contribution associated with this optimization is an in-depth study of the existence and properties of the useless instructions, which implicates compiler optimizations in increasing the incidence of useless instructions.

Finally, *use-based register caching* applies degree of use information more broadly. The large, slow register file is replaced by the combination of the bypass network and a small, fast register cache. Degree of use information is used to determine the expiration of a value's usefulness by comparing the number of actual uses with the prediction. Only those values that are useful after bypassing are placed in the register cache, enabling its size advantage over the register file. The register file is relegated to the task of recovery, supplying values that were mistakenly dropped from or never placed in the cache.

# 1.4 Methodology

This section summarizes aspects of the methodology common to the different experiments conducted. The issues presented here are general in nature; details specific to a given experiment are provided in the associated chapter where necessary. Many additional details too cumbersome or arcane to present within a chapter (or here) are described within the appendix.

### 1.4.1 Benchmarks

The benchmarks used in all experiments are from the SPEC CPU 2000 suite [80]. Depending on the experiment, data is provided for all benchmarks (26 total) or only the integer benchmarks (12 total). Except where noted, the training inputs provided with the benchmark suite were used. Benchmark binaries generated with different compilers and compiler options were used in some experiments. Descriptions of the compilers and the flags used in each configuration may be found in section A.2 of the appendix. If unspecified for a particular experiment, the binaries used were those compiled with the Compaq/Digital C, C++, and Fortran-90 compilers (cc, cxx, and f90 under Digital UNIX 4.0, respectively) with the flags that yielded the best performance on an aggressive (8-wide, deeply-pipelined) simulated machine. All binaries were statically-linked.

### 1.4.2 Simulators

The majority of the results in this dissertation come from execution-driven simulation of userlevel code (system calls are executed on the host machine). Two different simulators were useda functional simulator and a timing simulator. All characterization data were gathered using functional simulation of benchmarks executing to completion. Performance data (and other associated results) were obtained using a detailed, parameterized microarchitectural timing model. The parameters varied among experiments; important features of the microarchitecture common to all of the experiments are discussed in the next section. The significant slowdown of the timing simulator versus native execution prohibited simulation of the benchmarks to their completion under the timing simulator (a complete timing simulation of apsi, for example, runs for more than a month). Instead, the first four billion instructions of each benchmark were simulated.

#### 1.4.3 Model architecture and microarchitecture

The benchmarks are compiled to an Alpha instruction-set architecture (ISA) target [5]. The Alpha ISA is a sequential, register-based, load-store ISA. Thirty-two each integer and floating-point registers are defined; one of each kind always contains zero. Excepting loads and stores, all instructions operate exclusively on register values. Most instructions have one or two inputs, although conditional move instructions are provided, which effectively have three inputs. Instructions have a maximum of one output.

Where timing simulation is required, a pipelined, out-of-order superscalar microarchitecture with MIPS R10K-style register renaming is assumed [89]. Instructions are scheduled dynamically—subject to resource constraints—from an instruction window as soon as their input operands are available. Multi-cycle execution resources are assumed to be fully-pipelined, and the execution of a dependent operation may begin in the cycle immediately following the completion of its parent.

Loads may issue before older store addresses are completely known and assume both a cache hit and no unknown memory dependence to an older store [72]. A cache miss results in the need to re-issue all operations issued after the load through the signalling of the miss. Loads may bypass their data from older executed, unretired stores with the same latency as a cache hit. A conflicting older store executing after a load results in a pipeline squash and refetch of all operations beginning with the load. A load-dependence predictor is used to delay the issuing of loads that have previously caused such squashes [90]. Instruction sequencing uses separate conditional and indirect branch predictors and a return address stack. Execution proceeds down a wrong-path until the mispredicted control instruction is executed; fetch begins along the correct path in the cycle immediately following the execution of a misprediction; more generally, any pipeline squash completes in a single cycle and fetch resumes the following cycle. There is no limit to the number of outstanding, unresolved branches. The performance of most Alpha implementations are sensitive to code layout with respect to branches and their targets [6]. For this reason, the compilers insert many NOPs. These NOPs are eliminated during instruction fetch—they have no effect other than occupying cache space.

The memory hierarchy consists of three caches and a fixed-latency, infinite memory. Separate L1 instruction caches and data caches are backed by a unified L2 cache. The L1 data cache and the L2 cache are writeback caches. The memory system supports multiple outstanding misses at each level; each level also contains an opportunistic stride-based prefetcher. Data and instruction TLBs are perfect (i.e., not modeled).

### **1.5 Dissertation Outline**

The next four chapters of the dissertation each present a primary contribution in the order described in Section 1.3. Chapter 2 presents an in-depth characterization of degree of use properties. Degree of use prediction is described in Chapter 3. Both static and dynamic prediction methods are presented; the formulation of the degree of use dataflow problem appears in connection with the static prediction. Chapter 4 presents useless instruction elimination. The incidence and causes of useless instructions are investigated, followed by a description and experimental evaluation of the UIE technique. Use-based register caching is the topic of Chapter 5. The proposed register cache organization is motivated by considering the bypass network the primary value communication mechanism in lieu of the register file. Managing the register cache contents using degree of use information is demonstrated to be superior to previously proposed techniques. Chapter 6 summarizes the contributions detailed in the prior chapters of the dissertation; it also discusses possible additional applications of degree of use information and issues with such optimizations in general. References and the appendix make up the remainder of the document.

# **Chapter 2**

# **Characterizing Value Degree of Use**

This chapter presents a detailed characterization of inter-instruction communication through registers in terms of degree of use. The data presented here serve three functions: (1) to illuminate the inter-instruction communication patterns that occur in programs, (2) to suggest opportunities for communication optimizations, and (3) to demonstrate the feasibility of degree of use prediction.

First, aggregate degree of use properties are presented. Values generated during a program's execution are classified by their degree of use, and the types of communication that are revealed are discussed. In some cases, the role of a value in the operation of the program can be identified by the type of instruction that generates the value or the architectural register to which the value is assigned. With this additional data, values with specific roles in a program are shown to have degree of use characteristics significantly different than the overall average. Next, the stability of the communication is explored on a per-instruction basis. Stable inter-instruction communication suggests that degree of use prediction, the topic of the next chapter, will be successful. Finally, mathematical models for degree of use characteristics are developed, extending some prior work in this area. The results of this analysis allow for both the calculation of the probability of occurrence of a particular degree of use and the estimation of the mean degree of use from the expected instruction mix.

### 2.1 Degree of Use Characteristics

Figure 2.1 shows data on the observed degree of use distribution for each of the benchmarks compiled under two different compiler suites: the vendor suite (offered by the same company responsible for the instruction set architecture) and the third-party suite. Details on the specific compilers in each suite and the compilation methodology can be found in section A.2 of the appendix.

It is readily apparent that most of the communication occurring during program execution is direct communication to one consumer: an average of over 67% of dynamic values have a degree of use of one. The frequency of degree of use two values show the most absolute variation, accounting for anywhere between 4% and 33% of all values. No higher degree of use accounts for more than 11% of the values in any of the benchmarks. 4-5% of the values generated by most of the integer benchmarks are not used at all.

Comparing Figure 2.1(a) and Figure 2.1(b), it is apparent that the degree of use behavior of a given program is quite similar even when different compilers are used, especially for the C and C++ benchmarks. This should not be surprising since the overall value communication structure is a function of the ISA and the program itself. The only immediately obvious difference is a trade-off between one- and two-use values: the vendor compilers tend to generate more of the former and less of the latter while the third-party compilers do the opposite. The third-party compilers also generate fewer degree of use zero instructions. These minute differences arise from how each compiler performs register allocation, code scheduling, and other optimizations that affect how registers are mapped onto the inherent dataflow specified by the program.

#### 2.1.1 Mean, median, mode, and maximum

The median and mode degrees of use are easily observed on each distribution of Figure 2.1 (the bin crossed by the 50% level and the largest bin, respectively). Without exception, the median and mode degree of use are one. The mean degree of use for each benchmark appears in Table 2.1 along with the maximum degree of use and the percentage of non-nop instructions that produce a register result. An average of about 76% of dynamic instructions produce a value; the remainder are almost entirely stores and branches, although a few rare instructions (e.g., certain system).

|              | Vendor Compiler Suite |         |           | Third-party Compiler Suite |        |       |

|--------------|-----------------------|---------|-----------|----------------------------|--------|-------|

| Benchmark    | Mean                  | Maximum | % Dynamic | Mean Maximum % Dyna        |        |       |

| eon          | 1.94                  | 8.46 K  | 63.7%     | 2.06                       | 8.49 K | 62.4% |

| bzip2        | 1.76                  | 336 M   | 76.6%     | 1.74                       | 67.5 M | 81.1% |

| crafty       | 1.53                  | 5.40 M  | 82.8%     | 1.54                       | 2.34 M | 76.5% |

| gap          | 1.53                  | 3.21 M  | 76.0%     | 1.59                       | 11.6 M | 72.7% |

| gcc          | 1.70                  | 2.68 M  | 69.7%     | 1.73                       | 421 K  | 62.5% |

| gzip         | 1.58                  | 828 K   | 76.2%     | 1.52                       | 4.19 M | 78.0% |

| mcf          | 1.51                  | 34.0 M  | 67.5%     | 1.71                       | 33.8 M | 70.4% |

| parser       | 1.76                  | 13.8 M  | 74.2%     | 1.73                       | 3.26 M | 71.4% |

| perl         | 1.68                  | 579 K   | 71.0%     | 1.67                       | 122 K  | 67.4% |

| twolf        | 1.68                  | 69.3 K  | 70.8%     | 1.78                       | 44.1 K | 72.9% |

| vortex       | 1.54                  | 6.98 M  | 71.4%     | 1.61                       | 86.7 K | 66.1% |

| vpr          | 1.72                  | 28.5 M  | 71.7%     | 1.63                       | 864 K  | 77.9% |

| ammp         | 1.88                  | 205 M   | 81.8%     | 1.78                       | 86.6 M | 82.9% |

| art          | 1.96                  | 250 K   | 67.3%     | 1.69                       | 57.1 M | 81.5% |

| equake       | 1.56                  | 7.66 M  | 92.1%     | 1.58                       | 3.57 M | 86.6% |

| mesa         | 1.72                  | 1.31 M  | 74.9%     | 1.66                       | 1.31 M | 74.2% |

| applu        | 1.91                  | 1.67 M  | 86.1%     | 1.78                       | 2.08 M | 65.7% |

| apsi         | 1.92                  | 6.25 M  | 80.9%     | 1.85                       | 2.50 M | 78.2% |

| mgrid        | 1.74                  | 344 K   | 91.9%     | 1.59                       | 3.44 M | 80.8% |

| sixtrack     | 1.91                  | 16.3 M  | 88.3%     | 1.99                       | 5.64 M | 73.9% |

| swim         | 1.85                  | 863 K   | 82.8%     | 1.63                       | 967 K  | 74.2% |

| wupwise      | 1.73                  | 2.89 M  | 79.1%     | 1.78                       | 9.22 M | 67.3% |

| facerec      | 1.85                  | 11.3 M  | 82.2%     | 1.79                       | 2.96 M | 78.4% |

| fma3d        | 1.90                  | 80.3 K  | 77.9%     | 1.80                       | 41.8 K | 79.9% |

| galgel       | 1.85                  | 2.99 M  | 75.9%     | 1.75                       | 6.73 M | 78.8% |

| lucas        | 1.83                  | 51.5 K  | 90.4%     | 1.80                       | 24.9 M | 75.9% |

| Integer      | 1.66                  | 336 M   | 72.6%     | 1.69                       | 67.5 M | 71.6% |

| Floating Pt. | 1.83                  | 205 M   | 82.3%     | 1.75                       | 86.6 M | 77.0% |

| C/C++        | 1.69                  | 336 M   | 74.2%     | 1.69                       | 86.6 M | 74.0% |

| Fortran      | 1.85                  | 16.3 M  | 83.6%     | 1.78                       | 24.9 M | 75.3% |

| All          | 1.75                  | 336 M   | 77.8%     | 1.72                       | 67.5 M | 74.5% |

Table 2.1: Degree of Use Characteristics

calls) do not produce results either. Note that the average degree of use differs very little between the different compiler suites.

While the relative fraction of values with a high degree of use is very small, the data in Table 2.1 show that degrees of use themselves can be large. Maximum degrees of use range over five orders of magnitude from a few thousand to over three hundred million (a global pointer value in bzip2) across the different benchmarks. Instructions exhibiting the largest degrees of use fall into two overlapping categories: (1) address-generating instructions (often stack and global pointer updates), and (2) instructions generating loop-invariants. In the first case, the number of unique static consumer instructions tends to be high, while in the second case the high degree of use frequently results from repeated communication to a set of static consumers.

This relationship between the number of unique consumer instructions and the average degree of use appears in Figure 2.2 for static instructions generating a significant number of values.<sup>†</sup> The diagonal line corresponds to an average degree of use equal to the number of static consumers. Points above this line represent instructions that generate values used within loops: the average

<sup>&</sup>lt;sup>†</sup> Only static instructions generating more than 1000 values are represented. The data in the figure corresponds to benchmarks compiled with the vendor compilers; data from the benchmarks compiled with the other compilers appears nearly identical.

number of uses of such a value exceeds the number of unique consumer instructions. A typical example of such an instruction is one that generates the base address of an array accessed in the loop body. Conversely, points below the line represent instructions generating values with a smaller average degree of use than the number of potential consumer instructions. For these instructions, variation in the subsequent control flow results in different consumers receiving the result of the instructions on different executions. Note that some of these consumers may still receive one of these values multiple times due to looping. A representative example of an instruction in this region is an indirect subroutine call, which has as its result the return address: many return instructions in different subroutines will use the result of the call, but the average degree of use will be only one.

#### 2.1.2 Degree of use of input values

The average degree of use of instruction inputs is higher than the average degree of use of instruction results. To understand this phenomenon, consider a single value used ten times. The degree of use of the value is ten and that value would be counted once in the distributions of Figure 2.1. However, that value accounts for *ten* instruction inputs: while only one instruction generates a result with a degree of use of ten, ten instructions *use* a degree-of-use-ten value as an input. In other words, the frequency of occurrence of a particular degree of use as an input is its frequency as a result weighted by the degree of use itself.

Therefore, the distribution of the degree of use of instruction inputs may be obtained from the distribution in Figure 2.1(a) by doubling the height of the degree of use two bar, tripling the height of the degree of use three bar, and so on, and then renormalizing. The resulting distribution is portrayed in Figure 2.3 (for benchmarks compiled with the vendor compilers). Note that while an instruction is most likely to *generate* a value that is used once, an instruction will most likely *use* a value that is used more than once. Values with seven or more uses account for nearly a quarter of all values used even though they comprise less than 3% of all values (see Figure 2.1(a)). As would be expected, degree of use zero values account for no inputs.

Another way to think about distributions of Figure 2.3 is as the relative contribution that values with a particular degree of use make to the average degree of use. Consider how the mean degree of use is calculated: each degree of use is multiplied by its frequency of occurrence to

obtain its contribution to the mean (an exercise that will be demonstrated more explicitly in Section 2.5). This procedure is exactly that used to generate the distribution of input degrees of use (except for the final renormalization). Figure 2.3 shows that while single-use values comprise the majority (just over two-thirds) of all values generated, they contribute less than 40% to the overall mean degree of use.

# 2.2 Classifying Values

The degree of use of a value is intimately tied to the role of that value in the execution of a program. Therefore, one expects to see different degree of use properties for different classes of values. In this section, two proxies for the role of a value in a program are considered: the type of instruction that generates the value and the architectural register to which the value is assigned.

### 2.2.1 Classification by instruction type

Table 2.2 shows degree of use data for six classes of instructions. In addition to the average degree of use, the table shows the average number of unique static consumers for that class of

20

instruction. The categories in the table represent about 80% of dynamic instructions, including the largest five (control instructions were among the smallest classes of value-generating instructions). The categories listed were chosen based on whether the degree of use data were noteworthy or could be explained by considering the role of those types of instructions within a program.

Load instructions exhibit a larger than average number of static consumers although their degree of use is about equal to the overall average. Further partitioning the loads by the size of the memory access reveals that 64-bit integer loads average over six distinct consumers, while the remaining loads average less than two. In spite of this distinction, the average degree of use of 64-bit loads is only 13% higher than that of other types. Due to the variety of roles for loads in a program, it is difficult to draw any conclusions from these characteristics, although one might speculate that the behavior of the 64-bit loads is correlated with the fact that addresses are 64 bits.

The data in the table indicate a significant difference in the behavior of the results of integer and floating-point math operations. These categories include add, subtract, multiply, divide, and square root instructions of all data sizes but exclude scaled adds, shifts, conversions, and other logical operations, which showed somewhat different behavior. The data show that integer values are used more often than floating-point values; besides their role in computation, integer values perform other functions that are likely to result in many uses of the same value. For example, some integer variables are loop induction variables or containers of multiple smaller-sized data items (e.g., packed bytes or bitmasks). Variation in control flow causes the number of potential consumers to exceed the average number of uses for integer results; floating-point operations typically communicate to a fixed set of consumers.

The lda or load address instruction exhibited the highest average degree of use of any common instruction. lda places the result of an effective address calculation into a register where it often is used as a base address for many loads or stores, accounting for both the high average degree of use and number of unique consumer instructions. Those lda instructions that did not take a register input were classified instead as load immediates, which exhibit very different behavior.

The results of compare instructions have a very well-defined role—determining the direction of a subsequent conditional branch. These values are almost always used just once by a subsequent branch. Occasionally, a branch condition will be computed by a compare instruction prior

|              | Vendor Compiler Suite  |                   |                | Third-party Compiler Suite |                   |                |

|--------------|------------------------|-------------------|----------------|----------------------------|-------------------|----------------|

| Group        | % dynamic instructions | Average consumers | Average<br>DOU | % dynamic instructions     | Average consumers | Average<br>DOU |

| Load         | 30.3%                  | 3.73              | 1.71           | 31.0%                      | 3.71              | 1.67           |

| FP math      | 22.1%                  | 1.46              | 1.34           | 18.3%                      | 2.00              | 1.70           |

| Integer math | 11.0%                  | 2.61              | 1.74           | 13.2%                      | 2.84              | 1.77           |

| Load address | 9.6%                   | 11.42             | 4.90           | 8.6%                       | 16.47             | 6.00           |

| Compare      | 5.0%                   | 1.14              | 1.04           | 6.2%                       | 1.15              | 1.01           |

| Control      | 1.1%                   | 3.12              | 1.18           | 1.0%                       | 2.93              | 1.08           |

Table 2.2: Degree of Use Properties of Instruction Groups

to one or more different branches, resulting in more than one possible consumer for the computed condition. This phenomenon accounts for the number of potential consumers exceeding one.

Finally, control instructions (those that generate values) supply many different consumers, but their average degree of use is much lower than that of the load address instructions. This category is almost entirely composed of subroutine call instructions, each of which generates a return address used by one of many potential consumers. Indirect calls (jsr), comprising about 10% of this category, have an average of 75 consumers, while the more common direct calls (bsr) supply an average of only 1.3 consumers.

# 2.2.2 Classification by register type

Guessing the role of a value using only the nature of its source instruction is difficult. Loads, for example, perform too many different functions in a program to hint at the purpose of the loaded value. A better clue to the role of a value is the identity of the architectural register containing that value. Many registers or groups of registers have functions designated by convention to allow different software components (e.g., compilers, assemblers, and libraries) to cooperate. The functions of these registers should correlate with the degree of use properties of the values assigned to them. The stack pointer is perhaps the most obvious example: within a function body, accesses to local variables stored in the stack frame use the stack pointer as a base register. Thus, one expects values in this register to exhibit a high average degree of use, which is the case.

Table 2.3 shows the average degree of use for several classes of registers (as defined by the Alpha Assembly Language Programmers Guide [6]). Data are shown for benchmarks compiled with the vendor compilers only; the other compiler suite exhibits comparable behavior.