# WYSINWYX: What You See Is Not What You eXecute

GOGUL BALAKRISHNAN

NEC Laboratories America, Inc.

and

THOMAS REPS

University of Wisconsin and GrammaTech, Inc.

Over the last seven years, we have developed static-analysis methods to recover a good approximation to the variables and dynamically-allocated memory objects of a stripped executable, and to track the flow of values through them. The paper presents the algorithms that we developed, explains how they are used to recover intermediate representations (IRs) from executables that are similar to the IRs that would be available if one started from source code, and describes their application in the context of program understanding and automated bug hunting.

Unlike algorithms for analyzing executables that existed prior to our work, the ones presented in this paper provide useful information about memory accesses, even in the absence of debugging information. The ideas described in the paper are incorporated in a tool for analyzing Intel x86 executables, called CodeSurfer/x86. CodeSurfer/x86 builds a system dependence graph for the program, and provides a GUI for exploring the graph by (i) navigating its edges, and (ii) invoking operations, such as forward slicing, backward slicing, and chopping, to discover how parts of the program can impact other parts.

To assess the usefulness of the IRs recovered by CodeSurfer/x86 in the context of automated bug hunting, we built a tool on top of CodeSurfer/x86, called Device-Driver Analyzer for x86 (DDA/x86), which analyzes device-driver executables for bugs. Without the benefit of either source code or symbol-table/debugging information, DDA/x86 was able to find known bugs (that had been discovered previously by source-code-analysis tools), along with useful error traces, while having a low false-positive rate. DDA/x86 is the first known application of program analysis/verification techniques to industrial executables.

Categories and Subject Descriptors: D.2.4 [Software Engineering]: Software/Program Verifi-

Authors' addresses: G. Balakrishnan, NEC Laboratories America, Inc., 4 Independence Way, Princeton, NJ 08540; bgogul@nec-labs.com. T. Reps, Computer Sciences Dept., Univ. of Wisconsin, 1210 W. Dayton St., Madison, WI 53703, and GrammaTech, Inc., 317 N. Aurora St., Ithaca, NY 14850; reps@cs.wisc.edu. At the time the research reported in the paper was carried out, G. Balakrishnan was affiliated with the University of Wisconsin.

The work was supported in part by ONR under grants N00014-01-1-{0796, 0708}, by NSF under grants CCR-9986308 and CCF-{0540955, 0524051}, by HSARPA under AFRL contract FA8750-05-C-0179, and by AFRL under contract FA8750-06-C-0249.

T. Reps has an ownership interest in GrammaTech, Inc., which has licensed elements of the technology reported in this publication.

Portions of the work appeared in the 13th, 14th, and 17th Int. Confs. on Compiler Construction [Balakrishnan and Reps 2004; Balakrishnan et al. 2005; Reps and Balakrishnan 2008], the 17th Int. Conf. on Computer Aided Verification [Balakrishnan et al. 2005], the 3rd Asian Symp. on Prog. Langs. and Systems [Reps et al. 2005], the 2006 Workshop on Part. Eval. and Semantics-based Prog. Manip. [Reps et al. 2006], the 13th Int. Static Analysis Symp. [Balakrishnan and Reps 2006], the 8th Int. Conf. on Verif., Model Checking, and Abs. Interp. [Balakrishnan and Reps 2007], and the 14th Int. Conf. on Tools and Algs. for the Const. and Analysis of Systems [Balakrishnan and Reps 2008], as well as in G. Balakrishnan's Ph.D. dissertation [Balakrishnan 2007].

© 2009 G. Balakrishnan and T. Reps

## 2 · G. Balakrishnan and T. Reps

cation—Assertion checkers; model checking; D.2.5 [Software Engineering]: Testing and Debugging—Symbolic execution; D.2.7 [Software Engineering]: Distribution, Maintenance, and Enhancement—Restructuring, reverse engineering, and reengineering; D.3.2 [Programming Languages]: Language Classifications—Macro and assembly languages; D.4.6 [Operating Systems]: Security and Protection—Invasive software; E.1 [Data]: Data Structures—arrays; lists, stacks, and queues; records; F.3.2 [Logics and Meanings of Programs]: Semantics of Programming Languages—Program analysis

General Terms: Algorithms, Security, Theory, Verification

Additional Key Words and Phrases: Abstract interpretation, context-sensitive analysis, data-structure recovery, interprocedural dataflow analysis, pointer analysis, reverse engineering, static analysis

#### 1. INTRODUCTION

Recent research in programming languages, software engineering, and computer security has led to new kinds of tools for analyzing programs for bugs and security vulnerabilities [Havelund and Pressburger 2000; Wagner et al. 2000; Engler et al. 2000; Corbett et al. 2000; Bush et al. 2000; Ball and Rajamani 2001; Chen and Wagner 2002; Henzinger et al. 2002; Das et al. 2002]. In these tools, static analysis is used to determine a conservative answer to the question "Can the program reach a bad state?" Some of this work has already been transitioned to commercial products for source-code analysis (see [Ball et al. 2006], [Coverity], and [CodeSonar]).

However, these tools all focus on analyzing source code written in a high-level language. Unfortunately, most programs that an individual user will install on his computer, and many commercial off-the-shelf (COTS) programs that a company will purchase, are delivered as stripped machine code (i.e., neither source code nor symbol-table/debugging information is available). If an individual or company wishes to vet such programs for bugs, security vulnerabilities, or malicious code (e.g., back doors, time bombs, or logic bombs) the availability of good source-code-analysis products is irrelevant.

Less widely recognized is that even when the original source code is available, source-code analysis has certain drawbacks [Howard 2002; WHDC 2007]. The reason is that computers do not execute source code; they execute machine-code programs that are generated from source code. The transformation from source code to machine code can introduce subtle but important differences between what a programmer intended and what is actually executed by the processor. For instance, the following compiler-induced vulnerability was discovered during the Windows security push in 2002 [Howard 2002]: the Microsoft C++ .NET compiler reasoned that because the program fragment shown below on the left never uses the values written by memset (intended to scrub the buffer pointed to by password), the

<sup>&</sup>lt;sup>1</sup>Static analysis provides a way to obtain information about the possible states that a program reaches during execution, but without actually running the program on specific inputs. Static-analysis techniques explore the program's behavior for *all* possible inputs and *all* possible states that the program can reach. To make this feasible, the program is "run in the aggregate"—i.e., on descriptors that represent *collections* of memory configurations [Cousot and Cousot 1977].

memset call could be removed—thereby leaving sensitive information exposed in the freelist at runtime.

```

\begin{array}{lll} \texttt{memset(password, '\0', len);} & \Longrightarrow & \texttt{free(password);} \end{array}

```

Such a vulnerability is invisible in the original source code; it can only be detected by examining the low-level code emitted by the optimizing compiler. We call this the WYSINWYX phenomenon (pronounced "wiz-in-wicks"): What You See [in source code] Is Not What You eXecute [Reps et al. 2005; Balakrishnan et al. 2007; Balakrishnan 2007].

WYSINWYX is not restricted to the presence or absence of procedure calls; on the contrary, it is pervasive. Some of the reasons why analyses based on source code can provide the wrong level of detail include

- —Many security exploits depend on platform-specific details that exist because of features and idiosyncrasies of compilers and optimizers. These include memory-layout details (such as the positions—i.e., offsets—of variables in the runtime stack's activation records and the padding between structure fields), register usage, execution order (e.g., of actual parameters at a call), optimizations performed, and artifacts of compiler bugs. Bugs and security vulnerabilities can escape notice when a tool is unable to take into account such fine-grained details.

- —Analyses based on source code<sup>2</sup> typically make (unchecked) assumptions, e.g., that the program is ANSI C compliant. This often means that an analysis does not account for behaviors that are allowed by the compiler and that can lead to bugs or security vulnerabilities (e.g., arithmetic is performed on pointers that are subsequently used for indirect function calls; pointers move off the ends of arrays and are subsequently dereferenced; etc.)

- —Programs are sometimes modified subsequent to compilation, e.g., to perform optimizations or insert instrumentation code [Wall 1992]. They may also be modified to insert malicious code. Such modifications are not visible to tools that analyze source code.

In short, even when source code is available, a substantial amount of information is hidden from source-code-analysis tools, which can cause bugs, security vulnerabilities, and malicious behavior to be invisible to such tools.

The alternative is to perform static analysis at the machine-code level. The advantage of this approach is that the machine code contains the actual instructions that will be executed; this addresses the WYSINWYX phenomenon because it provides information that reveals the actual behavior that arises during program execution.

Although having to perform static analysis on machine code represents a daunting challenge, there is also a possible silver lining: by analyzing an artifact that is closer to what is actually executed, a static-analysis tool may be able to obtain a more accurate picture of a program's properties. The reason is that—to varying degrees—the semantic definition of every programming language leaves certain details unspecified. Consequently, for a source-code analyzer to be sound, it must

$<sup>^2</sup>$ Terms like "analyses based on source code" and "source-code analyses" are used as a shorthand for "analyses that work on intermediate representations (IRs) built from source code."

# 4 . G. Balakrishnan and T. Reps

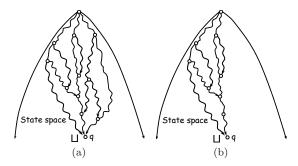

Fig. 1. Source-code analysis, which must account for all possible choices made by the compiler, must summarize more paths (see (a)) than machine-code analysis (see (b)). Because the latter can focus on fewer paths, it can yield more precise results.

account for all possible implementations, whereas a machine-code analyzer only has to deal with one possible implementation—namely, the one for the code sequence chosen by the compiler.

For instance, in C and C++ the order in which actual parameters are evaluated is not specified: actuals may be evaluated left-to-right, right-to-left, or in some other order; a compiler could even use different evaluation orders for different functions. Different evaluation orders can give rise to different behaviors when actual parameters are expressions that contain side effects. For a source-level analysis to be sound, at each call site it must take the join ( $\sqcup$ ) of the results from analyzing each permutation of the actuals.<sup>3</sup> In contrast, an analysis of an executable only needs to analyze the particular sequence of instructions that lead up to the call.

Static-analysis tools are always fighting imprecision introduced by the join operation. One of the dangers of static-analysis tools is that loss of precision by the analyzer can lead to the user being swamped with a huge number of reports of potential errors, most of which are false positives. As illustrated in Fig. 1, because a source-code-analysis tool summarizes more behaviors than a tool that analyzes machine code, the join performed at q must cover more abstract states. This can lead to less-precise information than that obtained from machine-code analysis. Because more-precise answers mean a lower false-positive rate, machine-code-analysis tools have the potential to report fewer false positives.

There are other trade-offs between performing analysis at source level versus the machine-code level: with source-code analysis one can hope to learn about bugs and vulnerabilities that exist on multiple platforms, whereas analysis of the machine code only provides information about vulnerabilities on the specific platform on which the executable runs.

Although it is possible to create source-code tools that strive to have greater fidelity to the program that is actually executed—examples include [Chandra and Reps 1999; Nita et al. 2008]—in the limit, the tool would have to incorporate all the platform-specific decisions that would be made by the compiler. Because such

<sup>&</sup>lt;sup>3</sup>We follow the conventions of abstract interpretation [Cousot and Cousot 1977], where the lattice of properties is oriented so that the confluence operation used where paths come together is join ( $\sqcup$ ). In dataflow analysis, the lattice is often oriented so that the confluence operation is meet

$<sup>(\</sup>sqcap)$ . The two formulations are duals of one another.

decisions depend on the level of optimization chosen, to build these choices into a tool that works on a representation that is close to the source level would require simulating much of the compiler and optimizer inside the analysis tool. Such an approach is impractical.

In addition to addressing the WYSINWYX issue, performing analysis at the machine-code level provides a number of other benefits:

- —Programs typically make extensive use of libraries, including dynamically linked libraries (DLLs), which may not be available as source code. Typically, source-code analyses are performed using code stubs that model the effects of library calls. Because these are created by hand, they may contain errors, which can cause an analysis to return incorrect results. In contrast, a machine-code-analysis tool can analyze the library code directly [Gopan and Reps 2007].

- —The source code may have been written in more than one language. This complicates the life of designers of tools that analyze source code because multiple languages must be supported, each with its own quirks.

- —Even if the source code is primarily written in one high-level language, it may contain inlined assembly code in selected places. Source-code-analysis tools typically either skip over inlined assembly [CodeSurfer] or do not push the analysis beyond sites of inlined assembly [PREfast 2004]. To a machine-code-analysis tool, inlined assembly just amounts to additional instructions to analyze.

- —Source-code-analysis tools are only applicable when source is available, which limits their usefulness in security applications (e.g., to analyzing code from open-source projects).

Research carried out during the last decade by our research group [Xu et al. 2000; 2001; Balakrishnan and Reps 2004; Reps et al. 2005; Reps et al. 2006; Balakrishnan and Reps 2006; 2007; Gopan and Reps 2007; Balakrishnan 2007; Lim and Reps 2008; Balakrishnan and Reps 2008] as well as by others [Larus and Schnarr 1995; Cifuentes and Fraboulet 1997b; Debray et al. 1998; Bergeron et al. 1999; Amme et al. 2000; De Sutter et al. 2000; Bergeron et al. 2001; Kiss et al. 2003; Debray et al. 2004; Backes 2004; Regehr et al. 2005; Guo et al. 2005; Christodorescu et al. 2005; Kruegel et al. 2005; Cova et al. 2006; Chang et al. 2006; Brumley and Newsome 2006; Emmerik 2007; Zhang et al. 2007] has developed the foundations for performing static analysis at the machine-code level. The machine-code-analysis problem comes in two versions: (i) with symbol-table/debugging information (unstripped executables), and (ii) without symbol-table/debugging information (stripped executables). Many tools address both versions of the problem, but are severely hampered when symbol-table/debugging information is absent.

In 2004, we supplied a key missing piece, particularly for analysis of stripped executables [Balakrishnan and Reps 2004]. Previous to that work, static-analysis tools for machine code had rather limited abilities: it was known how to (i) track values in registers and, in some cases, the stack frame [Larus and Schnarr 1995], and (ii) analyze control flow (sometimes by applying local heuristics to try to resolve indirect calls and indirect jumps, but otherwise ignoring them).

The work presented in [Balakrishnan and Reps 2004] provided a way to apply the tools of abstract interpretation [Cousot and Cousot 1977] to the problem of analyzing stripped executables, and we followed this up with other techniques to complement and enhance the approach [Reps et al. 2005; Lal et al. 2005; Reps et al. 2006; Balakrishnan and Reps 2006; 2007; Balakrishnan 2007; Balakrishnan and Reps 2008]. This body of work has resulted in a method to recover a good approximation to an executable's variables and dynamically allocated memory objects, and to track the flow of values through them. These methods are incorporated in a tool called CodeSurfer/x86 [Balakrishnan et al. 2005].

CodeSurfer/x86: A Platform for Recovering IRs from Stripped Executables. Given a stripped executable as input, CodeSurfer/x86 [Balakrishnan et al. 2005] recovers IRs that are similar to those that would be available had one started from source code. The recovered IRs include control-flow graphs (CFGs), with indirect jumps resolved; a call graph, with indirect calls resolved; information about the program's variables; possible values for scalar, array, and pointer variables; sets of used, killed, and possibly-killed variables for each CFG node; and data dependences. The techniques employed by CodeSurfer/x86 do not rely on debugging information being present, but can use available debugging information (e.g., Windows .pdb files) if directed to do so.

The analyses used in CodeSurfer/x86 are a great deal more ambitious than even relatively sophisticated disassemblers, such as IDAPro [IDAPro]. At the technical level, they address the following problem:

Given a (possibly stripped) executable E, identify the procedures, data objects, types, and libraries that it uses, and,

—for each instruction I in E and its libraries,

—for each interprocedural calling context of I, and

—for each machine register and variable V in scope at I,

statically compute an accurate over-approximation to the set of values that V may contain when I executes.

It is useful to contrast this approach against the approach used in much of the other work that now exists on analyzing executables. Many research projects have focused on specialized analyses to identify aliasing relationships [Debray et al. 1998], data dependences [Amme et al. 2000; Cifuentes and Fraboulet 1997b], targets of indirect calls [De Sutter et al. 2000], values of strings [Christodorescu et al. 2005], bounds on stack height [Regehr et al. 2005], and values of parameters and return values [Zhang et al. 2007]. In contrast, CodeSurfer/x86 addresses all of these problems by means of a set of analyses that focuses on the problem stated above. In particular, CodeSurfer/x86 discovers an over-approximation of the set of states that can be reached at each point in the executable—where a state means all of the state: values of registers, flags, and the contents of memory—and thereby provides information about aliasing relationships, targets of indirect calls, etc.

One of the goals of CodeSurfer/x86 is to be able to detect whether an executable conforms to a standard compilation model. By "standard compilation model" we mean that the executable has procedures, activation records (ARs), a global data region, and a free-storage pool; might use virtual functions and DLLs; maintains a runtime stack; each global variable resides at a fixed offset in memory; each local variable of a procedure f resides at a fixed offset in the ARs for f; actual

parameters of f are pushed onto the stack by the caller so that the corresponding formal parameters reside at fixed offsets in the ARs for f; the program's instructions occupy a fixed area of memory, and are not self-modifying.

During the analysis performed by CodeSurfer/x86, these aspects of the program are checked. When violations are detected, an error report is issued, and the analvsis proceeds. In doing so, however, we generally choose to have the analyzer only explore behaviors that stay within those of the desired execution model. For instance, if the analysis finds that the return address might be modified within a procedure, it reports the potential violation, but proceeds without modifying the control flow of the program. Consequently, if the executable conforms to the standard compilation model, CodeSurfer/x86 creates a valid IR for it; if the executable does not conform to the model, then one or more violations will be discovered, and corresponding error reports will be issued; if the (human) analyst can determine that the error report is indeed a false positive, then the IR is valid. The advantages of this approach are (i) it provides the ability to analyze some aspects of programs that may deviate from the desired execution model; (ii) it generates reports of possible deviations from the desired execution model; (iii) it does not force the analyzer to explore all of the consequences of each (apparent) deviation, which may be a false positive due to loss of precision that occurs during static analysis.

Organization. The remainder of the paper is organized as follows:  $\S 2$  presents the abstract memory model used in CodeSurfer/x86, and an algorithm to recover variable-like entities, referred to as a-locs (for abstract locations), from an executable.  $\S 3$  presents an abstract-interpretation-based algorithm, referred to as value-set analysis (VSA), to recover information about the contents of machine registers and memory locations at every program point in an executable.  $\S 4$  presents an improved a-loc recovery algorithm.  $\S 5$  describes how the various algorithms used in CodeSurfer/x86 interact with each other.  $\S 6$  presents Device-Driver Analyzer for x86 (DDA/x86)—a tool built on top of CodeSurfer/x86 to analyze device-driver executables for bugs—and presents a case study in which DDA/x86 was used to find bugs in Windows device drivers.  $\S 7$  discusses related work.

# 2. AN ABSTRACT MEMORY MODEL

One of the major stumbling blocks in analyzing executables is the difficulty of recovering information about variables and types, especially for aggregates (i.e., structures and arrays). Consider, for instance, a data dependence from statement a to statement b that is transmitted by write/read accesses on some variable x. When performing source-code analysis, the programmer-defined variables provide us with convenient compartments for tracking such data manipulations. A dependence analyzer must show that a defines x, b uses x, and there is an x-def-free path from a to b. However, in executables, memory is accessed either directly—by specifying an absolute address—or indirectly—through an address expression of the form "[base + index × scale + offset]", where base and index are registers, and scale and offset are integer constants. It is not clear from such expressions what the natural compartments are that should be used for analysis. Because executables do not have intrinsic entities that can be used for analysis (analogous to source-level variables), a crucial step in the analysis of executables is to identify variable-like

entities.

If debugging information is available (and trusted), this provides one possibility; however, even if debugging information is available, analysis techniques have to account for bit-level, byte-level, word-level, and bulk-memory manipulations performed by programmers (or introduced by the compiler) that can sometimes violate variable boundaries [Backes 2004; Miné 2006; Reps et al. 2006]. If a program is suspected of containing malicious code, even if debugging information is present, it cannot be entirely relied upon. For these reasons, it is not always desirable to use debugging information—or at least to rely on it alone—for identifying a program's data objects. (Similarly, past work on source-code analysis has shown that it is sometimes valuable to ignore information available in declarations and infer replacement information from the actual usage patterns found in the code [Eidorff et al. 1999; O'Callahan and Jackson 1997; Ramalingam et al. 1999; Siff and Reps 1996; van Deursen and Moonen 1998].)

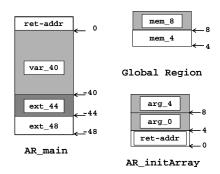

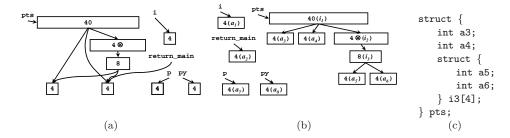

EXAMPLE 2.1. The two programs shown in Fig. 2 will be used in this section to illustrate the issues involved in recovering a suitable set of variable-like entities from a machine-code program. The C program shown in Fig. 2(a) initializes all elements of array pts[5] and returns pts[0].y. The x-members of each element are initialized with the value of the global variable a and the y-members are initialized with the value of global variable b. The initial values of the global variables a and b are 1 and 2, respectively.

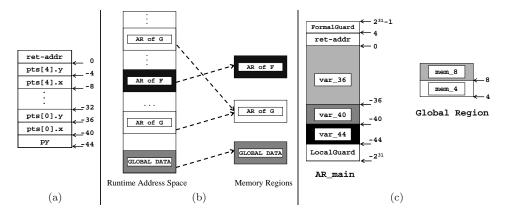

Fig. 2(b) shows the corresponding x86 program (in Intel assembly-language syntax). By convention, esp is the stack pointer in the x86 architecture. Instruction 1 allocates space for the locals of main on the stack. Fig. 3(a) shows how the variables are laid out in the activation record of main. Note that there is no space for variable i in the activation record because the compiler promoted i to register edx. Similarly, there is no space for pointer p because the compiler promoted it to register eax.

Instructions L1 through 12 correspond to the for-loop in the C program. Instruction L1 updates the x-members of the array elements, and instruction 8 updates the y-members. Instructions 13 and 14 correspond to initializing the return value for main.

# 2.1 Memory-Regions and Abstract Addresses

This section presents the basic abstract memory model that is used in CodeSurfer/x86's analyses. One simple model considers memory to be an array of bytes. Writes (reads) in this model are treated as writes (reads) to the corresponding element of the array. However, there are some disadvantages in such an approach:

- —It may not be possible to determine specific address values for certain memory blocks, such as those allocated from the heap via malloc. For the analysis to be sound, writes to (reads from) such blocks of memory have to be treated as writes to (reads from) any part of the heap, which leads to imprecise (and mostly useless) information about memory accesses.

- —The runtime stack is reused during each execution run; in general, a given area of the runtime stack will be used by several procedures at different times during

```

typedef struct {

proc main

int x,y;

;Allocate locals

sub esp, 44

} Point:

lea eax, [esp+8] ;t1 = &pts[0].y

mov [esp+0], eax ;py = t1

int a = 1, b = 2;

mov ebx, [4]

;ebx = a

;ecx = b

mov ecx, [8]

int main(){

mov edx, 0

;i = 0

int i, *py;

lea eax,[esp+4]

;p = &pts[0]

Point pts[5], *p;

mov [eax], ebx

L1:

;p->x = a

py = &pts[0].y;

;p->y =

mov [eax+4],ecx

;p += 8

= &pts[0];

add eax. 8

for(i = 0; i < 5; ++i) {

10

inc edx

;i++

cmp edx, 5

p->x = a;

11

p->y = b;

;(i < 5)?L1:exit loop

12

jl L1

p += 8;

mov edi, [esp+0]; t2 = py

13

;set return value (*t2)

14

mov eax. [edi]

15

;Deallocate locals

return *py;

add esp, 44

}

16

retn

(a)

(b)

```

Fig. 2. (a) A C program that initializes an array of structs; (b) the corresponding x86 program (in Intel assembly-language syntax).

execution. Thus, at each instruction a specific numeric address can be ambiguous (because the same address may belong to different Activation Records (ARs) at different times during execution): it may denote a variable of procedure f, a variable of procedure g, a variable of procedure h, etc. (A given address may also correspond to different variables of different activations of f.) Therefore, an instruction that updates a variable of procedure f would have to be treated as possibly updating the corresponding variables of procedures g, h, etc., which also leads to imprecise information about memory accesses.

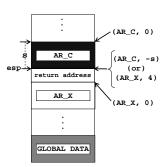

To overcome these problems, we work with the following abstract memory model [Balakrishnan and Reps 2004]. Although in the concrete semantics the activation records for procedures, the heap, and the memory area for global data are all part of one address space, for the purposes of analysis, we separate the address space into a set of disjoint areas, which are referred to as memory-regions (see Fig. 3(b)). Each memory-region represents a group of locations that have similar runtime properties: in particular, the runtime locations that belong to the ARs of a given procedure belong to one memory-region. Each (abstract) byte in a memory-region represents a set of concrete memory locations. For a given program, there are three kinds of regions: (1) the global-region, for memory locations that hold initialized and uninitialized global data, (2) AR-regions, each of which contains the locations of the ARs of a particular procedure, and (3) malloc-regions, each of which contains the locations allocated at a particular malloc site. We do not assume anything about the relative positions of these memory-regions.

For an n-bit architecture, the size of each memory-region in the abstract memory model is  $2^n$ . For each region, the range of offsets within the memory-region is  $[-2^{n-1}, 2^{n-1}-1]$ . Offset 0 in an AR-region represents all concrete starting addresses of the ARs that the AR-region represents. Offset 0 in a malloc-region represents all concrete starting addresses of the heap blocks that the malloc-region represents. Offset 0 of the global-region represents the concrete address 0.

The analysis treats all data objects, whether local, global, or in the heap, in

a fashion similar to the way compilers arrange to access variables in local ARs, namely, via an offset. We adopt this notion as part of our abstract semantics: an abstract address in a memory-region is represented by a pair: (memory-region, offset).

By convention, esp is the stack pointer in the x86 architecture. On entry to a procedure P, esp points to the top of the stack, where the new activation record for P is created. Therefore, in our abstract memory model, esp holds abstract address (AR\_P, 0) on entry to procedure P, where AR\_P is the activation-record region associated with procedure P. Similarly, because malloc returns the starting address of an allocated block, the return value for malloc (if allocation is successful) is the abstract address (Malloc\_n, 0), where Malloc\_n is the memory-region associated with the  $n^{th}$  call-site on malloc.

EXAMPLE 2.2. Fig. 3(c) shows the memory-regions for the program in Ex. 2.1. There is a single procedure, and hence two regions: one for global data and one for the AR of main. Furthermore, the abstract address of local variable py is the pair (AR\_main,-44) because it is at offset -44 with respect to the AR's starting address. Similarly, the abstract address of global variable b is (Global,8).

# 2.2 Abstract Locations (A-Locs)

As pointed out earlier, executables do not have intrinsic entities like source-code variables that can be used for analysis; therefore, the next step is to recover variable-like entities from the executable. We refer to such variable-like entities as a-locs (for "abstract locations").

Heretofore, the state of the art in recovering variable-like entities is represented by IDAPro [IDAPro], a commercial disassembly toolkit. IDAPro's algorithm is based on the observation that the data layout generally follows certain conventions: accesses to global variables appear as "[absolute-address]", and accesses to local variables appear as "[esp + offset]" or "[ebp - offset]". IDAPro identifies such statically-known absolute addresses, esp-based offsets, and ebp-based offsets in the program, and treats the set of locations in between two such absolute addresses or offsets as one entity. We refer to this method of recovering a-locs as the Semi-Naïve algorithm. The Semi-Naïve algorithm is based on purely local techniques. (IDAPro does incorporate a few global analyses, such as one for determining changes in stack height at call-sites. However, the techniques are ad-hoc, heuristic methods.)

In CodeSurfer/x86, the Semi-Naïve algorithm is used to identify the *initial* set of a-locs; several global analyses based on abstract interpretation are then used to obtain an improved set of a-locs. The latter methods are discussed in §4.

Let us look at the a-locs identified by the Semi-Naïve algorithm for the program in Ex. 2.1.

<sup>&</sup>lt;sup>4</sup>CodeSurfer/x86 actually uses an abstraction of heap-allocated storage, called the *recency abstraction*, that involves more than one memory-region per call-site on malloc [Balakrishnan and Reps 2006]. The recency abstraction overcomes some of the imprecision that arises due to the need to perform weak updates—i.e., accumulate information via join—on fields of summary mallocregions. In particular, the augmented domain often allows our analysis to establish a definite link between a pointer field of a heap-allocated object and objects pointed-to by the pointer field. Due to space considerations, this technique is not described in this paper.

Fig. 3. (a) Layout of the activation record for procedure main in Ex. 2.1; (b) abstract memory model; (c) a-locs identified by the Semi-Naïve algorithm.

Global a-locs. In Ex. 2.1, instructions "mov ebx, [4]" and "mov ecx, [8]" have direct memory operands, namely, [4] and [8]. IDAPro identifies these statically-known absolute addresses as the starting addresses of global a-locs and treats the locations between these addresses as one a-loc. Consequently, IDAPro identifies addresses 4..7 as one a-loc, and the addresses 8..11 as another a-loc. Therefore, we have two a-locs: mem\_4 (for addresses 4..7) and mem\_8 (for addresses 8..11). (An executable can have sections for read-only data. The global a-locs in such sections are marked as read-only a-locs.)

Local a-locs. Local a-locs are determined on a per-procedure basis as follows. At each instruction in the procedure, IDAPro computes the difference between the value of esp (or ebp) at that point and the value of esp at procedure entry. These computed differences are referred to as sp\_delta.<sup>5</sup> After computing sp\_delta values, IDAPro identifies all esp-based indirect operands in the procedure. In Ex. 2.1, instructions "lea eax, [esp+8]", "mov [esp+0], eax", "lea eax, [esp+4]", and "mov edi, [esp+0]" have esp-based indirect operands. Recall that on entry to procedure main, esp contains the abstract address (AR\_main, 0). Therefore, for every esp/ebp-based operand, the computed sp\_delta values give the corresponding offset in AR\_main. For instance, [esp+0], [esp+4], and [esp+8] refer to offsets -44, -40, and -36, respectively, in AR\_main. This gives rise to three local a-locs: var\_44, var\_40, and var\_36. Note that var\_44 corresponds to all of the source-code variable py. In contrast, var\_40 and var\_36 correspond to disjoint segments of array pts[]: var\_40 corresponds to program variable pts[0].x; var\_36 corresponds to the locations of program variables pts[0].y, p[1..4].x, and p[1..4].y. In addition to these a-locs, an a-loc for the return address is also

<sup>&</sup>lt;sup>5</sup>When IDAPro computes the sp\_delta values, it uses heuristics to identify changes to esp (or ebp) at procedure calls and instructions that access memory, and therefore the sp\_delta values may be incorrect. Consequently, the layout obtained by IDAPro for an AR may not be in agreement with the way that memory is actually accessed during execution runs. This can have an impact on the precision of the results obtained by our abstract-interpretation algorithms; however, as discussed in §4.4, the results obtained by the algorithms are still sound, even if the initial set of a-locs is suboptimal because of incorrect sp\_delta values.

defined; its offset in AR\_main is 0.

In addition to the a-locs identified by IDAPro, two more a-locs are added:(1) a FormalGuard that spans the space beyond the topmost a-loc in the AR-region, and (2) a LocalGuard that spans the space below the bottom-most a-loc in the AR-region. FormalGuard and LocalGuard delimit the boundaries of an activation record; therefore, a memory write to FormalGuard or LocalGuard represents a write beyond the end of an activation record.

*Heap a-locs.* In addition to globals and locals, we have one a-loc per heap-region. There are no heap a-locs in Ex. 2.1 because it does not use the heap.

Registers. In addition to the global, heap, and local a-locs, registers are also considered to be a-locs.

After the a-locs are identified, we create a mapping from a-locs to (rgn, off, size) triples, where rgn represents the memory-region to which the a-loc belongs, off is the starting offset of the a-loc in rgn, and size is the size of the a-loc. The starting offset of an a-loc a in a region rgn is denoted by offset(rgn, a). For Ex. 2.1,  $offset(AR_main, var_40)$  is -40 and  $offset(Global, mem_4)$  is 4. The a-loc layout map can also be queried in the opposite direction: for a given region, offset, and size, what are the overlapping a-locs? As described in §3.4, such information is used to interpret memory-dereferencing operations during VSA.

# 3. VALUE-SET ANALYSIS (VSA)

Another significant obstacle in analyzing executables is that it is difficult to obtain useful information about memory-access expressions in the executable. Information about memory-access expressions is a crucial requirement for any tool that works on executables. Consider the problem of identifying possible data dependences between instructions in executables. An instruction  $i_1$  is data dependent on another instruction  $i_2$  if  $i_1$  might read the data that  $i_2$  writes. For instance, in Ex. 2.1, instruction 14 is data dependent on instruction 8 because instruction 8 writes to pts[0].y and instruction 14 reads from pts[0].y. On the other hand, instruction 14 is not data dependent on instruction L1.

There has been work in the past on analysis techniques to obtain such information. However, prior techniques are either overly-conservative or unsound in their treatment of memory accesses. The alias-analysis algorithm proposed by Debray et al. [Debray et al. 1998] assumes that any memory write can affect any other memory read. Therefore, their algorithm reports that instruction 14 is data dependent on both L1 and 8—i.e., it provides an overly-conservative treatment of memory operations. On the other hand, Cifuentes et al. [Cifuentes and Fraboulet 1997b] use heuristics to determine if two memory operands are aliases of one another, and hence may fail to identify the data dependence between instruction 8 and instruction 14.

To obtain information about memory-access expressions, CodeSurfer/x86 makes use of a number of analyses, and the sequence of analyses performed is itself iterated (for reasons discussed in §5). The variable and type-discovery phase of CodeSurfer/x86 recovers information about variables that are allocated globally, locally (i.e., on the stack), and dynamically (i.e., from the freelist); see §2.2 and §4. The recovered variables (a-locs) are the basic variables used in CodeSurfer/x86's

value-set-analysis (VSA) algorithm, which statically identifies the set of values that the a-locs may contain when an instruction I executes. This section describes the VSA algorithm.

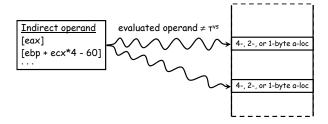

VSA is a combined numeric-analysis and pointer-analysis algorithm that determines a safe approximation of the set of numeric values or addresses that each register and a-loc holds at each program point. In particular, at each instruction I that contains an indirect memory operand, VSA provides information about the contents of the registers that are used. This permits it to determine the (abstract) addresses that are potentially accessed—and hence the a-locs that are potentially accessed—which, in turn, permits it to determine the potential effects of I on the state.

The problem that VSA addresses has similarities with the *pointer-analysis* problem that has been studied in great detail for programs written in high-level languages [Hind 2001]. For each variable (say v), pointer analysis determines an overapproximation of the set of variables whose addresses v can hold. Similarly, VSA determines an over-approximation of the set of addresses that a register or a memory location holds at each program point. For instance, VSA determines that at instruction L1 in Ex. 2.1 eax holds one of the offsets  $\{-40, -32, -24, \ldots, -8\}$  in the activation record of procedure main, which corresponds to the addresses of field v of the elements of array pts [0..4].

On the other hand, VSA also has some of the flavor of numeric static analyses, where the goal is to over-approximate the integer values that each variable can hold; in addition to information about addresses, VSA determines an over-approximation of the set of integer values that each data object can hold at each program point. For instance, VSA determines that at instruction L1, edx holds numeric values in the range  $0, \ldots, 4$ .

A key feature of VSA is that it tracks integer-valued and address-valued quantities simultaneously. This is crucial for analyzing executables because numeric operations and address-dereference operations are inextricably intertwined even in the instruction(s) generated for simple source-code operations. For instance, consider the operation of loading the value of a local variable v into register eax. If v has offset -12 in the current AR, the load would be performed by the instruction mov eax, [ebp-12]. This involves a numeric operation (ebp-12) to calculate an address whose value is then dereferenced ([ebp-12]) to fetch the value of v, after which the value is placed in eax. A second key feature of VSA is that, unlike earlier algorithms [Cifuentes and Fraboulet 1997a; 1997b; Cifuentes et al. 1998; Debray et al. 1998], it takes into account data manipulations that involve memory locations.

VSA is based on abstract interpretation [Cousot and Cousot 1977], where the aim is to determine the possible states that a program reaches during execution, but without actually running the program on specific inputs. The set of descriptors of memory configurations used in abstract interpretation is referred to as an *abstract domain*. An element of an abstract domain represents a set of concrete (i.e., runtime) states of a program. An element of the abstract domain for VSA associates each a-loc with a set of (abstract) memory addresses and numeric values.

VSA is a flow-sensitive, context-sensitive, interprocedural, abstract-interpretation algorithm (parameterized by call-string length [Sharir and Pnueli 1981]). In the rest of this section, we formalize the VSA domain and describe the VSA algorithm in

detail.

# 3.1 Value-Sets

A value-set represents a set of memory addresses and numeric values. Recall from §2.1 that each abstract address is a pair (memory-region, offset). Therefore, a set of abstract addresses can be represented by a set of tuples of the form ( $rgn_i \mapsto \{o_1^i, o_2^i, ..., o_{n_i}^i\}$ ). A value-set uses a k-bit strided-interval (SI) [Reps et al. 2006] to represent the set of offsets in each memory-region. Let  $\gamma$  denote the concretization function for the strided-interval domain; a k-bit strided interval  $\mathbf{s}[\mathbf{lb}, \mathbf{ub}]$  represents the set of integers

$$\gamma(\mathbf{s}[\mathbf{lb}, \mathbf{ub}]) = \{i \in [-2^{k-1}, 2^{k-1} - 1] \mid l \le i \le u, i \equiv l \pmod{s}\}, \text{ where}$$

- —s is called the *stride*.

- $-[\mathbf{l}, \mathbf{u}]$  is called the *interval*.

- -0[1,1] represents the singleton set  $\{l\}$ .

We also call  $\perp$  a strided interval; it denotes the empty set of offsets.

Consider the set of addresses  $S = \{(\mathtt{Global} \mapsto \{1,3,5,9\}), (\mathtt{AR\_main} \mapsto \{-48,-40\})\}$ . The value-set for S is the set  $\{(\mathtt{Global} \mapsto \mathbf{2[1,9]}), (\mathtt{AR\_main} \mapsto \mathbf{8[-48,-40]})\}$ . Note that the value-set for S is an over-approximation; the value-set includes the global address 7, which is not an element of S. For conciseness, a value-set will be shown as an r-tuple of SIs, where r is the number of memory-regions for the executable. By convention, the first component of the r-tuple represents addresses in the SIobal memory-region. Using this notation, the value-set for S is the 2-tuple, (2[1,9],8[-48,-40]).

A value-set is capable of representing a set of memory addresses as well as a set of numeric values. For instance, the 2-tuple  $(\mathbf{2}[\mathbf{1},\mathbf{9}],\perp)$  denotes the set of numeric values  $\{1,3,5,7,9\}$  as well as the set of addresses  $\{(\mathtt{Global},1),(\mathtt{Global},3),\ldots,(\mathtt{Global},9)\}$ ; the 2-tuple  $(\perp,\mathbf{8}[-4\mathbf{8},-4\mathbf{0}])$  represents the set of addresses  $\{(\mathtt{AR\_main},-48),(\mathtt{AR\_main},-40)\}$ . This is a crucial requirement for analyzing executables because numbers and addresses are indistinguishable at runtime

Advantages of Strided Intervals for Analysis of Executables. We chose to use SIs instead of ranges because alignment and stride information allow indirect-addressing operations that implement either (i) field-access operations in an array of structs, or (ii) pointer-dereferencing operations, to be interpreted more precisely.

Let \*a denote a dereference of a-loc a. Suppose that the contents of a is not aligned with the boundaries of other a-locs; then a memory access \*a can fetch portions of two or more a-locs. Similarly, an assignment to \*a can overwrite portions of two or more a-locs. Such operations appear to forge new addresses. For instance, suppose that the address of a-loc x is 1000, the address of a-loc y is 1004, and the contents of a-loc a is 1001. Then \*a (as a 4-byte fetch) would retrieve 3 bytes of x's value and 1 byte of y's value.

This issue motivated the use of SIs because SIs are capable of representing certain non-convex sets of integers, and ranges (alone) are not. Suppose that the contents of a is the set  $\{1000, 1004\}$ ; then \*a (as a 4-byte fetch) would retrieve all of x (and none of y) or all of y (and none of x). The range [1000, 1004] includes the addresses 1001, 1002, and 1003, and hence \*[1000, 1004] (as a 4-byte fetch) could result in a

forged address. However, because VSA is based on SIs,  $\{1000, 1004\}$  is represented exactly, as the SI 4[1000, 1004]. If VSA were based on range information rather than SIs, it would either have to try to track *segments* of (possible) contents of data objects, or treat such dereferences conservatively by returning  $\top^{vs}$ , thereby losing track of all information.

The Value-Set Abstract Domain. Value-sets form a lattice. Informal descriptions of a few 32-bit value-set operators are given below. (For a detailed description of the value-set domain, see [Reps et al. 2006].)

- $-(vs_1 \sqsubseteq^{vs} vs_2)$ : Returns true if the value-set  $vs_1$  is a subset of  $vs_2$ , false otherwise.

- $-(vs_1 \sqcap^{vs} vs_2)$ : Returns the meet (intersection) of value-sets  $vs_1$  and  $vs_2$ .

- $-(vs_1 \sqcup^{vs} vs_2)$ : Returns the join (union) of value-sets  $vs_1$  and  $vs_2$ .

- $-(vs_1 \nabla^{vs} vs_2)$ : Returns the value-set obtained by widening [Cousot and Cousot 1976]  $vs_1$  with respect to  $vs_2$ , e.g., if  $vs_1 = (\mathbf{4}[\mathbf{40}, \mathbf{44}])$  and  $vs_2 = (\mathbf{4}[\mathbf{40}, \mathbf{48}])$ , then  $(vs_1 \nabla^{vs} vs_2) = (\mathbf{4}[\mathbf{40}, \mathbf{2^{31}} \mathbf{4}])$ . Note that the upper bound for the interval in the result is  $\mathbf{2^{31}} \mathbf{4}$  (and not  $\mathbf{2^{31}} \mathbf{1}$ ) because  $\mathbf{2^{31}} \mathbf{4}$  is the maximum positive value that is congruent to  $\mathbf{40}$  modulo  $\mathbf{4}$ .

- $-(vs + v^s c)$ : Returns the value-set obtained by adjusting all values in vs by the constant c, e.g., if vs = (4, 4[4, 12]) and c = 12, then  $(vs + v^s c) = (16, 4[16, 24])$ .

- -\*(vs, s): Returns a pair of sets (F, P). F represents the set of "fully accessed" a-locs: it consists of the a-locs that are of size s and whose starting addresses are in vs. P represents the set of "partially accessed" a-locs: it consists of (i) a-locs whose starting addresses are in vs but are not of size s, and (ii) a-locs whose addresses are in vs but whose starting addresses and sizes do not meet the conditions to be in F. (This information is obtained using the a-loc layout map described in §2.2.)

- —RemoveLowerBounds (vs): Returns the value-set obtained by setting the lower bound of each component SI to  $-2^{31}$ . For example, if  $vs = (\mathbf{1}[\mathbf{0}, \mathbf{100}], \mathbf{1}[\mathbf{100}, \mathbf{200}])$ , then RemoveLowerBounds (vs) =  $(\mathbf{1}[-2^{31}, \mathbf{100}], \mathbf{1}[-2^{31}, \mathbf{200}])$ .

- —RemoveUpperBounds(vs): Similar to RemoveLowerBounds, but sets the upper bound of each component to  $2^{31} 1$ .

# 3.2 Abstract Environment (AbsEnv)

AbsEnv (for "abstract environment") is the abstract domain used during VSA to represent a set of concrete stores that arise at a given program point. This section formalizes AbsEnv.

Let Proc denote the set of memory-regions associated with procedures in the program; AllocMemRgn denote the set of memory-regions associated with heap-allocation sites; Global denote the memory-region associated with the global data area; and a-locs[R] denote the a-locs that belong to memory-region R. We work with the following basic domains:

```

\begin{split} \mathsf{MemRgn} &= \{\mathsf{Global}\} \cup \mathsf{Proc} \cup \mathsf{AllocMemRgn} \\ \mathsf{ValueSet} &= \mathsf{MemRgn} \rightarrow \mathsf{StridedInterval}_{\perp} \\ \mathsf{AlocEnv}[R] &= \mathsf{a-locs}[R] \rightarrow \mathsf{ValueSet} \\ \mathsf{Flag} &= \{\mathsf{CF}, \mathsf{ZF}, \mathsf{SF}, \mathsf{PF}, \mathsf{AF}, \mathsf{OF}\} \end{split}

```

Flag represents the set of x86 flags. An x86 flag is either set to TRUE or FALSE at runtime. To represent multiple possible Boolean values, we use the abstract domain Bool3:

```

Bool3 = \{FALSE, MAYBE, TRUE\}.

```

In addition to the Booleans False and True, Bool3 has a third value, Maybe, which means "the value is unknown" (i.e., it may be False or it may be True). AbsEnv maps each region R to its corresponding AlocEnv[R], each register to a ValueSet, and each Flag to a Bool3:

```

\begin{array}{c} (\mathsf{register} \to \mathsf{ValueSet}) \\ \times (\mathsf{Flag} \to \mathsf{Bool3}) \\ \mathsf{AbsEnv} = \times (\{\mathsf{Global}\} \to \mathsf{AlocEnv[Global]}) \\ \times (\mathsf{Proc} \to \mathsf{AlocEnv[Proc]}_{\bot}) \\ \times (\mathsf{AllocMemRgn} \to \mathsf{AlocEnv[AllocMemRgn]}_{\bot}) \end{array}

```

In the above definitions,  $\bot$  is used to denote a partial map. For instance, a ValueSet may not contain offsets in some memory-regions. Similarly, in AbsEnv, a procedure P whose activation record is not on the stack is mapped to  $\bot$  rather than to a value in AlocEnv[P].

We use the following notational conventions:

- —Given a memory a-loc or a register a-loc a and  $ae \in \mathsf{AbsEnv}, \ ae[a]$  refers to the ValueSet for a-loc a in ae.

- —Given  $vs \in \mathsf{ValueSet}$  and  $r \in \mathsf{MemRgn}, \ vs[r]$  refers to the strided interval for memory-region r in vs.

- —Given  $f \in \mathsf{Flag}$  and  $ae \in \mathsf{AbsEnv}$ , ae[f] refers to the Bool3 for flag f in ae.

# 3.3 Representing Abstract Stores Efficiently

To represent the abstract store at each program point efficiently, we use applicative dictionaries, which provide a space-efficient representation of a collection of dictionary values when many of the dictionary values have nearly the same contents as other dictionary values in the collection [Reps et al. 1983; Myers 1984].

Applicative dictionaries can be implemented using applicative balanced trees, which are standard balanced trees on which all operations are carried out in the usual fashion, except that whenever one of the fields of an interior node M would normally be changed, a new node M' is created that duplicates M, and changes are made to the fields of M'. To be able to treat M' as the child of  $\operatorname{parent}(M)$ , it is necessary to change the appropriate child-field in  $\operatorname{parent}(M)$ , so a new node is created that duplicates  $\operatorname{parent}(M)$ , and so on, all the way to the root of the tree. Thus, new nodes are introduced for each of the original nodes along the path from M to the root of the tree.

Because an operation that restructures a standard balanced tree may modify all of the nodes on the path to the root anyway, and because a single operation on a standard balanced tree that has n nodes takes at most  $O(\log n)$  steps, the same operation on an applicative balanced tree introduces at most  $O(\log n)$  additional nodes and also takes at most  $O(\log n)$  steps. The new tree resulting from the operation shares the entire structure of the original tree except for the nodes on a

path from M' to the root, plus at most  $O(\log n)$  other nodes that may be introduced to maintain the balance properties of the tree. In our implementation, the abstract stores from the VSA domain are implemented using applicative AVL trees [Myers 1984]. That is, each function or partial function in a component of AbsEnv is implemented with an applicative AVL tree.

### 3.4 Intraprocedural Value-Set Analysis

This subsection describes an intraprocedural version of VSA. For the time being, we consider programs that have a single procedure and no indirect jumps. To aid in explaining the algorithm, we adopt a C-like notation for program statements. We will discuss the following kinds of instructions, where R1 and R2 are two registers of the same size, c,  $c_1$ , and  $c_2$  are explicit integer constants, and  $\leq$  and  $\geq$  represent signed comparisons:

$$\begin{array}{ll} {\rm R1} = {\rm R2} + c & {\rm R1} \leq c \\ *({\rm R1} + c_1) = {\rm R2} + c_2 & {\rm R1} \geq {\rm R2} \\ {\rm R1} = *({\rm R2} + c_1) + c_2 & \end{array}$$

Conditions of the two forms shown on the right are obtained from the instruction(s) that set condition codes used by branch instructions (see §3.4.2).

The analysis is performed on a control-flow graph (CFG) for the procedure. The CFG consists of one node per x86 instruction, and there is a directed edge  $n_1 \rightarrow n_2$  between a pair of nodes  $n_1$  and  $n_2$  in the CFG if there is a flow of control from  $n_1$  to  $n_2$ . The edges are labeled with the instruction at the source of the edge. If the source of an edge is a branch instruction, then the edge is labeled according to the outcome of the branch. For instance in the CFG for the program in Ex. 2.1, the edge  $12\rightarrow L1$  is labeled edx<5, whereas the edge  $12\rightarrow 13$  is labeled  $edx\geq 5$ . Each CFG has two special nodes: (1) an enter node that represents the entry point of the procedure, (2) an exit node that represents the exit point of the procedure.

Each edge in the CFG is associated with an abstract transformer that captures the semantics of the instruction represented by the CFG edge. Each abstract transformer takes an  $in \in \mathsf{AbsEnv}$  and returns a new  $out \in \mathsf{AbsEnv}$ . Sample abstract transformers for various kinds of edges are listed in Fig. 4. Interesting cases in Fig. 4 are described below:

- —Because each AR region of a procedure that may be called recursively—as well as each heap region—potentially represents more than one concrete data object, assignments to their a-locs must be modeled by weak updates, i.e., the new value-set must be joined with the existing one, rather than replacing it (see case two of Fig. 4).

- —Furthermore, unaligned writes can modify parts of various a-locs (which could possibly create forged addresses). In case 2 of Fig. 4, such writes are treated safely by setting the values of all partially modified a-locs to  $\top^{vs}$ . Similarly, case 3 treats a load of a potentially forged address as a load of  $\top^{vs}$ . (Techniques for more precise handling of partial accesses to a-locs are discussed in §4.)

Given a CFG G for a procedure (without calls), the goal of intraprocedural VSA is to annotate each node n with absEnv<sub>n</sub>  $\in$  AbsEnv, where absEnv<sub>n</sub> represents an over-approximation of the set of memory configurations that arise at node n

| Instruction                                | AbstractTransformer(in: AbsEnv): AbsEnv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                            | Let $out := in$ and $vs_{R2} := in[R2]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| R1 = R2 + c                                | $out[R1] := vs_{R2} + v^{s} c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 161 — 162   6                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| $*(R1+c_1) = R2+c_2$                       | return out  Let $vs_{\mathbb{R}1} := in[\mathbb{R}1]$ , $vs_{\mathbb{R}2} := in[\mathbb{R}2]$ , $(F,P) = *(vs_{\mathbb{R}1} + ^{vs}c_1, s)$ , and out $:= in$ Let $Proc$ be the procedure containing the instruction if $( F  = 1 \land  P  = 0 \land (F \text{ has no heap a-locs or a-locs of recursive procedures}))$ then $out[v] := vs_{\mathbb{R}2} + ^{vs}c_2$ , where $v \in F //$ Strong update else for each $v \in F$ do $out[v] := out[v] \sqcup^{vs}(vs_{\mathbb{R}2} + ^{vs}c_2) //$ Weak update end for end if for each $v \in P$ do $//$ Set partially accessed a-locs to $T^{vs}$ $out[v] := T^{vs}$ |  |  |  |  |

|                                            | end for return out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| $\mathtt{R1} = *(\mathtt{R2} + c_1) + c_2$ | Let $v_{\mathtt{R}2} := in[\mathtt{R}2]$ , $(F,P) = *(vs_{\mathtt{R}2} + v^s c_1,s)$ and $out := in$ if $( P  = 0)$ then  Let $vs_{rhs} := \bigsqcup^{\mathtt{vs}} \{in[v] \mid v \in F\}$ $out[\mathtt{R}1] := vs_{rhs} + v^s c_2$ else $out[\mathtt{R}1] := \top^{vs}$ end if  return $out$                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| R1 $\leq c$                                | Let $vs_c := ([-2^{31}, c], \top^{si}, \dots, \top^{si})$ and $out := in$ $out[\mathtt{R1}] := in[\mathtt{R1}] \sqcap^{vs} vs_c$ return $out$                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| $\mathtt{R1} \geq \mathtt{R2}$             | Let $v_{\mathtt{R}1} := in[\mathtt{R}1]$ and $v_{\mathtt{R}2} := in[\mathtt{R}2]$<br>Let $v_{Slb} := \mathtt{RemoveUpperBounds}(v_{\mathtt{R}2})$ and $v_{Sub} := \mathtt{RemoveLowerBounds}(v_{\mathtt{R}1})$<br>out := in<br>$out[\mathtt{R}1] := v_{\mathtt{R}1} \sqcap^{\mathtt{vs}} v_{\mathtt{S}lb}$<br>$out[\mathtt{R}2] := v_{\mathtt{R}2} \sqcap^{\mathtt{vs}} v_{\mathtt{S}ub}$<br>$return \ out$                                                                                                                                                                                                           |  |  |  |  |

Fig. 4. Abstract transformers for VSA. (In the second and third instruction forms, s represents the size of the dereference performed by the instruction.)

over all possible runs of the program. The intraprocedural version of the VSA algorithm is given in Fig. 5. The value of absEnv<sub>enter</sub> consists of information about the initialized global variables and the initial value of the stack pointer (esp).

The AbsEnv abstract domain has very long ascending chains.<sup>6</sup> Hence, to ensure termination, widening needs to be performed. Widening needs to be carried out at at least one edge of every cycle in the CFG; however, the edge at which widening is performed can affect the accuracy of the analysis. To choose widening edges, our implementation of VSA uses techniques from [Bourdoncle 1993] (see [Balakrishnan 2007, Ch. 7]).

EXAMPLE 3.1. This example presents the results of intraprocedural VSA for the program in Ex. 2.1. For the program in Ex. 2.1, the AbsEnv for the entry node of

<sup>&</sup>lt;sup>6</sup>The domain is of bounded height because strided intervals are based on 32-bit two's complement arithmetic. However, for a given executable, the bound is very large: each a-loc can have up to  $|\mathsf{MemRgn}|$  SIs; hence the height is  $(n \times |\mathsf{MemRgn}| \times 2^{32})$ , where n is the total number of a-locs.

```

1: decl worklist: Set of Node

3: proc IntraProceduralVSA()

worklist := \{ enter \}

absEnventer := Initial values of global a-locs and esp

while (worklist \neq \emptyset) do

7:

Select and remove a node n from worklist

8:

m := Number of successors of node n

9:

for i = 1 to m do

10:

succ := GetCFGSuccessor(n, i)

edge\_amc := AbstractTransformer(n \rightarrow succ, absEnv_n)

11:

12:

Propagate(succ, edge_amc)

13:

end for

14:

end while

15: end proc

16:

17: proc Propagate(n: Node, edge_amc: AbsEnv)

old := absEnv_n

18:

new := old \sqcup^{ae} edge\_amc

19:

if (old \neq new) then

20:

21:

absEnv_n := new

worklist := worklist \cup \{n\}

23:

end if

24: end proc

```

Fig. 5. Intraprocedural VSA Algorithm.

main is  $\{ esp \mapsto (\bot, \mathbf{0}), mem\_4 \mapsto (\mathbf{1}, \bot), mem\_8 \mapsto (\mathbf{2}, \bot) \}$ . Recall that instruction "L1:mov [eax], ebx" updates the x members of array pts. Instruction "14: mov eax, [edi]" initializes the return value of main to p[0].y. The results of the VSA algorithm at instructions L1, 8, and 14 are as follows:

| Instruction L1 and 8 |                                                | Instructio      | on 14                                          |

|----------------------|------------------------------------------------|-----------------|------------------------------------------------|

| esp                  | $\mapsto (\bot, -44)$                          | esp             | $\mapsto (\perp, -44)$                         |

| mem_4                | $\mapsto (1, ot)$                              | mem_4           | $\mapsto (1, \perp)$                           |

|                      | $\mapsto (2, ot)$                              | mem_8           | $\mapsto (2, ot)$                              |

| eax                  | $\mapsto (\perp, 8[-40, \mathbf{2^{31}} - 8])$ | eax             | $\mapsto (\perp, 8[-40, \mathbf{2^{31}} - 8])$ |

| ebx                  | $\mapsto (1, ot)$                              | ebx             | $\mapsto (1, \perp)$                           |

| ecx                  | $\mapsto (2, ot)$                              | ecx             | $\mapsto (2, \perp)$                           |

| edx                  | $\mapsto (1[0,4],ot)$                          | edx             | $\mapsto (5, \perp)$                           |

| edi                  | $\mapsto \top^{vs}$                            | edi             | $\mapsto (\perp, -36)$                         |

| var_44               | $\mapsto (\perp, -36)$                         | var <b>_</b> 44 | $\mapsto (\perp, -36)$                         |

For instance, VSA recovers the following facts:

- —At instruction L1, the set of possible values for edx is  $\{0, 1, 2, 3, 4\}$ . At instruction 14, the only possible value for edx is 5. (Recall that edx corresponds to the loop variable i in the C program.)

- —At instruction L1, eax holds the following set of addresses:  $\{(\texttt{AR\_main}, -40), (\texttt{AR\_main}, -32), \dots, (\texttt{AR\_main}, 0), \dots, (\texttt{AR\_main}, 2^{31} 8)\}.$  That is, at instruction L1, eax holds the addresses of the local a-locs var\_40, var\_36, ret-addr, and FormalGuard. (See Fig. 3(b) for the layout of AR\\_main.)

Therefore, instruction L1 possibly modifies var\_40, var\_36, ret-addr, and FormalGuard.

Similarly, at instruction 8, eax+4 refers to the following set of addresses:  $\{(\texttt{AR\_main}, -36), (\texttt{AR\_main}, -28), \dots, (\texttt{AR\_main}, 4), \dots, (\texttt{AR\_main}, 2^{31} - 4)\}.$

Therefore, instruction 8 possibly modifies var\_36 and FormalGuard.

—At instruction 14, the only possible value for edi is the address (AR\_main, -36), which corresponds to the address of the local a-loc var\_36.

The value-sets obtained by the analysis can be used to discover the data dependence that exists between instructions 8 and 14. At instruction 8, the set of possibly-modified a-locs is {var\_36, FormalGuard}. At instruction 14, the set of used a-locs is {var\_36}. Reaching-definitions analysis based on this information reveals that instruction 14 is data dependent on instruction 8.

Reaching-definitions analysis based on the information at instruction L1 would also reveal that instruction 14 is also data dependent on instruction L1, which is spurious (i.e., a false positive), because the set of actual addresses accessed at instruction L1 and instruction 14 are different. The reason for the spurious data dependence is that the Semi-Naïve algorithm, described in §2, recovers too coarse a set of a-locs. For instance, for the program in Ex. 2.1, the Semi-Naïve algorithm failed to recover any information about the array pts. §4 presents an improved a-loc-recovery algorithm that is capable of recovering information about arrays, fields of structs, etc., thereby reducing the number of spurious data dependences.

At instruction L1, the set of possibly-modified a-locs includes ret-addr, which is the a-loc for the return address. This is because the analysis was not able to determine a precise upper bound for eax at instruction L1, although register edx has a precise upper and lower bound at instruction L1. Note that, because eax and edx are incremented in lock-step within the loop, the affine relation  $eax = (esp + edx \times 8) + 4$  holds at instruction L1. The implemented system identifies such affine relations and uses them to find precise upper or lower bounds for registers, such as eax, within a loop [Balakrishnan 2007, Ch. 7, Sect. 2].

3.4.1 *Idioms*. Before applying an abstract transformer, the instruction is checked to see if it matches a pattern for which we know how to carry out abstract interpretation more precisely than if value-set arithmetic were to be performed directly. Some examples are given below.

XOR r1,r2, when r1 = r2 = r. The XOR instruction sets its first operand to the bitwise-exclusive-or ( $^{\wedge}$ ) of the instruction's two operands. The idiom catches the case when XOR is used to set a register to 0; hence, the a-loc for register r is set to the value-set  $(0[0,0], \perp, \ldots)$ .

TEST r1,r2, when r1 = r2 = r. The TEST instruction computes the bitwise-and (&) of its two operands, and sets the SF, ZF, and PF flags according to the result. The idiom addresses how the value of ZF is set when the value-set of r has the form  $(si, \perp, \ldots)$ :

$$ZF := \begin{cases} True & \text{if } \gamma(\mathbf{si}) = \{0\} \\ False & \text{if } \gamma(\mathbf{si}) \cap \{0\} = \emptyset \\ Maybe & \text{otherwise} \end{cases}$$

|                                                                                                        | cmp X, Y                                   |                              | sub X, Y                                |             | test X, Y               |                                              |

|--------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------------------|-----------------------------------------|-------------|-------------------------|----------------------------------------------|

|                                                                                                        | Flag Predicate                             | Predicate                    | Flag Predicate                          | Predicate   | Flag Predicate          | Predicate                                    |

|                                                                                                        | Unsigned Comparisons                       |                              |                                         |             |                         |                                              |

| ja, jnbe                                                                                               | $\neg \mathtt{CF} \wedge \neg \mathtt{ZF}$ | $X >_u Y$                    | $\neg CF \land \neg ZF$                 | $X' \neq 0$ | $\neg ZF$               | $X\&Y \neq 0$                                |

| jae, jnb, jnc                                                                                          | ¬CF                                        | $X \ge_u Y$                  | ¬CF                                     | True        | True                    | True                                         |

| jb,jnae,jc                                                                                             | CF                                         | $X <_u Y$                    | CF                                      | $X' \neq 0$ | False                   | False                                        |

| jbe,jna                                                                                                | $CF \lor ZF$                               | $X \leq_u Y$                 | $CF \lor ZF$                            | True        | ZF                      | X & Y = 0                                    |

| je,jz                                                                                                  | ZF                                         | X = Y                        | ZF                                      | X' = 0      | ZF                      | X&Y = 0                                      |

| jne, jnz                                                                                               | ¬ZF                                        | $X \neq Y$                   | ¬ZF                                     | $X' \neq 0$ | $\neg ZF$               | $X\&Y \neq 0$                                |

|                                                                                                        | Signed Comparisons                         |                              |                                         |             |                         |                                              |

| jg,jnle                                                                                                | $\neg ZF \land (OF \Leftrightarrow SF)$    | X > Y                        | $\neg ZF \land (OF \Leftrightarrow SF)$ | X' > 0      | $\neg ZF \land \neg SF$ | $(X\&Y \neq 0) \land (X > 0 \lor Y > 0)$     |

| jge,jnl                                                                                                | OF ⇔ SF                                    | $\mathtt{X} \geq \mathtt{Y}$ | OF ⇔ SF                                 | True        | ¬SF                     | $(\mathtt{X} \geq 0 \lor \mathtt{Y} \geq 0)$ |

| jl,jnge                                                                                                | $(\mathtt{OF} \oplus \mathtt{SF})$         | X < Y                        | $(\mathtt{OF} \oplus \mathtt{SF})$      | X' < 0      | SF                      | $(X < 0 \land Y < 0)$                        |

| jle,jng                                                                                                | ${\tt ZF} \lor {\tt OF} \oplus {\tt SF}$   | $\mathtt{X} \leq \mathtt{Y}$ | $ZF \lor (OF \oplus SF)$                | True        | $ZF \lor SF$            | $(X \& Y = 0) \lor (X < 0 \land Y < 0)$      |

| (Note: $A \oplus B = (\neg A \land B) \lor (A \land \neg B)$ , & refers to the bitwise-and operation.) |                                            |                              |                                         |             |                         |                                              |

Fig. 6. High-level predicates for conditional jump instructions. (In column 5, X' refers to the value of X after the instruction executes. Because test sets CF and OF to FALSE, the flag predicates in column 6 have been simplified accordingly.)

where ' $\gamma$ ' is the concretization function for the strided-interval domain (see §3.1).

CMP a,b or CMP b,a. In the present implementation, we assume that an allocation always succeeds (and hence value-set analysis only explores the behavior of the system on executions in which allocations always succeed). Under this assumption, we can apply the following idiom: Suppose that  $k1, k2, \ldots$  are malloc-regions, the value-set for a is  $(\bot, \ldots, si_{k1}, si_{k2}, \ldots)$ , and the value-set for b is  $(\mathbf{0}[\mathbf{0}, \mathbf{0}], \bot, \ldots)$ . Then ZF is set to FALSE.

3.4.2 Predicates for Conditional Branch Instructions. In x86 architectures, predicates used in high-level control constructs such as if, while, for, etc. are implemented using conditional branch instructions. A conditional branch instruction (say jxx TGT) evaluates a predicate involving the processor's flags and transfers control to the target instruction (TGT) if the predicate expression is True; otherwise, it transfers control to the next instruction. For instance, a j1 instruction evaluates the conditional expression SF = 1, where SF is the sign flag. It is not clear from conditional expressions such as SF = 1 what the high-level predicate is.