# Typhoon-Zero Implementation: The Vortex Module

Robert W. Pfile

Technical Report #1290

October 1995

# Typhoon-Zero Implementation: The Vortex Module

Robert W. Pfile Wisconsin Wind Tunnel Project Computer Sciences Department University of Wisconsin – Madison

pfile@cs.wisc.edu, wwt@cs.wisc.edu

October 13, 1995

#### Abstract

This report describes *Vortex*, an Mbus module designed to provide hardware support for the Tempest parallel programming interface on clusters of Sun Sparcstation 10 and 20 workstations. The module consists primarily of two Field Programmable Gate Arrays (FPGAs), and two static RAM chips, both of commodity origin. Vortex is the only custom hardware needed for a distributed shared memory system, called *Typhoon-Zero*, which is currently in production and is intended to be a prototype for the proposed *Typhoon* DSM system. This report first presents background information on the Tempest interface and our decision to prototype Typhoon, then gives a description of the SPARC Mbus. Next the theory of operation for Vortex is given, followed by a comprehensive description of the Vortex architecture. Afterward, FPGA selection and design issues are discussed, as well as our design methodology for producing the Vortex module. Next, the logic and the printed circuit board implementation, verification and testing processes are described. Finally, CAD tool difficulties, timing problems and bugs encountered during the design process are described along with the solutions developed to address them. Verilog source code, printed circuit board schematics and other code are presented in the Appendices.

# Contents

| 1 | Background 1.1 Tempest                                            |            |       |      |     |       |     |     |     |     |     |   |     |   | 1<br>1   |

|---|-------------------------------------------------------------------|------------|-------|------|-----|-------|-----|-----|-----|-----|-----|---|-----|---|----------|

|   |                                                                   |            |       |      |     | • • • |     |     | • • | • • |     | ٠ |     | ٠ | 1        |

|   | 1.2 Fine-Grain Access Control                                     |            |       | • •  |     |       |     |     |     |     |     | • |     | • | 1        |

|   | 1.4 Typhoon-Zero and Vortex                                       |            |       |      |     |       |     |     |     |     |     |   |     |   | 1        |

|   | 1.4 Typhoon-zero and vortex                                       |            |       | •    |     |       |     |     |     |     |     |   |     | - |          |

| 2 | 2 Timeline                                                        |            |       |      |     |       |     |     |     |     |     |   |     |   | 4        |

| 3 | 3 Organization                                                    |            |       |      |     |       |     |     |     |     |     |   |     |   | 6        |

| 4 | 4 The SPARC Mbus                                                  |            |       |      |     |       |     |     |     |     |     |   |     |   | 6        |

|   | 4.1 MAD multiplexing                                              |            |       |      | • • |       |     |     |     |     |     |   |     | • | 6<br>7   |

|   | 4.2 Transaction Status Bits                                       |            |       |      | • • |       |     | • • |     |     |     | • |     | ٠ | 9        |

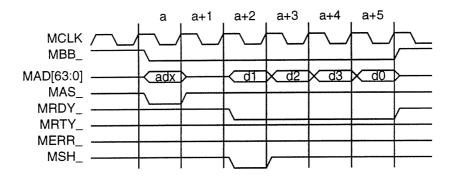

|   | 4.3 Wrapped Burst Transfers                                       |            |       | • •  | • • |       | • • | • • |     |     |     | • |     | ٠ | 9        |

|   | 4.4 Level-2 Mbus Commands                                         |            |       | • •  | • • |       |     | ٠.  |     |     |     |   |     | • | 10       |

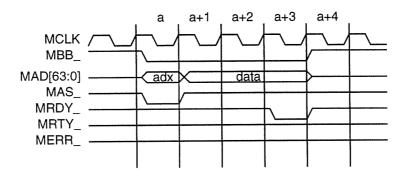

|   | 4.5 Mbus Timing Diagrams                                          |            |       | • •  |     |       |     | • • | • • |     | •   |   | • • | • | 10       |

| 5 | 5 Theory of Operation                                             |            |       |      |     |       |     |     |     |     |     |   |     |   | 10<br>11 |

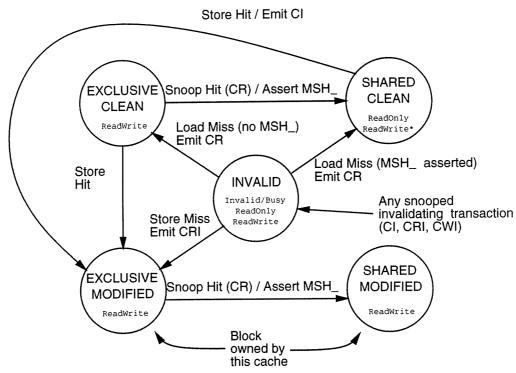

|   | 5.1 Fine-Grain Access Control                                     |            |       |      |     |       |     | • • | • • |     | •   |   |     | • | 11       |

|   | 5.1.1 Tempest Tag/Cache State Inc                                 | clusion .  |       | • •  |     |       |     | • • | • • |     | •   |   |     | • | 11       |

|   | 5.1.2 Enforcing Access Control                                    |            |       |      |     |       |     | • • |     | • • | •   | • |     | ٠ | 13       |

|   | 5.1.3 System Constraints on Enforce                               | ing Access | s Con | troi | • • |       |     |     | ٠.  | ٠.  | •   |   |     | • | 13       |

|   | 5.1.4 Support for Fine-Grain Access                               | s Control  | • • • |      |     |       |     |     | • • |     | •   |   |     | ٠ | 14       |

|   | 5.1.5 User Tag Shadow Space                                       |            |       |      |     |       |     |     |     |     |     |   |     |   | 14       |

|   | 5.1.6 System Tag Shadow Space 5.1.7 Coherent Invalidate Transacti |            |       |      |     |       |     |     |     |     |     |   |     |   | 15       |

|   |                                                                   |            |       |      |     |       |     |     |     |     |     |   |     |   | 15       |

|   | 5.2 Glue                                                          |            | • • • |      | • • | • • • | • • |     |     |     | •   |   |     | • | 15       |

|   | 5.2.1 Dispatching franciers 5.2.2 Cacheable Control Registers .   |            |       |      |     |       | •   |     | • • |     | •   | • | •   | • | 15       |

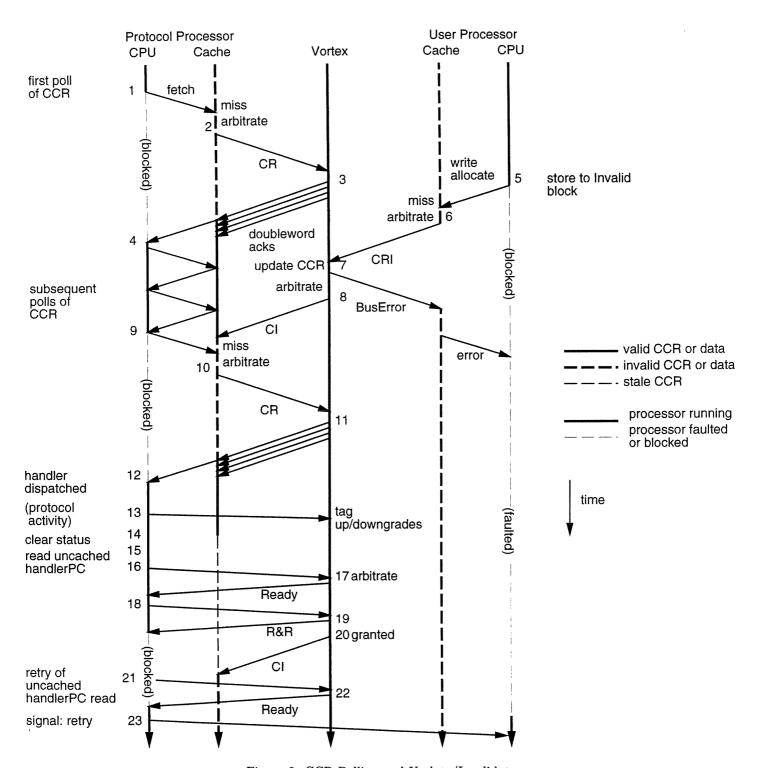

|   | 5.2.3 The handlerPC CCR                                           |            |       |      |     |       |     |     |     |     |     |   |     |   | 16       |

|   | 5.2.4 handlerPC example                                           |            |       |      |     |       |     |     |     |     |     |   |     |   | 17       |

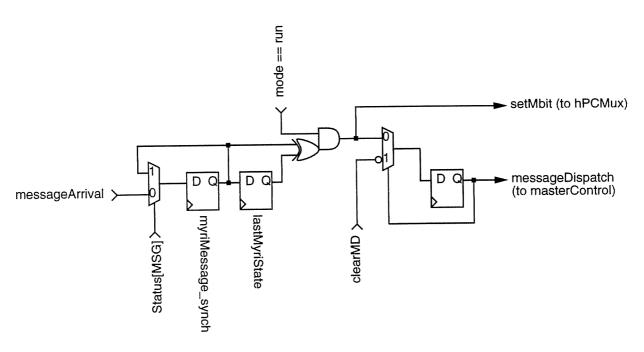

|   | 5.2.5 Network Support                                             |            |       |      |     |       |     |     |     |     |     |   |     |   | 19       |

| 6 | 6 Architectural Overview                                          |            |       |      |     |       |     |     |     |     |     |   |     |   | 20       |

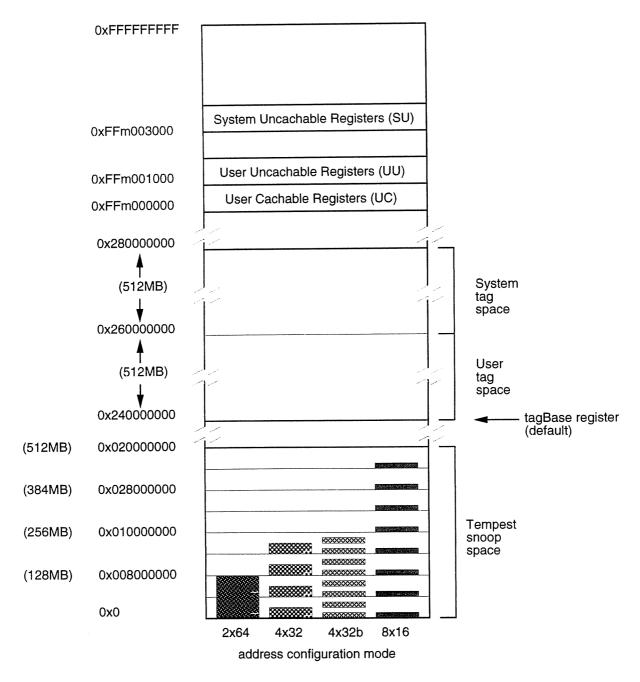

| U | 6.1 Mbus Memory Map                                               |            |       |      |     |       |     |     |     |     |     |   |     |   | 20       |

|   | 6.2 Tempest Snoop Space                                           |            |       |      |     | •     |     |     |     |     |     |   |     |   |          |

|   | 6.3 Tag Shadow Spaces                                             |            |       |      |     |       |     |     |     |     |     |   |     |   | 20       |

|   | 6.4 Control Register Spaces                                       |            |       |      |     |       |     |     |     |     |     |   |     |   | 22       |

|   | 6.4.1 User Cacheable Registers: bas                               | se OxffmO  | 00000 |      |     |       |     |     |     |     |     |   |     |   | 22       |

|   | 6.4.2 User Uncacheable Registers:                                 |            |       |      |     |       |     |     |     |     |     |   |     |   | 22       |

|   | 6.4.3 System Uncacheable Registers                                |            |       |      |     |       |     |     |     |     |     |   |     |   | 23       |

|   | 6.4.4 Register Descriptions                                       |            |       |      |     |       |     |     |     |     |     |   |     |   | 24       |

| 7 | 7 FPGAs and FPGA Design Issues                                    |            |       |      |     |       |     |     |     |     |     |   |     |   | 30       |

| • | 7.1 FPGA Selection Criteria                                       |            |       |      |     |       |     |     |     |     | . , |   |     |   | 30       |

|   | 7.1.1 Clock Speed                                                 |            |       |      |     |       |     |     |     |     |     |   |     |   | 31       |

|   | 7.1.2 Clock to Q delay                                            |            |       |      |     |       |     |     |     |     |     |   |     |   | 31       |

|   | 7.1.3 Drive Strength                                              |            |       |      |     |       |     |     |     |     |     |   |     |   | 31       |

|   | 7.1.4 Ground Bounce                                               |            |       |      |     |       |     |     |     |     |     |   |     |   | 31       |

|   | 7.1.5 Density                                                     |            |       |      |     |       |     |     |     |     |     |   |     |   | 31       |

|   | 7.2 FPGA Selection                                                |            |       |      |     |       |     |     |     |     |     |   |     |   | 32       |

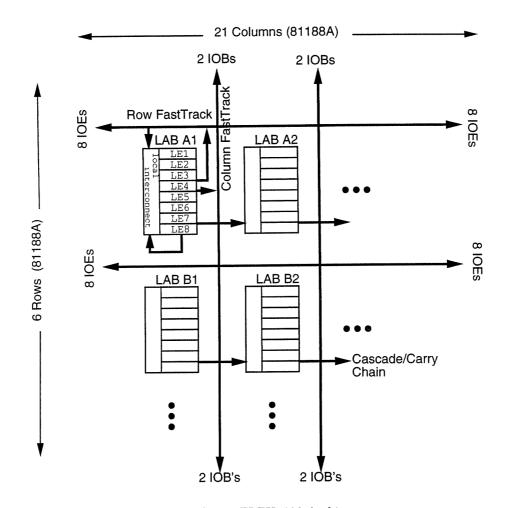

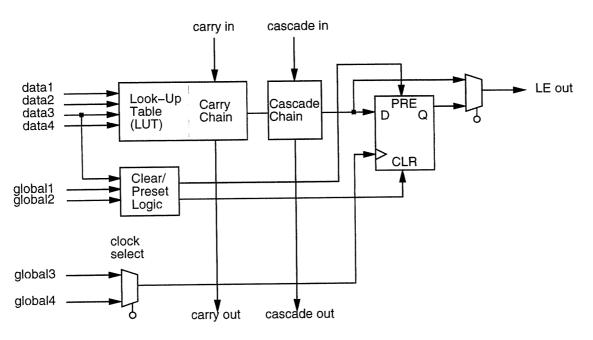

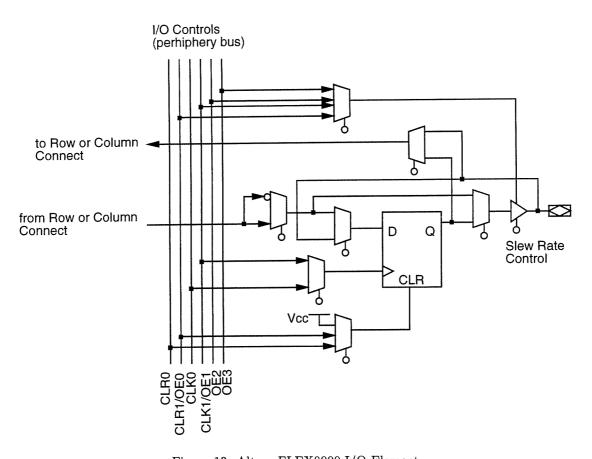

|   | 7.3 Altera FPGA Architecture                                      |            |       |      |     |       |     |     |     |     |     |   |     |   | 33       |

|   | 7.4 The Altera EPF81188ARC240-2                                   |            |       |      |     |       |     |     |     |     |     |   |     |   | 35       |

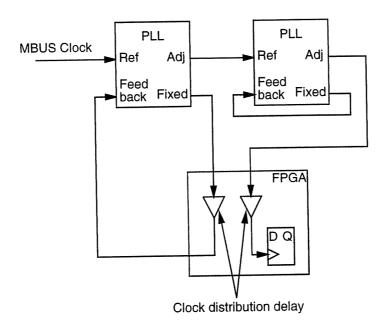

|    | 7.5                | Clockii  | ting Strategy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | •   |     |     |     | •   |     |     | 35 |

|----|--------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|----|

| 8  | Design Methodology |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     |     |     |     |     | 36  |    |

|    | 8.1                | Logic    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | . , |     |     |     |     |     | 36 |

|    |                    | 8.1.1    | C++ Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |     |     |     |     |     |     | 36 |

|    |                    | 8.1.2    | Verilog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |     |     |     |     |     |     | 37 |

|    |                    |          | Synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |     |     |     |     |     |     | 37 |

|    |                    | 8.1.3    | The second secon | •   | • • | • • | •   | 1   |     | •   | 37 |

|    |                    | 8.1.4    | FPGA Place and Route                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •   |     |     | • • | •   | •   | •   | 37 |

|    | 8.2                | Printe   | ed Circuit Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •   | • • | • • |     | •   | • • | •   | 31 |

| 9  | Impl               | lemen    | ntation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |     |     |     |     |     |     | 37 |

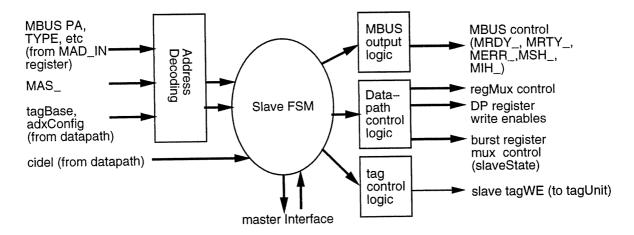

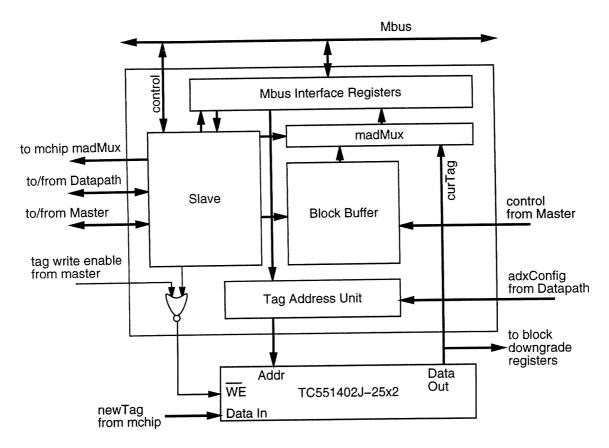

|    | 9.1                | Slave .  | ·<br>}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |     |     |     |     |     |     | 37 |

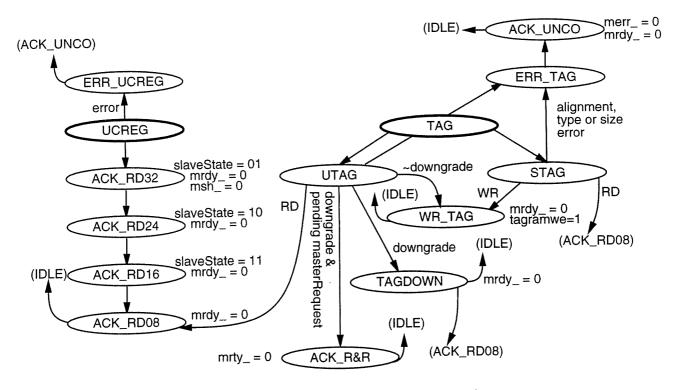

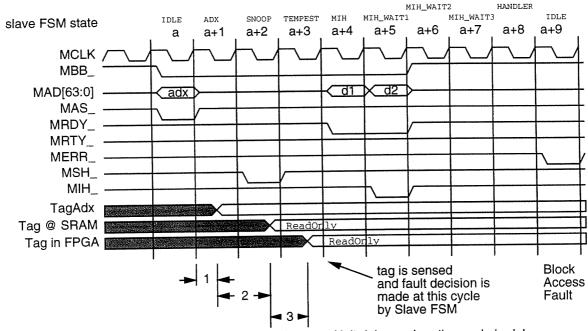

|    | _                  | 9.1.1    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     |     |     |     |     |     | 38 |

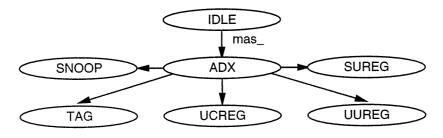

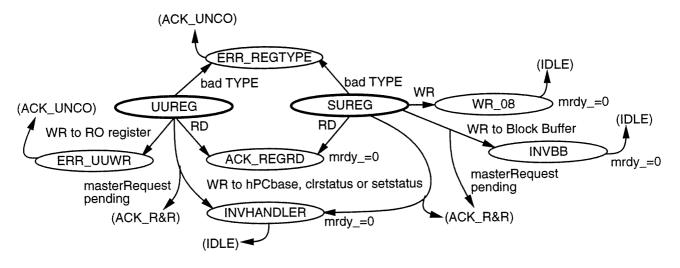

|    |                    | 9.1.2    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     |     |     |     |     |     | 41 |

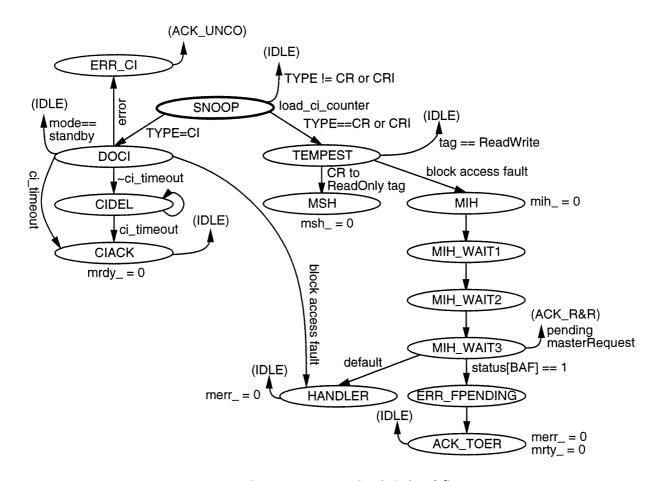

|    |                    | 9.1.3    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     |     |     |     |     |     | 41 |

|    |                    |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     |     |     | _   |     |     | 42 |

|    |                    | 9.1.4    | Slave Output Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | • • | •   | •   | •   |     | •   |     | 42 |

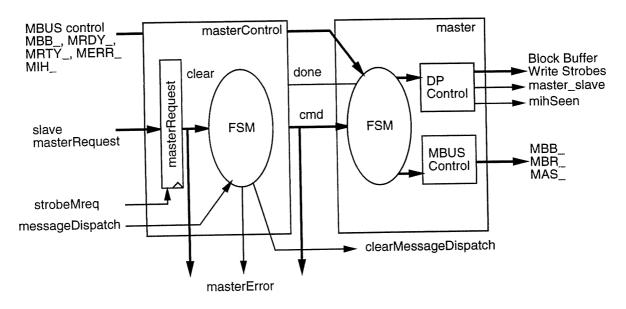

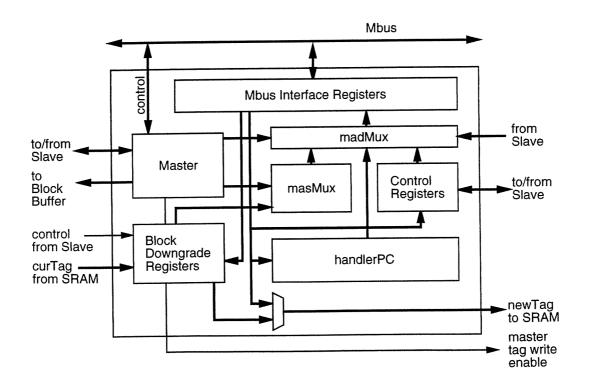

|    | 9.2                |          | ser                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |     |     |     | ٠   | •   | . • | 42 |

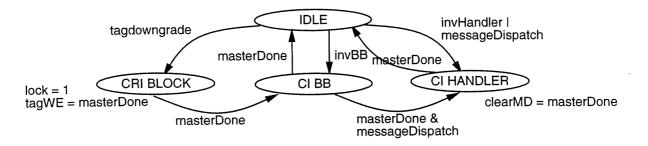

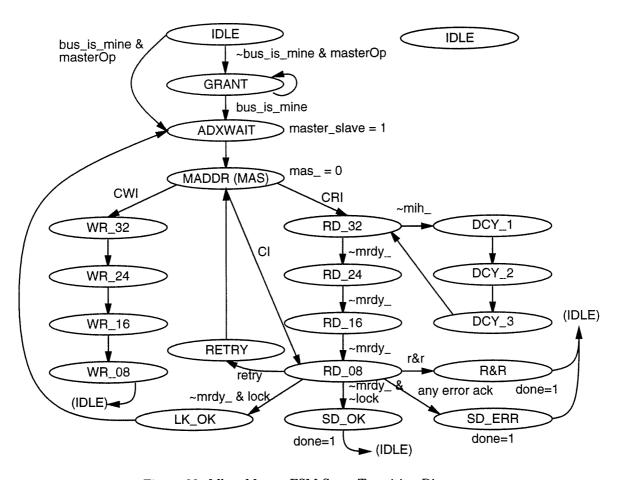

|    |                    | 9.2.1    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     |     |     |     |     |     |    |

|    |                    | 9.2.2    | master                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     | • • |     |     | •   | •   |     | 43 |

|    | 9.3                | Datap    | path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |     |     |     |     |     |     | 45 |

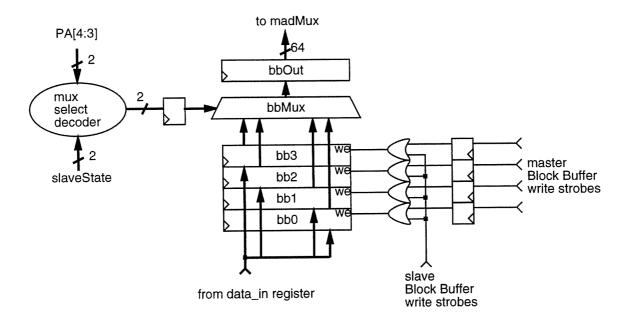

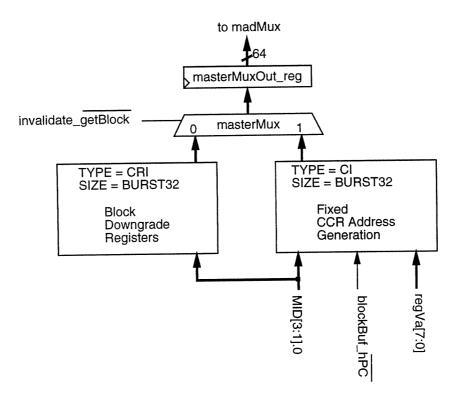

|    |                    | 9.3.1    | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |     |     |     |     |     |     | 45 |

|    |                    | 9.3.2    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     |     |     |     |     |     | 45 |

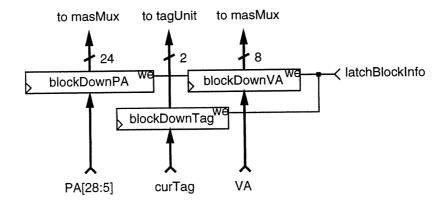

|    |                    | 9.3.3    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     |     |     |     |     |     | 46 |

|    |                    |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     |     |     |     |     |     | 46 |

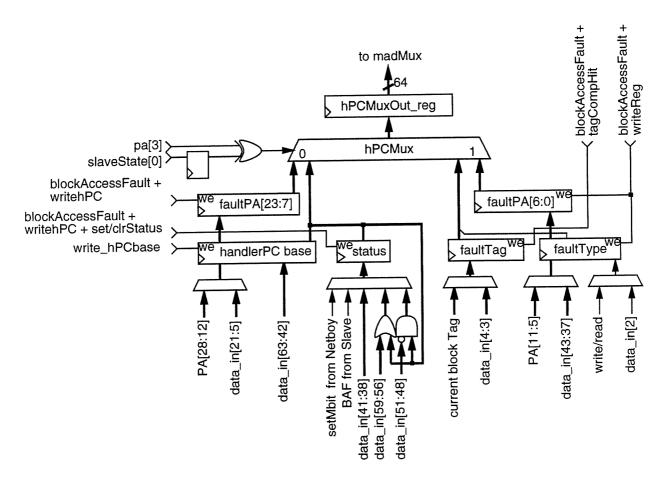

|    |                    | 9.3.4    | Ŭ -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |     |     |     |     |     |     | 48 |

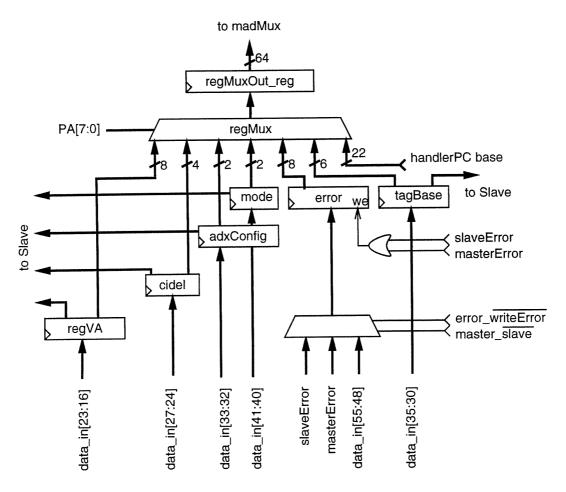

|    |                    | 9.3.5    | Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | • • |     |     |     | •   | •   | • • | 48 |

|    |                    | 9.3.6    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     |     |     |     |     |     | 50 |

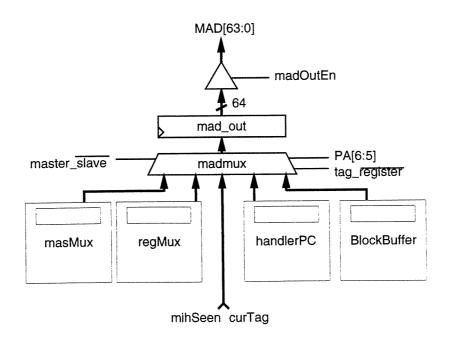

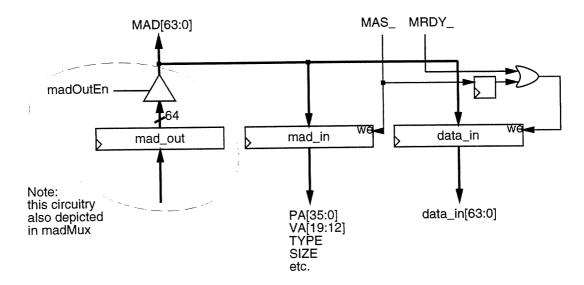

|    |                    | 9.3.7    | MAD Multiplexor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | • • |     | • • |     | •   | ٠   | • • |    |

|    | 9.4                | Tag A    | Address Unit (tagUnit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |     | • • | •   |     | •   |     | 50 |

|    | 9.5                | Mbus     | s Interface Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |     |     |     |     |     |     | 51 |

|    | 9.6                | Netbo    | ooy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |     |     |     |     |     |     | 51 |

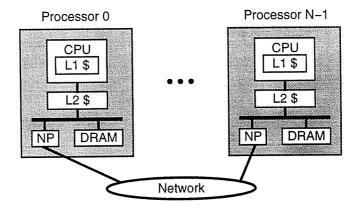

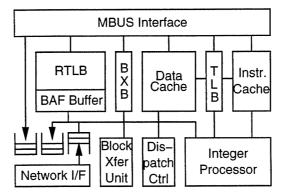

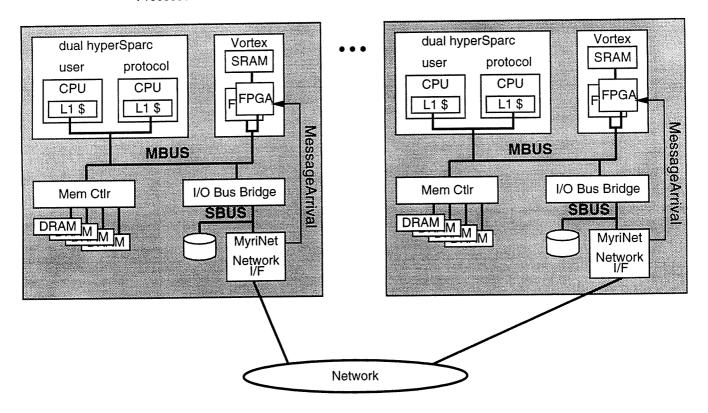

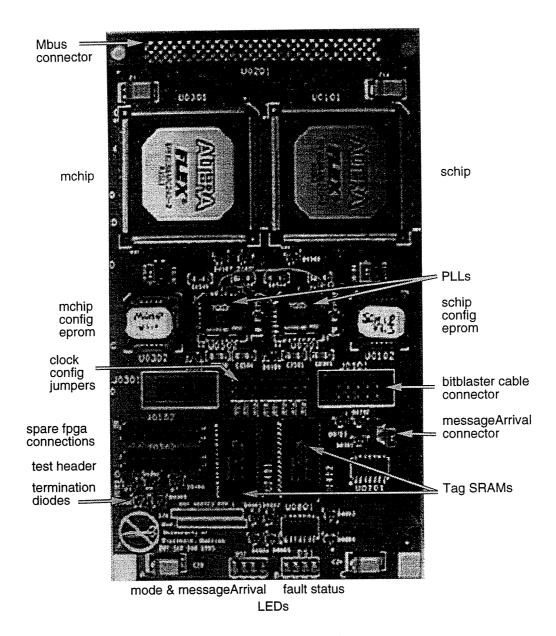

|    | 9.7                | Partit   | itioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |     |     |     |     | •   |     | 51 |