# A CHARACTERIZATION OF PROLOG EXECUTION

by

Mark Andrew Friedman

Computer Sciences Technical Report #1077

February 1992

# A CHARACTERIZATION OF PROLOG EXECUTION

by

# MARK ANDREW FRIEDMAN

A thesis submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

(Computer Science)

at the

UNIVERSITY OF WISCONSIN-MADISON

1992

#### **Abstract**

We analyze the execution of a new suite of medium-sized and realistic benchmarks through simulations on a general-purpose, register-oriented architecture at the abstract machine and architectural levels to identify the most critical characteristics of Prolog for efficient execution. We propose improvements through modest enhancements to the architecture and to the Warren abstract machine to add significant support for the identified issues. Architectural support for tag-handling operations through an architecture which distinguishes between the tag and value fields of an object leads to a twelve percent decrease in static code and a seven percent decrease in executed instructions. The addition of orthogonal tag instructions reduces code size by an additional nine percent and reduces dynamic instructions by eleven percent. The introduction of push and pop instructions decreases code size by seven percent and the number of instructions executed by eight percent. Static code is reduced by forty percent and the number of instructions executed decreases by nine percent by utilizing procedure argument mode information at compile time within compiled unification operations. Knowledge of dereferencing characteristics reduces static code by six percent and reduces instructions executed by six percent by eliminating dereferencing for objects which are directly referenced and when previously dereferenced values may be substituted for non-dereferenced objects. Optimization of arithmetic expression evaluation eliminates six percent of the executed instructions which create arithmetic expressions and eliminates seven percent of the executed instructions which evaluate these structures and decreases the static code size by ten percent. A modified WAM-database execution model is proposed which reduces static code by twenty percent with a modest four percent increase in executed instructions. We find Prolog to attain only modest speedups through simple pipelined and multiple-operation-issue machine implementations and propose new directions to explore to allow Prolog to better exploit the increasing levels of instruction-level parallelism attainable in modern architectures.

# **Table of Contents**

| Chapter 1. Introduction                                            |

|--------------------------------------------------------------------|

| 1.1 Logic Programming and Prolog                                   |

| 1.2 Overview of Research                                           |

| 1.3 Organization of Thesis                                         |

| 1.4 Original Contributions                                         |

| Chapter 2. Background                                              |

| 2.1 The Warren Abstract Machine                                    |

| 2.1.1 Data Objects                                                 |

| 2.1.2 Memory Areas                                                 |

| 2.1.3 Address Pointers                                             |

| 2.1.4 WAM Operations                                               |

| 2.1.5 Fundamental Operations                                       |

| 2.1.6 Built-In Predicates                                          |

| 2.1.7 Palindrome Example                                           |

| 2.2 Special Purpose Prolog Machines                                |

| 2.2.1 Tick's Pipelined Prolog Processor24                          |

| 2,2.2 The Programmed Logic Machine (PLM)                           |

| 2.2.3 The Personal Sequential Inference (PSI) Machine              |

| 2.3 Prolog RISC Implementations                                    |

| 2.3.1 Prolog on the Symbolic Programming Using RISC (SPUR) Machine |

| 2.3.2 The Logic Programming Windowed (LOW) RISC Machine            |

| 2.4 Global Prolog Compiler Optimizations                           |

| 2.4.1 Mellish, Debray, and Warren45                                |

| 2.4.2 The Aquarius Compiler                                        |

| 2.5 The Berkeley Abstract Machine (BAM) Processor48                |

| Chapter 3. Methodology                                             |

| 3.1 Methodology and Tools                                          |

| 3.2 Benchmarks                                                     |

| 3.2.1 Static Benchmark Characteristics59                           |

| 3.2.2 Dynamic Benchmark Characteristics                            |

| 3.2.3 Locality of Program Execution                                |

| 3.2.4 Memory Reference Characteristics                             |

| 3.3 Quality of the Benchmarks                                      |

| Chapter 4. WAM-Level Benchmark Characteristics                     |

| 4.1 Costs of WAM Operations and Built-In Predicate Operations      |

| 4.2 Costs of Fundamental Operations                                |

| 4.3 Enhancements through Mode Analysis and Global Optimization     |

| 4 4 In-line Expansion Enhancements                                 |

| 4.5 Summary of WAM-Level Enhancements                       | 88  |

|-------------------------------------------------------------|-----|

| Chapter 5. Architectural Benchmark Characteristics          | 90  |

| 5.1 High-Level Architectural Operation Profile              | 90  |

| 5.2 Low-Level Architectural Operation Profile               | 94  |

| 5.2.1 Architectural Opcode Profile                          | 94  |

| 5.2.2 Architectural Operand Profile                         | 98  |

| 5.3 Enhancements through Tag-Handling Architectural Support | 100 |

| 5.4 Enhancements through Stack Support                      | 103 |

| 5.5 Summary of Architectural-Level Enhancements             | 106 |

| Chapter 6. Instruction-Level Parallelism                    | 108 |

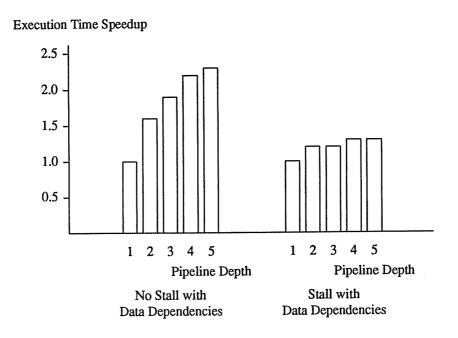

| 6.1 Pipelined Implementation Characteristics                | 111 |

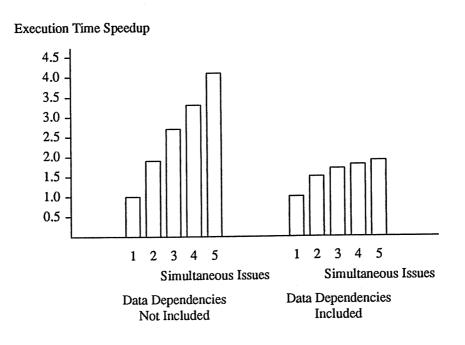

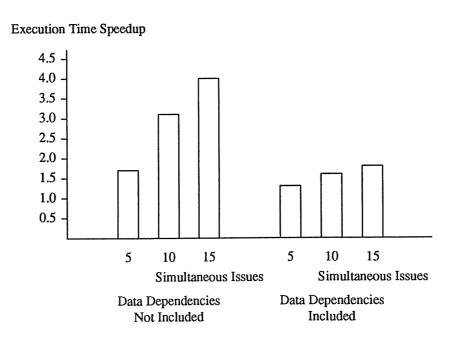

| 6.2 Multiple Operation Issue Implementation Characteristics | 113 |

| Chapter 7. Conclusions                                      | 116 |

| 7.1 Characterization and Optimization Results               | 116 |

| 7.2 Increasing Instruction-Level Parallelism                | 118 |

| 7.3 Conclusions                                             | 120 |

| References                                                  | 122 |

| Appendix A Representation of Fact-Intensive Programs        | 128 |

# **List of Figures**

| Figure 2.1. WAM Data Objects                                                        |    |

|-------------------------------------------------------------------------------------|----|

| Figure 2.2. WAM Memory Areas                                                        |    |

| Figure 2.3. WAM Environment                                                         |    |

| Figure 2.4. WAM Choice Point                                                        |    |

| Figure 2.5. Palindrome Prolog Operations                                            |    |

| Figure 2.6. Palindrome WAM Code                                                     | •  |

| Figure 2.7. The Data path of Tick's Prolog Processor Execution Unit                 | •  |

| Figure 2.8. Configuration of a PLM System                                           |    |

| Figure 2.9. PSI-II Address Translation Scheme                                       |    |

| Figure 2.10. PSI-II Data Processing Element                                         |    |

| Figure 2.11. LOW RISC System Organization                                           |    |

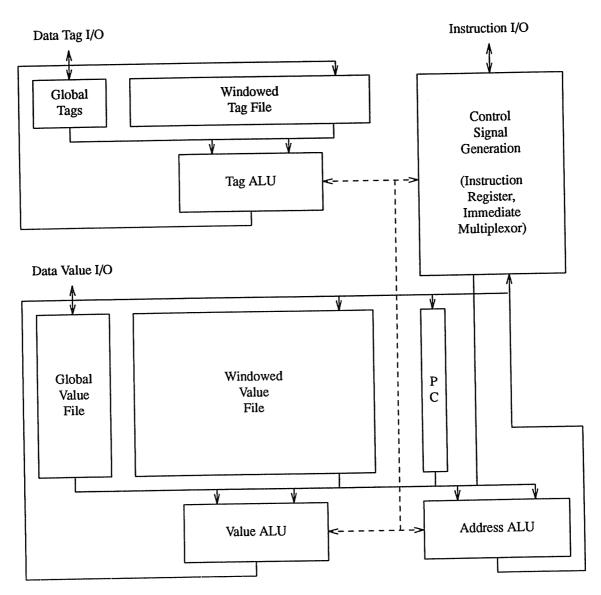

| Figure 2.12. LOW RISC Processor Organization                                        | •  |

| Figure 2.13. BAM Processor Organization                                             | •  |

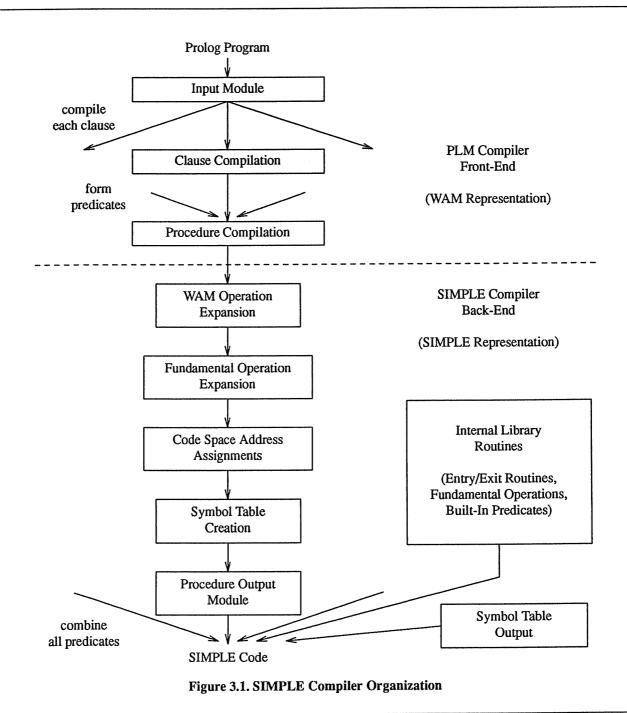

| Figure 3.1. SIMPLE Compiler Organization                                            | •  |

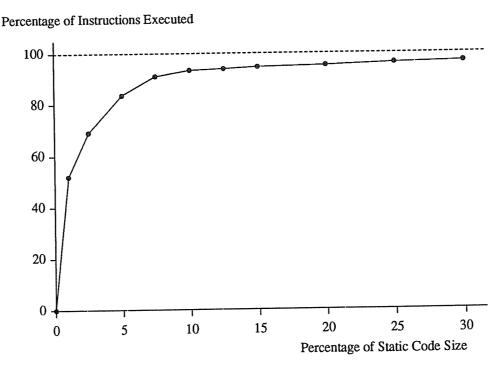

| Figure 3.2. Percentage of Instructions Executed within Most-Active Code             | •  |

| Figure 4.1. SIMPLE Instruction Sequence for the get_constant WAM Operation          | •  |

| Figure 4.2. Optimized Arithmetic Expression Evaluation                              | •  |

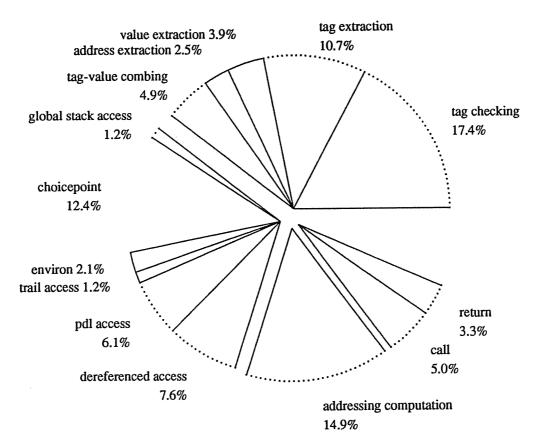

| Figure 5.1. Architectural Operations Dynamic Instruction Percentages                | •  |

| Figure 5.2. Tag-Handling Operation SIMPLE Instruction Sequences                     | •  |

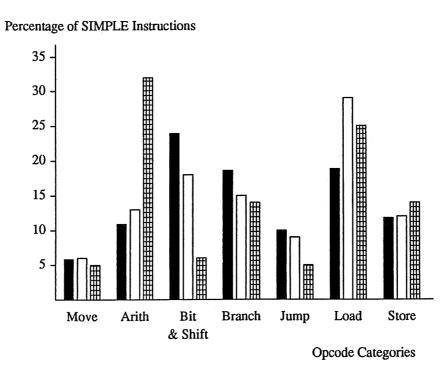

| Figure 5.3. Prolog (black), Lisp (white), and Pascal (checked) Instruction Profiles |    |

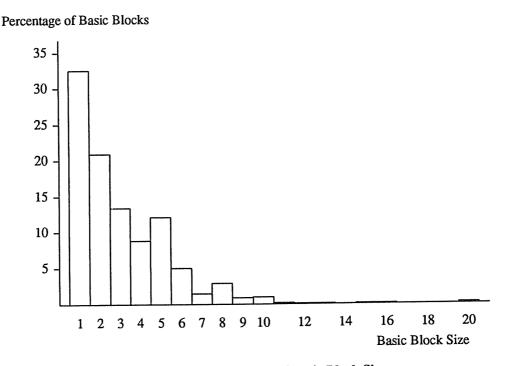

| Figure 6.1. Static Distribution of Basic Block Sizes                                | •  |

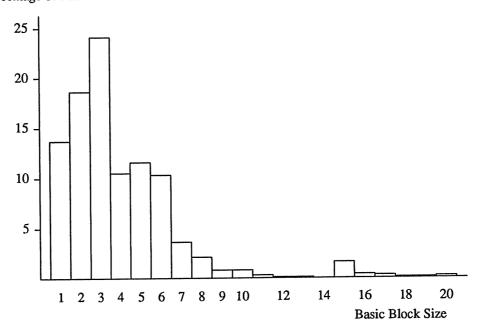

| Figure 6.2, Dynamic Distribution of Basic Block Sizes                               | •  |

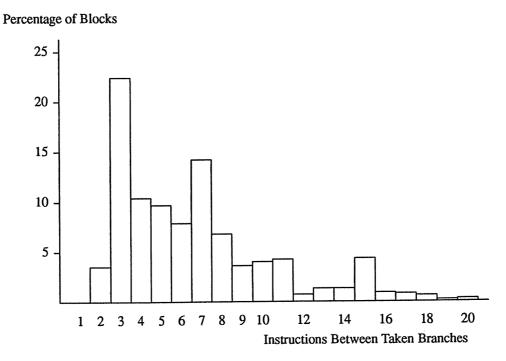

| Figure 6.3. Instructions Executed Between Taken Branches                            | •  |

| Figure 6.4. Speedups Through Pipelined Implementations                              | •• |

| Figure 6.5. Speedups Through Multiple Operation Issue (Arbitrary Operations)        | •• |

| Figure 6.6. Speedups Through Multiple Operation Issue (Partitioned Operations)      | •• |

| Figure A.1. SIMPLE Static Code Size for Fact Representation                         | •• |

| Figure A 2 Combined WAM-Database Fact Representation                                |    |

# **List of Tables**

| Table 2.1. WAM Operations                                                   | *******                                 |

|-----------------------------------------------------------------------------|-----------------------------------------|

| Table 2.2. Register Usage of SPUR PLM Implementation                        |                                         |

| Table 3.1. SIMPLE Static Instruction Sequence Length of WAM Operations      |                                         |

| Table 3.2. SIMPLE Static Code Size of Internal Library Routines             |                                         |

| Table 3.3. SIMPLE Instruction Set                                           | ••••••                                  |

| Table 3.4. Benchmark Summary                                                |                                         |

| Table 3.5. Static Benchmark Characteristics                                 | ********                                |

| Table 3.6. Rules, Facts, and Library Static Code Percentages                | •••••                                   |

| Table 3.7. Static and Dynamic SIMPLE Instruction to WAM Operation Ratios    | *************************************** |

| Table 3.8, Dynamic Benchmark Characteristics                                | *******                                 |

| Table 3.9. Rules, Facts, and Library Dynamic Instruction Percentages        | *************************************** |

| Table 3.10. Unexecuted Code Percentages                                     |                                         |

| Table 3.11. Benchmark Operand Reference Characteristics                     |                                         |

| Table 3.12. Benchmark Memory Usage Characteristics                          | **************                          |

| Table 3.13. Comparative Characteristics of Benchmark Suites                 | ******************                      |

| Table 4.1. WAM Operation Static Code Size Percentages                       | ********                                |

| Table 4.2. WAM Operation Dynamic Instruction Percentages                    | *************************************** |

| Table 4.3. Internal Routines Library Dynamic Instruction Percentages        |                                         |

| Table 4.4. Fundamental Operation Dynamic Instruction Percentages            |                                         |

| Table 4.5. Code Size Reductions Using Mode and Type Information             |                                         |

| Table 4.6. Performance Improvements Using Mode and Type Information         |                                         |

| Table 4.7. Performance Improvements Using Dereferencing Mode Information    | ,                                       |

| Table 4.8. Performance Improvements Using Optimized Arithmetic Evaluation   |                                         |

| Table 4.9. Performance Improvements with Optimal Built-In Configuration     | •••••                                   |

| Table 4.10. Performance Improvements with Optimal Fundamental Configuration |                                         |

| Table 5.1. Opcode Frequency Distributions                                   | ******                                  |

| Table 5.2. Dynamic Operand Reference Distribution                           | *******                                 |

| Table 5.3. Dynamic Memory Reference Distribution                            | ******                                  |

| Table 5.4. Code Size Reductions Using Tag Operation Support                 |                                         |

| Table 5.5. Performance Improvements Using Tag Operation Support             | *************************************** |

| Table 5.6. Performance Improvements Using Math Overflow Support             |                                         |

| Table 5.7. Performance Improvements Using Push / Pop Operations             | •••••                                   |

| Table 5.8. Performance Improvements Using Stack Overflow Support            |                                         |

| Table A 1 Performance Changes with WAM-Database Fact Representation         |                                         |

# Acknowledgements

I would foremost like to thank my advisor Professor Gurindar S. Sohi for his guidance, support and especially his understanding and patience during the years I have been under his supervision. I hope one day to gain the admiration and respect of my students to the degree I admire Guri for the dedication, persistance and the wisdom and values he brings to his profession.

I am grateful to the Univerity of Wisconsin-Madison for the research assistantship they provided to me during the 1989-1990 academic year. Were it not for the persistance of Professor Larry Landweber, it is unlikely I would have received the assistantship and it is *less* likely that I would have completed my degree! I thank Larry for the efforts he put forth in my behalf, his encouragement, his time and attention, and his invaluable advice.

I thank my dissertation committee members: Professors Ken Kunen, Mark Hill, Yannis Ioannidis and John Beetem for their time and helpful comments and Professor Jim Goodman for serving on my preliminary examination committee.

Peter Van Roy and Barry Fagin provided an early version of the PLM compiler and PLM simulator. Without the availability of their tools, inner details of the WAM would have remained mysterious. I am grateful to Van Roy, Fagin and the Aquarius project for providing their compiler and allowing me to incorporate it into my work.

The IBM Corporation, largely through efforts of Robert C. Moran, provided financial support during my first three years in Madison through the IBM Resident Graduate Fellowship Program.

I thank again Professor Jim Goodman and Professor Larry Travis for their support earlier on in the graduate program.

I am grateful to Bob Holloway for selecting me as an instructor and enjoyed our frequent conversations.

Teaching 302 was an invaluable experience and teaching has become my career.

To the many housemates, officemates, graduate students, undergraduates, faculty, staff, Madisonians, spouses, significant others, fraternity brothers, volunteers, and those that I've missed that I've had the fortune to meet during

six years in Madison, I say thanks and apologize for not listing each and every one of you. I would like to single out one thank you, not so much for the friendship he provided over the years, but for the request I make now. Marty, since you've worked so hard to organize so many of my affairs in the past, I was hoping you'd generate a list of the individuals referenced above and send them individual letters. *Thanks!*

And to my family and old friends, I should have a little more time for you now . . .

### **CHAPTER 1**

### Introduction

We believe Prolog to be an important foundation for future languages due to its very-high-level expressiveness, declarative style of programming, and inclusion of features not found in traditional, empirical programming languages. Prolog has proven useful in a variety of applications and has obtained a dedicated group of users in both research and in practice. Prolog will become increasingly useful as increasing numbers of symbolic applications emerge in future years.

The future of Prolog's success is dependent upon the existence of efficient Prolog implementations. Historically, Prolog implementations have been significantly less efficient (or perceived to be significantly less efficient) than necessary for practical use. Prolog's use of unification, backtracking and dynamic data structures create computational demands that continue to challenge the efficiency of its implementation. While in the past special-purpose Prolog machines, both complex microcoded machines and register-oriented, load-store instruction set architectures were designed that provided increased (but short-lived) Prolog performance, it is now difficult to justify the design of a Prolog-specific machine given that established load-store instruction set machines can provide Prolog performance of the same order of magnitude while serving general-purpose requirements as well. It is more difficult for the performance levels of language-specific machines to keep pace with the ever-increasing performance levels of general-purpose architectures that are driven by the momentum of procedural language implementations. Increasing the performance of Prolog systems is a continuing necessity to encourage the use of Prolog for applications which it is best suited.

It is the aim of our research to study the characteristics of Prolog execution and determine how these characteristics suggest improvements both at the abstract machine level and as modest modifications to established high-performance architectures to achieve increased Prolog performance with little impact on overall system performance. In particular, in this report we present a characterization of Prolog execution by measuring the occurrence and costs

of a variety of operations on a simple load-store architecture using a new set of benchmarks. Driven by our characterization study, we propose enhancements to the architecture and quantify performance improvements that would be realized through the implementation of these enhancements.

We begin our discussion by expanding upon the significance of our problem and the directions and approach of our research. We describe the organization of the remainder of this report. We list original contributions that we make to Prolog implementation research.

#### 1.1. Logic Programming and Prolog

Logic programming became the subject of increased attention when the Japanese Fifth Generation Computer Systems (FGCS) Project announced that Prolog would serve as the basis for its principal programming language [1]. The FGCS project succeeded in demonstrating that a framework of computer hardware and software could be constructed as a predicate logic machine. The achievements of FGCS include a hierarchy of logic programming languages, the development of a logic programming operating system, and the development of a family of logic programming machines [2-4]. The FGCS project stimulated similar programs in the United States [5-7] and created interest in logic programming throughout the world.

Logic programming is a programming paradigm founded on simple, first-order logic, yet it is powerful enough to facilitate the development of advanced applications [8-10]. This idea was first explored by Kowalski and Colmerauer in the early 1970's [11, 12]. Prolog is the most popular logic programming language. Introductions are provided in tutorials by Clocksin and Mellish [13], and Sterling and Shapiro [14], and in a pictorial overview by Colmerauer [15]. The language is especially suited for symbolic programming in natural language analysis, artificial intelligence, and database applications, as well as for applications such as compiler writing [16], algebraic manipulation, and theorem proving. Successful examples of Prolog's use are in natural language understanding [17-20], expert systems [21-23], knowledge representation [24], the automatic generation of plans [25], database design [26, 27], expert database systems [28-30], and computer aided design (CAD) [31-34].

Programming in Prolog is distinguished from programming in conventional languages in that Prolog is a declarative language. Prolog programmers describe known facts and relationships within the domain of the problem they wish to solve, together with a query defining the problem. Programmers are freed from the task of prescribing

the exact sequence of operations needed to solve a problem as they must do in imperative languages. A more accurate description of the activity of "programming" in Prolog is "the development of logical specifications of the knowledge within a particular domain that is necessary to solve a problem".

When a computer carries out the computation of a Prolog program, the sequencing of the computation is determined by the internal inference mechanisms of the Prolog system. Prolog searches through the originally supplied set of facts and relationships and applies them to attempt to solve a problem. This ability to automatically support the computation process is based on the principles of unification and resolution discovered by Robinson [35].

Resolution is a rule of inference of first-order predicate logic. It can be used to determine how one formula (in Prolog's case, a conjunction of subproblems of the original problem) is logically derived from a set of other formulae (in Prolog's case, a larger problem to be solved and the facts and relationships supplied by the programmer). Prolog uses resolution to break the originally defined problem into smaller subproblems, and these subproblems into still smaller subproblems, until the system arrives at a set of subproblems for which answers can be obtained immediately from the set of programmer-supplied facts.

Unification is a generalized pattern-matching mechanism applied to a set of formulae that constructs more specific versions of these formulae so that resolution can be applied. During unification, terms within the formulae are matched and made "identical" by instantiating variables within the terms to specific values. It is within this process that data structures are created as a solution is obtained to the program's problem.

An introduction to first-order predicate calculus and resolution-based theorem proving can be found in Nilsson [36]. Mathematical questions regarding the properties of Prolog's procedural meaning with respect to logic are analyzed by Lloyd [37]. In the remainder of this thesis, we refrain from discussing theoretical aspects of logic programming.

The characteristic that gives Prolog it's primary advantages over procedural languages is the separation between its logical and control components. This characteristic results in its declarative nature and a separation of the two chief concerns during program development: the correctness and the efficiency of a program. The Prolog programmer is better able to address the concerns of correctness and verification because the concerns of efficiency are lower-level details left to the implementer of the Prolog system. The powerful pattern-matching scheme of unification gives Prolog the ability to easily create, compare, search, and manipulate complex data structures.

Declarativeness, combined with the ease of use of arbitrary data structures, results in a very-high-level programming language where the programmer is able to express ideas in terms of objects and entities in the language of his problem's domain. The relative independence of the facts and relationships that the programmer supplies makes Prolog well suited for incremental development and program maintenance. All of these features combine with the conciseness of Prolog to make it an ideal language for rapid prototyping. In all, Prolog is an important foundation for future languages.

Unfortunately, the earliest Prolog systems, implemented as interpreters [11], executed slowly and required unacceptable amounts of working storage. The unavailability of fast computers with large main memories and the unavailability of optimizing compilers hindered the establishment of Prolog as a practical language. The development of Prolog was slowed by an absence of interesting examples to demonstrate its novelty and the existence of better compilers and environments for the then more mature language Lisp that had proven its value in symbolic processing. The development of the first Prolog compiler by Warren [38] and his later refined definition of an abstract Prolog instruction set and memory organization [39] provided the first steps toward efficient Prolog implementation. Several research efforts followed exploring the design of special-purpose, high-performance processors that directly implemented the instruction set of Warren's abstract machine [40-42]. As the trends of conventional language architecture design moved to that of reduced-instruction-set-computer (RISC) technology, Prolog architecture researchers looked to improve Prolog through RISC implementation techniques [43, 6, 44-48]. Recently, researchers have begun investigating techniques of global optimization specifically suited for Prolog compilation [49-53]. The most recent and promising Prolog implementation, the Berkeley Abstract Machine (BAM) [7], coupled with the Aquarius compiler [54, 55], combines a RISC architecture with a global optimizing compiler.

Despite advancements in the development of Prolog systems, the current techniques employed to implement the language and more specifically, the effects of the implementation of dynamic data structures, dynamic typing, searching mechanisms, and the process of unification create heavier computational demands than desirable (that is, long execution times and large space requirements when compared with other languages). The characteristics of Prolog create computational needs different from other languages. (Dynamic data structures and dynamic typing are features not commonly found in procedural languages. Searching mechanisms and the process of unification are not

built into either procedural languages nor functional languages.) It is relatively recently that researchers in the fields of computer architecture and compilation theory have joined researchers in logic programming to address these unique requirements. We expect that with continued research such as the work we present in this thesis that Prolog systems will offer performance comparable to other languages making logic programming languages the definitive choice for those applications that they suit best.

### 1.2. Overview of Research

Our research centers on discovering and quantifying implementation improvements that lead to more efficient processing of programs written in Prolog. Our work has been in three directions. First, we performed a comprehensive, bottom-up characterization of Prolog programs by exploring the frequency of occurrence of different operations and computing the costs of these operations as the count of instructions executed on a simple load-store architecture for a set of benchmarks representative of typical Prolog programs. Our analysis provides a foundation for the development of future Prolog systems. It is more complete (in terms of the quality of benchmarks, the amount and presentation of fundamental statistics, and the precision of cost calculations) than any work that has been presented of which we are aware. We compare our measurements to Prolog profiles reported by others [5, 56, 57] and to studies of other languages [58-61] when these comparisons lend insight towards implementing Prolog efficiently.

The study of operational characteristics of programs written in high-level programming languages leads to information that can be used to detect inefficiencies in the implementation of programming languages and suggest possible improvements in their design. The second portion of our work identifies issues related to the abstract machine model and to computer architecture that are most critical for efficient Prolog execution by drawing from our characterization of Prolog. We propose or reference alternate implementation and enhancement techniques for these issues. We present comparative performance analyses to quantify the improvements gained through these techniques by our benchmarks. Our results are useful to compiler and interpreter designers who wish to implement Prolog on an existing machine and to architects who are looking to add hardware support to improve Prolog performance especially on modern load-store architectures.

The final portion of our work is the beginning of future research into exploiting instruction-level parallelism.

We have measured the parallelism and speed-up that would be achieved in implementations of Prolog using a simple

pipelined machine model and using a simple multiple-operation-issue machine model. We propose new directions to explore that may allow Prolog to fully exploit the increasing levels of instruction level parallelism attainable in modern pipelined and multiple-operation-issue architectures.

Our results are obtained using a new set of eleven benchmarks that include examples from artificial intelligence, natural language analysis, text processing, compiler technology, database technology, number theory, and linear algebra. The benchmarks we have developed are considerably larger and more representative of real applications than benchmarks that predominantly appear in the literature [38, 5, 7].

We have developed the Simple Instruction Set Machine for Prolog Execution (SIMPLE) to generate our results. The SIMPLE system includes an architectural specification, a compiler, and a simulator. The front-end of our compiler is the Programmed Logic Machine (PLM) compiler developed by Van Roy at Berkeley [62] that translates Prolog code into a representation of the Warren Abstract Machine (WAM). The back-end of the SIMPLE compiler implements the WAM model using the instruction set, register set, and memory organization of the SIMPLE architecture. The simulator emulates SIMPLE instructions and generates an extensive set of static and dynamic statistics and instruction and memory reference traces.

SIMPLE is a load-store, register-oriented instruction set architecture. Only load and store operations access memory. Operands of other instructions are immediate values or are contained within registers. The SIMPLE architecture is similar to many modern register-oriented computers [44-46] in that the operations and addressing modes within its small instruction set are the single-cycle, fixed-size, fixed-format instructions that form the core of these machines. Our work supports the philosophy of reduced-instruction-set-computer (RISC) design in that we have selected a minimal set of essential instructions suitable for fast hardware execution as our architectural base. Suggested enhancements involve small modifications to the instruction set that are justified by their frequency of use and non-disruptive to the overall performance and optimizations at the abstract machine level that lend synergy to the architecture. The RISC approach has been very beneficial to conventional architecture design [63, 64]. As we have seen in recent Prolog developments [6, 7], application of similar design techniques targeted to Prolog lead to results that are as profitable. Because our architecture is similar to existing machines and because its instructions are easy to understand, our results are readily applied to the design of other machines.

#### 1.3. Organization of Thesis

The organization of the remainder of this thesis is as follows. In chapter 2, we provide background information on other researchers' work on implementations of Prolog dividing these efforts into five areas: Warren's abstract machine model of Prolog execution, special-purpose Prolog machines, reduced-instruction-set-computer implementations of Prolog, global optimizations for Prolog compilation, and the most recent development, the Berkeley Abstract Machine [7]. We briefly overview the Warren Abstract Machine [39]. We survey Tick's overlapped Prolog processor [65], the Berkeley Programmed Logic Machine (PLM) [41], and the Fifth Generation Computer Systems Project's Personal Sequential Inference machines (the PSI-I and PSI-II) [66, 42]. We review the work that generated interest in Prolog RISC architectures by the Symbolic Processing Using RISC (SPUR) group [43] and the LOW RISC group [6]. We discuss global analysis compiler techniques on automatic mode determination [49, 51] and on automatic detection of determinism [50, 52]. We review the Aquarius compiler [55] and the Berkeley Abstract Machine (BAM) processor [7],

Chapter 3 contains a presentation of our research methodology, tools and benchmarks. We describe the SIM-PLE architecture, the organization of the SIMPLE compiler, and the use of SIMPLE to emulate the Warren Abstract Machine. We discuss the use of the SIMPLE simulator in obtaining statistics and the compilation of our measurements into results. We introduce our benchmark suite and characterize their static code characteristics, dynamic code characteristics, and memory usage.

The results of our characterization study, and a discussion and analysis of techniques to enhance critical aspects of a Prolog implementation are contained in chapters 4 and 5 separated into a WAM-level profile and an architectural-level study. Chapter 4 examines the costs of executing WAM operations and the costs created by Prolog's built-in predicate routines and evaluates the costs of operations fundamental to a WAM implementation. Chapter 5 reports on architectural operations including higher-level operation frequencies (for example, tag handling, procedure calls, and accessing different memory areas) and lower-level architectural statistics (for example, instruction frequencies, distribution of operand and addressing use, and patterns of memory usage).

As benchmark characteristics are presented and important issues are identified, we present performance analyses of alternate implementation techniques. We discuss architectural support for tag-handling, performance improvements through compile-time mode and type determination, elimination of redundant dereferencing

operations, in-line expansion of fundamental operations and built-in predicate routines, evaluation of arithmetic expressions, support of last-in, first-out stacks, and the representation of fact-intensive programs.

Chapter 6 presents our preliminary instruction-level parallelism results that form the basis for future work. We report the instruction-level parallelism and speed-up obtained from executing our benchmarks on a pipelined machine model and on a multiple-operation-issue machine model and propose directions for future exploration of performance improvements.

Prolog architectural research has evolved from the design of special-purpose WAM instruction set machines to the tuning of register-oriented, general-purpose architectures coupled with compilers that expose and optimize the inner details of WAM operations through global and special-case analysis. In chapter 7, we conclude that our work advances this trend that has proven beneficial. By analyzing architectural-level details to identify striking or noticeably different characteristics of a benchmarked simulation, one can propose and quantify improvements for modest enhancements to an architecture and adjustments to the abstract machine model to add significant support for Prolog on general-purpose, load-store instruction set machines. The need for such analysis continues as general-purpose architectures involve and Prolog systems strive to compete with conventional language performance by exploiting new enhancements. We suggest techniques directed at exposing instruction-level parallelism as an area for future work using our approach.

We include one appendix. Appendix A describes a technique to reduce the very large static SIMPLE code size of fact-intensive programs with a modest decrease in performance. While this technique relates to our overall work, it does not fit neatly into the flow of the main body of this report.

In the remainder of this report, we assume the reader is familiar with Prolog: the terminology and the use of the language. We assume the reader is familiar with Prolog's inference mechanism, specifically the methods of unification and resolution and their application in the depth-first, left-to-right goal selection search carried out by Prolog (SLD-resolution) and implemented through backtracking. An appreciation of how an interpreter executes a Prolog program would be sufficient depth for understanding our presentation. For a review of this material and the terminology that we use, the reader is referred to Clocksin and Mellish [13].

#### 1.4. Original Contributions

The main original contributions that we add to research in Prolog implementation are as follows:

- Our characterization study is of value to a wide range of researchers including those interested in Prolog abstract machine models, Prolog compiler design, and Prolog architectures. Other researchers have used similar types of information in their work. We know of no single report that characterizes Prolog as completely, that covers as many viewpoints, and that utilizes as interesting a set of benchmarks. Furthermore, no research of that we are aware has reported the characteristics of Prolog from the viewpoints of locality of code, non-executed code, high-level architectural operations, and the use and properties of built-in predicate routines.

- (2) We introduce a new set of Prolog benchmarks that are larger and more realistic than benchmarks that have appeared in the literature.

- (3) We introduce tag-handling support to our architecture altering the semantics of the instruction set so that the architecture recognizes that Prolog objects consist of both a tag field and a value field. Research in the design of the Berkeley Abstract Machine (BAM) architecture has suggested similar instructions to improve performance [7].

- (4) We investigate the behavior of our benchmarks to determine how much improvement may be achieved through global analysis compiler techniques for a variety of optimizations. Mellish [49], and Debray and Warren [51] have developed methods that automatically determine mode information and determinism. We analyze no specific techniques but instead use a reverse engineering scheme to determine the potential performance improvements that can be achieved through such techniques for specific benchmarks.

- (5) We recognize the importance and costs of built-in predicates and observe our benchmarks' behavior to determine the maximum benefits that could be achieved in these operations from global optimization techniques. Specifically, we suggest improvements in the compilation of built-in math predicate routines to increase performance and decrease memory requirements.

- (6) Our study of instruction-level parallelism begins work in determining what low-level parallelism is available in the execution of Prolog programs. There have been no reported studies of this type specific to Prolog.

(7) We propose a combined WAM-database model of execution to significantly reduce the size of fact-intensive benchmarks resulting in only a modest increase of executed instructions.

Our results have been generated through our own work. We have developed all of our own tools with the exception of the front-end of our compiler. A significant amount of time was spent developing the back-end of the compiler and optimizing the sequences of SIMPLE instructions that emulate WAM operations. A significant amount of time was spent developing the simulator that includes debugging and statistic generation capabilities. We spent a significant amount of time gathering and modifying our benchmark code to produce a diverse and realistic set of examples.

#### **CHAPTER 2**

## **Background**

#### 2.1. The Warren Abstract Machine

Prolog originated in the 1970's through efforts by Robert Kowalski and his expertise in logic and automatic theorem proving [11], Alain Colmerauer and his interests in natural language processing [12], and Phillipe Roussel and his work in implementing Prolog systems. Early Prolog interpreters were not favorably received due to their slowness and large storage requirements. It was David H. D. Warren's thesis work developing a Prolog compiler that led to the acceptance of Prolog and established the basis for practical systems [38, 67]. Warren refined his ideas and developed an "abstract Prolog engine". Known as the Warren Abstract Machine (WAM) [39], this model has become the standard for implementing Prolog systems. The Warren Abstract Machine defines an abstract instruction set and memory organization. The WAM description which follows includes details and enhancements to Warren's original definition which were incorporated as part of the Programmed Logic Machine (PLM) [41].

In the WAM, each predicate of a Prolog program is compiled into a single procedure. A Prolog goal is interpreted as a procedure call with the arguments of the goal serving as the arguments of the procedure call. The execution of a goal is the execution of the procedure of the predicate determined by the goal's principle functor and arity.

A procedure contains code for each of its predicate's clauses. The head of each clause becomes an entry point into the procedure. The code for each clause executes a series of tests and assignments to unify the arguments passed to the procedure with the terms and variables defined in the head of the clause. If the unification of all arguments succeed, a sequence of procedure calls then follow to execute the subgoals in the clause's body. If each of the subgoals executes successfully, the procedure returns to its caller.

If unification of the procedure arguments fails, or if all alternate clauses of a subgoal of the procedure fail, a backtracking routine is initiated which considers the next clause of the procedure. Each procedure contains code to assist the backtracking mechanism. When a procedure is first called, the arguments passed to the procedure are

saved before other code is executed. Also saved, is the next alternate clause to be tried should backtracking become necessary. When backtracking occurs, the procedure arguments are restored to their original values and the next alternate clause is executed. The alternate clause information must also be updated to the clause which follows the newly selected clause. When the last clause of a procedure is to be executed, backtracking information is no longer needed and is discarded.

#### 2.1.1. Data Objects

In the WAM, a Prolog object is represented by a word containing a tag and a value. The tag distinguishes the type of an object. The main types are unbound variables, references (or bound variables), constants, structures, and lists. An object's tag field assists in cdr-coding and garbage collection.

Figure 2.1 shows typical representations for these data objects. Both variables and references contain a variable tag. The value of a variable is a memory reference to itself while the value of a reference addresses the object to which it refers. Constants contain a constant tag, a secondary tag to distinguish between atoms, integers, and nil, and an immediate value or symbol table address. Structures and lists contain an appropriate tag and a pointer to the first of their sequence of elements. For structures, the first element of this sequence is the constant specifying its functor. The structure's arguments occupy successive locations in memory terminated by nil. For lists, elements may occupy consecutive memory locations or the list may be broken in pieces which are chained through cdr-coding [41]. In cdr-coding, a location which contains a list tag with the special cdr-bit set to one serves as a continuation pointer to the next piece of the list. A list is terminated by nil. A list may also be "non-terminated" by a variable element containing a set cdr-bit. Such a list may continue to grow as the execution of a program proceeds.

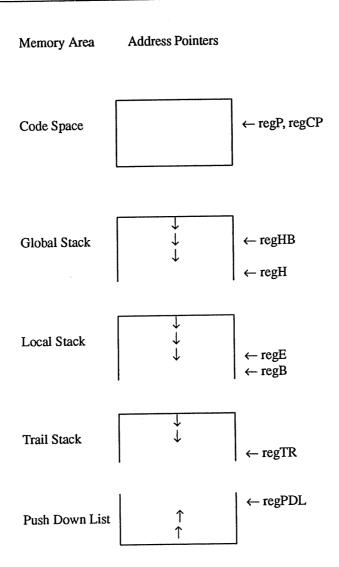

#### 2.1.2. Memory Areas

The WAM contains five memory areas divided among a code and data space. The code space contains instructions and other information representing the program. The four data space areas are accessed as stacks. These are the local stack, the global stack, the trail, and the push-down list (PDL). These stacks generally grow with each procedure invocation and contract on procedure return or on backtracking.

The global stack contains all the structures and lists created by unification and procedure invocation. It is analogous to the heap in procedural languages.

|                                 | Address    | Tag                | Value    |

|---------------------------------|------------|--------------------|----------|

| variable: X                     | 100        | variable           | 100      |

| reference to next object        | 200        | variable           | 300      |

| constant: 32                    | 300        | constant (integer) | 32       |

| structure: foo(Y)               | 400        | structure          | 450      |

|                                 | 450        | constant (atom)    | "foo"    |

|                                 | 451        | variable           | 451      |

|                                 | 452        | constant (nil)     | nil      |

| list: [123,bar,321]             | 500        | list               | 550      |

|                                 | 550        | constant (integer) | 123      |

|                                 | 551        | constant (atom)    | "bar"    |

|                                 | 552        | list (cdr set)     | 570      |

|                                 | 570        | constant (integer) | 321      |

|                                 | 570<br>571 | constant (nil)     | nil      |

|                                 | 3/1        | Constant (III)     | 1111     |

| non-terminated list: [foobar X] | 600        | list               | 650      |

|                                 | 650        | constant (atom)    | "foobar" |

|                                 | 651        | variable (cdr set) | 651      |

Figure 2.1. WAM Data Objects

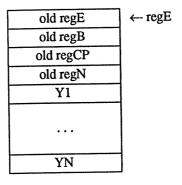

The local stack contains environments and choice points. Environments hold storage and control information for individual clause invocations. Variables within a clause are classified as either permanent or temporary. Permanent variables are those which must survive across procedure calls. The permanent variables of a clause are stored in its environment. Environments also contain a "continuation" which holds information specifying how to proceed after the execution of the clause completes. Environments correspond to the procedure activation records of procedural languages.

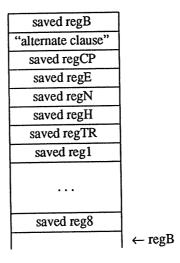

Choice points contain the information necessary to return to an earlier state of computation when backtracking. When a procedure is entered which contains more than one clause to be tried, a choice point is created. The choice point contains the original values of the procedure arguments, the address of the next alternate clause, and the values of several pointers to memory described in the next section. Choice points are unique to logic programming languages. The deterministic nature of imperative languages eliminates the need for an equivalent structure.

The trail area contains locations of variables which have been bound during unification and which must be unbound on backtracking to restore a previous state. This area is also unique to logic programming languages.

The push-down list is a small scratch area which assists in unification and in the implementation of built-in predicate routines.

#### 2.1.3. Address Pointers

The state of a Prolog computation is defined by a set of address pointers to memory. These include a program counter (regP), a continuation program pointer (regCP), pointers to the current environment (regE) and the current choice point (regB), pointers to the top of the global stack (regH), the top of the trail stack (regTR), and the top of the push-down list (regPDL), and a pointer to the global stack backtrack point (regHB). The state of the computation also includes the current procedure argument values and the values of the procedure's temporary variables. Typically, WAM implementations share a single set of resources to store these values (reg1 - reg8).

Figure 2.2 shows the layout for the WAM memory areas, the directions in which the stacks grow, and the WAM address pointers into each area.

In figure 2.3 the information contained in an environment is displayed which includes the previous contents of WAM address pointers and storage for permanent variables (Y1 - YN).

Figure 2.4 shows the information which is saved within a choice point. This includes the procedure arguments and temporary variable values, WAM address pointers, and the alternate clause address.

#### 2.1.4. WAM Operations

Prolog programs are encoded as sequences of instructions which execute WAM operations. Generally, compilation translates each symbol of a Prolog program (for example, constants, variables, functors, and operators) into a

Figure 2.2. WAM Memory Areas

Figure 2.3. WAM Environment

Figure 2.4. WAM Choice Point

WAM operation. WAM operations, summarized in table 2.1, can be classified into compiled-unification, procedural, choice point, and switch operations. Each clause of a program is constructed from compiled-unification and procedural operations. Clauses are linked into procedures with choice point and switch operations. Procedural operations accomplish the sequencing between Prolog procedures.

#### **Unification Operations**

get variable Yi, Aj get\_variable Xi,Aj get\_value Yi,Aj get value Xi, Aj get\_atom S,Aj get integer I,Aj get\_nil Aj get\_list Aj get\_structure F,Aj put\_variable Yi, Aj put\_variable Xi,Aj put\_value Yi,Aj put\_value Xi,Aj put\_atom S,Aj put integer I, Aj put\_nil Aj put\_list Aj put\_structure F,Aj put\_unsafe\_value Yi,Aj unify\_void N unify\_variable Yi unify variable Xi unify\_value Yi unify\_value Xi unify atom S unify integer I unify\_nil unify\_cdr Yi unify\_cdr Xi unify unsafe value Yi

#### **Procedural Operations**

call P,N execute P

proceed

escape B

allocate deallocate

**Table 2.1. WAM Operations**

#### **Choice Point Operations**

```

try_me_else C

trust_me_else fail

try C

trust C

cut

retry_me_else C

retry_C

cutd C

```

#### Switch Operations

Table 2.1. (continued)

The compiled-unification operations include get, put, and unify operations. The get operations correspond to the terms and variables in the head of a clause. They are used to retrieve and unify the procedure's arguments with the structure of the clause head. The type of each term in the head determines the type of the corresponding get operation. Variations of get operations match permanent and temporary variables, constants, structures, and lists. Get operations may simply copy an argument value to a permanent or temporary variable (get\_variable). They may unify an argument value with a permanent or temporary variable (get\_value). They may verify that an argument has a specific type and a specific value or may assign a specific type and specific value to an uninstantiated variable (get\_integer, get\_atom, get\_structure, get\_list, get\_nil).

The put operations correspond to the arguments of a subgoal. They are used to create arguments in preparation for a procedure call. Put operations create permanent and temporary variables (put\_variable), duplicate references to existing objects (put\_value), and create constants, structures, and lists (put\_integer, put\_atom, put\_structure, put\_list, put\_nil).

The unify operations combine get and put functionality by both unifying arguments passed into a procedure and creating arguments for a subsequent procedure call. Unify operations correspond to the elements of structures and lists. A sequence of unify operations is preceded by either a get or put operation for a list or structure. This proceeding operation determines the mode in which the following unify operations will execute. In "read mode", unify operations perform unification with successive elements of an existing list or structure. In "write mode", unify

operations create the successive elements of a new list or structure. As with get and put operations, the unify operation is selected by the type of the corresponding term in the Prolog clause.

The procedural operations correspond to the predicates which form the head and subgoals of a clause. Procedural operations transfer control to the subgoals (call, execute) and return control to a parent when a subgoal succeeds (proceed). Procedural operations manage environments by allocating space on the local stack for the permanent variables of a clause (allocate) and deallocating space (deallocate) when the execution of a clause completes.

Choice point operations link together the clauses of a procedure to determine the sequence of clauses which are selected when attempting to solve a goal. Each clause of a procedure is preceded by a choice point operation. The first choice point operation is responsible for creating a choice point (try\_me\_else). Intermediate clauses are preceded by choice point operations which update the alternate clause address (retry\_me\_else). The choice point operation before the last clause removes the choice point of that procedure (trust\_me\_else).

Switch operations speed up Prolog by determining the set of clauses which could potentially match the arguments passed into a procedure. These instructions branch to an address of a single potential clause or to a sequence of calls to potential clauses (try, retry, trust) based on either the type of the first argument (switch\_on\_term) or the value of the first argument (switch\_on\_constant, switch\_on\_structure).

#### 2.1.5. Fundamental Operations

Several implicit operations have significant importance and high frequency of use and are considered fundamental WAM operations. These are the bind, trail, dereference, fail, detrail, and general unification operations. In the PLM, which uses cdr-coding, another fundamental operation is the decdr operation. The bind operation performs instantiation. It converts variables to references and other objects. The trail operation is performed when a variable is bound. It manages the trail by pushing variable addresses onto the trail stack which must be unbound when backtracking. Not all variables which are bound need to be "trailed". Trailing only occurs for global stack variables above the global stack backtrack address and for permanent variables above the local stack backtrack address. This check is included in the trail operation. The dereference operation is used to follow chains of reference pointers to their eventual value. These chains are created during the binding of variables to other variables.

The dereference operation is used within compiled unification and switch operations, within general unification, evaluate, decdr, and within many of the built-in predicate routines. The fail operation implements backtracking. It restores the machine state from the current choice point and uses the detrail operation to reset trailed variables to unbound. The fail operation then transfers control to the most recent alternate clause. The general-unification operation unifies arbitrary Prolog objects and binds variables within these objects as required. It is used within several of the WAM operations (get\_value, unify\_value). General unification uses the push-down list as a scratch pad for unifying nested lists and structures. The decdr operation is used while unifying lists and structures to obtain the next element to be processed in these objects. It must examine the cdr-bit of list elements to properly follow list-continuation pointers.

#### 2.1.6. Built-In Predicates

An implementation modeled after the WAM must integrate a library of built-in predicates (also known as evaluable predicates) into the Prolog system. These predicates either cannot be defined in "pure" Prolog or they are used often enough that it is desirable to build them into the system. Many of the built-in predicates are metalogical or extralogical operations which result in side effects. The core of these predicates is common to most Prolog systems.

A few built-in predicates can be implemented using WAM operations (not, repeat, fail). Other built-in predicates are implemented through explicit operations or instructions (cut). Most WAM implementations supply built-in predicates through an escape mechanism. This escape mechanism may be a procedure call to a routine to accomplish the operation of the built-in predicate or may be a remote procedure call to do the same on another processor.

The evaluate operation which determines the value of arithmetic expressions and is used in the math built-in predicate routines is another fundamental WAM operation. In Prolog, arithmetic expressions are not immediately evaluated. Instead, they are represented by structures with functors corresponding to arithmetic operators and arguments which are themselves arithmetic expressions or numerical constants. In the evaluate operation, the form and functor of an expression is examined. Its arguments are extracted. An arithmetic operation is performed within the unify operations to obtain a numeric value. In a complex expression where the arguments of the expression are also

expressions, the arguments must first be evaluated before the value of the top-most expression can be completed.

The push-down list is used as a stack to evaluate nested expressions.

#### 2.1.7. Palindrome Example

Consider the palindrome Prolog program of figure 2.5. This program takes an original list, reverses it, and verifies that the reversed list is equivalent to the original list. In figure 2.6, we show the WAM operations for the palindrome example. The palindrome WAM code consists of WAM operations for each predicate and for each clause of the program. The sequence for each clause starts with a get operation for each of the terms in the head of the clause. When the get operation corresponds to a list, it is followed by unify operations for each of the elements in the list. The get and unify operations retrieve arguments to match with terms of the clause head and assign argument terms and subterms to permanent and temporary variables. These unification operations are followed by a group of put and unify operations and concluded by a procedural operation for each of the subgoals in the clause body. There is a put operation for each of the arguments of the subgoal which will be called. For list arguments, unify operations are used for each of the elements of the list that is passed to the subgoal. The put and unify instructions create arguments for the subgoal procedure which is then invoked. Two of the clauses contain operations to

```

Original and Reversed

palindrome (Original) :-

are permanent variables.

reverse (Original, Reversed),

samelists (Original, Reversed).

X, L1, and L are

reverse([X|L0], L) :-

permanent variables.

reverse(L0, L1),

concatenate(L1, [X], L).

reverse([], []).

concatenate([X|L1], L2, [X|L3]) :-

concatenate(L1, L2, L3).

concatenate([], X, X).

samelists(Original, Duplicate) :-

equivalent built-in predicate

Original == Duplicate.

```

Figure 2.5. Palindrome Prolog Operations

| palindrome/1: |                                                                                                                                                                                                    |                                                                                                                                                                                                                                  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | allocate get_variable Y2,X1 put_variable Y1,X2 call reverse/2,2 put_unsafe_value Y2,X1 put_unsafe_value Y1,X2 deallocate execute samelists/2                                                       | allocate environment: Original set up argument registers  call reverse procedure set up argument registers  deallocate environment call samelists procedure                                                                      |

| reverse/2:    |                                                                                                                                                                                                    |                                                                                                                                                                                                                                  |

| R2a:          | switch_on_term R2c,R2a,fail try_me_else R2b allocate get_variable Y1,X2 get_list X1 unify_variable Y3 unify_cdr X1 put_variable Y2,X2 call reverse/2,3 put_list X2 unify_unsafe_value Y3 unify_nil | prune search space try first clause, build choice point allocate environment: X, L1, L retrieve argument registers retrieve list argument set up argument registers recursively call reverse procedure set up argument registers |

| R2b:<br>R2c:  | put_unsafe_value Y2,X1 put_unsafe_value Y1,X3 deallocate execute concatenate/3 trust_me_else fail get_nil X1 get_nil X2 proceed                                                                    | deallocate environment<br>call concatenate procedure<br>try last clause, remove choice point<br>retrive argument registers<br>return to calling procedure                                                                        |

Figure 2.6. Palindrome WAM Code

concatenate/3: prune search space switch on term C3c, C3a, fail try first clause, build choice point try me else C3b retrive argument registers C3a: get list X1 unify\_variable X4 unify cdr X1 get\_list X3 unify\_value X4 unify cdr X3 call concatenate procedure execute concatenate/3 try last goal, remove choice point C3b: trust me else fail retrive argument registers get\_value X2,X3 C3c: get nil X1 return to calling procedure proceed samelists/2: call built-in equivalent predicate escape ==/2return to calling procedure proceed

create and remove environments for permanent variable storage. Variables Original and Reversed are the permanent variables Y2 and Y1 in the palindrome predicate. Variables X, L1, and L are the permanent variables Y3, Y2, and Y1 in the first clause of the reverse predicate.

Figure 2.6. (continued)

The WAM code shows how choice point operations link the code for a group of clauses into a single procedure. For the reserve and concatenate procedures, which both contain two clauses, the first clause is preceded by a try\_me\_else operation to create a choice point for the procedure. The second or last clause is preceded by a trust\_me\_else operation to remove the choice point. The switch operations show how the search space of a procedure may be reduced. If the incoming first procedure argument has a constant value, the switch operation directs execution immediately to the second clause. If the incoming first argument has a list value, execution is directed immediately to the first clause. When the first procedure argument is a variable, execution passes through the switch operation and both clauses are tried.

For a fuller description of the Warren Abstract Machine, the reader is referred to Warren's original specification [39]. A description of the PLM variation of the abstract machine is given by Dobry [41]. Additional

references are by David S. Warren [68] and by Hassan Ait-Kaci [69]. The first of these reports describes the abstract machine in stages building from a description of the implementation of a procedural language. The later tutorial builds the WAM by describing each design decision as a means to improve performance.

### 2.2. Special Purpose Prolog Machines

Shortly after Warren specified his abstract machine model, several groups initiated projects to design special-purpose machines that implemented the WAM instruction set and memory organization in hardware. These included Tick's pipelined Prolog processor [65, 40], the Berkeley Programmed Logic Machine (PLM) [41, 5], the Fifth Generation Computer System's Personal Sequential Inference (PSI) Machines [70, 66, 42], the Integrated Prolog Processor (IPP) [71, 72], and the Knowledge Crunching Machine (KCM) [73].

#### 2.2.1. Tick's Pipelined Prolog Processor

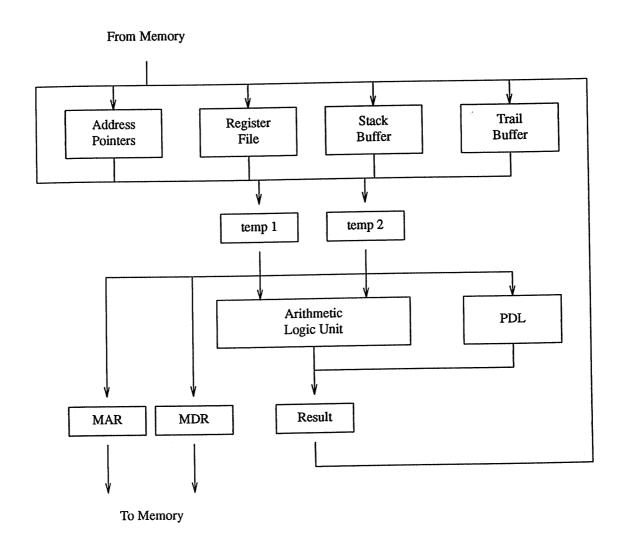

Working with Warren, Evan Tick designed a machine to determine the maximum Prolog performance attainable by a sequential machine for a cost comparable to high-performance Lisp machines [65, 40]. Using the register organization and memory organization of the WAM, Tick's design uses a microprogrammed organization to implement the complex WAM operations as machine instructions. Tick's objectives were a fast cycle time and the ability to issue one microinstruction per cycle when data dependencies and machine resources allow. To offset the cost of microcode interpretation, microinstructions are overlapped in a pipelined execution unit. The architecture is structured to allow multiple execution units to achieve parallel unification.

The architecture consists of a memory system, an instruction unit, an execution unit, and a microcontroller. The memory system is interleaved so that access time is not a critical factor. A cache may be placed in front of main memory.

Figure 2.7 shows the data path of the execution unit that contains three sets of resources. The first set includes WAM address pointer registers, a register file, a stack buffer, and a trail buffer. Several of the address pointer registers are counter registers to allow efficient access to sequential memory locations. The register file is a one-input, one-output array for the procedure's arguments and temporary variables. The stack buffer caches the top of the local stack. Microsequences guarantee that all references to the local stack fall within this buffer. When the current environment is below the stack buffer, it is copied to the top of the local stack. This increases the locality of stack

Figure 2.7. The Data path of Tick's Prolog Processor Execution Unit

references and creates a consistent access to the stack. The buffer uses a copy-back policy. Data consistency must be maintained between the stack buffer and all memory references. The trail buffer caches the top of the trail stack.

Two internal temporary registers form the second group of resources. The last set of resources include the arithmetic logic unit latched to a result register, an array for the push-down list, and a memory address register (MAR) and memory data register (MDR).

Tick's machine uses a three-stage pipeline. The first stage accesses the first set of resources and latches these to the temporary registers. The second stage executes the arithmetic logic unit latching results into the result register, or latches the temporary registers into the PDL or memory address and memory data registers. The last stage returns the result register to the first or second set of resources, or transfers data to or from memory.

WAM machine instructions execute using an arbitrary number of passes through the execution pipeline. The microcontroller supplies the execution unit with microinstructions for each WAM instruction. Each microinstruction specifies information for a single pipeline pass. The microstore containing the microsequences is a two-port, read-only memory permitting access to the next sequential microinstruction and a target microinstruction indicated by a branch control field. Microroutine call and return, unconditional and conditional branches, dispatch next machine instruction, and n-way branches are all supported by the microcontroller. The microcontroller is able to dispatch new instructions every cycle for nearly all microinstructions.

The instruction unit supplies as quickly as possible the starting address of a microsequence to the execution unit where it is queued. To reduce procedure call and conditional branch penalties, special attention is given to computing clause addresses. Each of the call, execute, and proceed operations are replaced by two instructions, a prefetch instruction and a jump instruction. The prefetch instruction is placed by the compiler somewhere before its corresponding jump instruction. It points to a switch\_on\_term instruction that dispatches to one of four clause addresses depending on the type of the first procedure argument. A small cache is included within the instruction unit indexed by procedure name to return the dispatch addresses. A prefetch instruction will attempt to use this cache to determine the start of the microinstruction sequence for the next procedure call together with the type of the object in the first argument register. When the next clause address of a procedure can be determined through a cached entry, the necessity of fetching the switch\_on\_term instruction is eliminated.

The instruction unit contains two interchangeable instruction buffers. These are the current instruction buffer and the future instruction buffer. Each has its own program counter. The clause address determined by a prefetch instruction is inserted into the program counter of the future instruction buffer. Prefetching of WAM instructions may then proceed in the future instruction buffer in competition with prefetching in the current instruction buffer. Execution of a jump instruction in the current instruction buffer switches the roles of the two buffers. Execution continues immediately with the WAM instructions of the next procedure.

According to Tick, the high-performance of his design and its ability to out-perform a microcode implementation on a more general-purpose machine is due to its short microinstruction cycle time, the overlapping of microinstructions, interleaved memory accesses, and the specialized hardware support for procedure calls, indexing, and unification dispatching.

# 2.2.2. The Programmed Logic Machine (PLM)

The Aquarius Project was founded in 1983 at the University of California at Berkeley by Alvin Despain and Yale Patt [74] as an attempt to achieve improvements in computer performance in applications that have substantial artificial intelligence and numerically computational components [75]. A large portion of the project involved the design of architectures and compilers for sequential Prolog execution. The first achievements were the Programmed Logic Machine (PLM) developed by Tep Dobry [41, 5] and the PLM compiler developed by Peter Van Roy [62]. The PLM is a microprogrammed engine implementing the Warren Abstract Machine. Built in 1985, using five hundred TTL chips, it was the first hardware implementation of the WAM. This work led to the VLSI-PLM [76], a single-chip WAM processor containing two hundred and fifty thousand transistors, and the Xenologic X-1 commercial Sun coprocessor.

The PLM is a coprocessor that attaches to a host central processor that provides a memory system, input and output, and assistance in implementing built-in predicates. The PLM executes modified WAM instructions that support cdr-coding, the cut operation, and built-ins predicates. PLM code space is one gigabyte of byte-addressable virtual memory. Instructions are one to six bytes in length including a one-byte opcode and zero to three operands. The PLM data space contains up to one gigabyte of virtual memory of thirty-two-bit words. Four to six bits of each word are used for tag information.

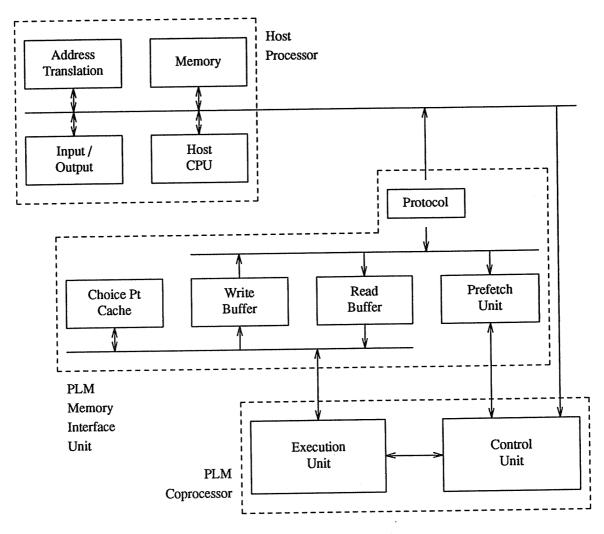

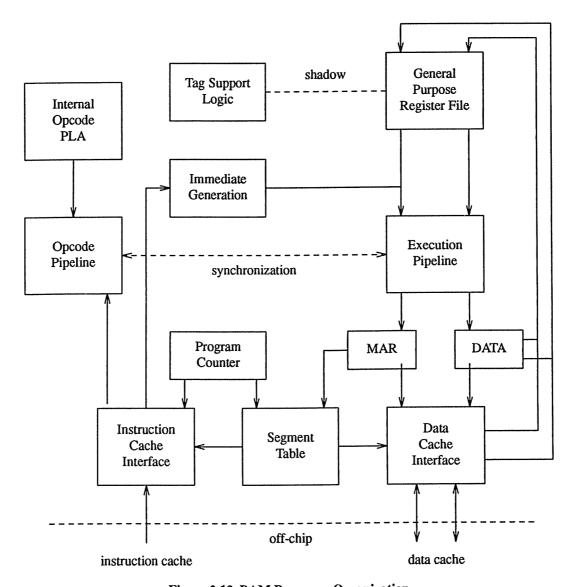

The major components of a PLM system are the host processor, the PLM Memory Interface unit (PMI), and the PLM coprocessor. The PMI is responsible for interfacing the host system to the PLM coprocessor. The PLM consists of an execution unit and a control unit. Figure 2.8 shows the configuration of these components.

The PMI coordinates activity between the PLM and the host system bus. It includes bus-protocol logic, several modules for buffering memory accesses to code space and data space, and logic for sequencing accesses to the bus. Buffering data access allows for a difference in cycle times between the PLM and its host processor. The two

Figure 2.8. Configuration of a PLM System

primary data buffers are the read buffer and the write buffer. Memory write operations initiated by the PLM are queued in the write buffer waiting to be sent to memory while the PLM continues execution. PLM read requests are queued in the read buffer waiting access to the bus. The PLM waits for reads to be serviced before continuing execution. Read requests are delayed until pending writes have been serviced to ensure consistency of data.

A choice point cache holds the current choice point to speed up execution of choice point operations. A writethrough policy ensures consistency between memory and this cache. When a new choice point is created, the contents of the choice point cache are overwritten and used in subsequent choice point operations. When a choice point is removed, the choice point cache is marked invalid. Refilling of the cache takes place as a side effect during a subsequent choice point access at the next fail operation. This policy eliminates premature refilling of the cache with a choice point that is overwritten before being accessed.

The PMI provides code-space buffering and partial instruction decoding in a prefetch unit. The prefetch unit contains a small instruction buffer holding up to four PLM instructions. Prefetch takes place as time permits behind data accesses as long as there is at least one instruction ready to execute. When the instruction buffer becomes empty, fetching the next instruction obtains highest priority. The prefetch unit aligns instructions and their operands before buffering. Instructions are sent to the PLM control unit through an opcode buffer and an argument buffer. The opcode buffer has single-byte width. The argument buffer holds the first operand in a thirty-two-bit word and any second or third operands packed in the next word. The PLM coprocessor will fetch the opcode and the first operand in one stage and second and third operands in a following stage.

The prefetch unit recognizes instructions that change control flow. It continues fetching instructions through unconditional branches. For conditional branches, the prefetch unit waits for the execution unit to catch up before deciding on the direction to continue prefetching. Backtracking is an additional change of control flow. It causes the prefetch unit to flush its instruction buffer and begin fetching at the backtrack point in parallel with the restoration of state information from the choice point contents.

The PLM processor consists of an execution unit and a control unit. The control unit includes a microsequencer and a kiloword control store containing 144-bit-wide horizontal microinstructions. The control unit coordinates the PMI and the PLM execution unit. It interfaces directly with the host so that the host may start and stop control of the PLM and inspect its state.

The control unit dispatches signals to control the data paths of the execution unit. It calculates the next microinstruction address and fetches the microinstruction from the control store. These operations are executed in parallel.

The next instruction address is derived in several stages involving various decisions. The source of the next instruction may come from machine-instruction decode logic, fundamental-operation select logic, a microreturn register, or the microaddress seed of the current microinstruction. The instruction decode logic determines an appropriate microcode entry point for the execution of a new PLM instruction using the instruction's opcode and some status

information. The fundamental-operation select logic is used to branch to a microcode entry point other than the start of a new PLM instruction. This occurs most frequently in executing fundamental operations. The microreturn register is used to implement microcall and microreturn operations for the dereference and decdr operations. The microaddress seed specifies a branching address for the microcode sequences. It may be used to realize up to a four-way branch by dividing the control store into four pages, prepending two page bits to the microaddress seed, and then branching to the address given by the seed in the selected page. To allow all decisions to be made and time for an access to the control store to be accomplished in a single microcycle, several features had to be added to microcode and hardware including delayed branching and shadowing of the tag bits for all the argument registers.