#### Deterministic Time and Analytical Models of Parallel Architectures

by

Mark A. Holliday

Computer Sciences Technical Report #652

July 1986

•

# DETERMINISTIC TIME AND ANALYTICAL MODELS OF PARALLEL ARCHITECTURES

by

#### MARK ARMIGER HOLLIDAY

A thesis submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy (Computer Sciences)

at the

UNIVERSITY OF WISCONSIN — MADISON

1986

#### Abstract

In parallel computer architectures many events are of constant duration. For example, a fetch of a cache block, ignoring resource contention, takes a fixed number of clock cycles. Analytical performance modeling techniques that include deterministic time have previously been proposed. However, serious restrictions on the set of allowed models are imposed in these previous techniques. In this dissertation we extend these previous modeling techniques by removing those restrictions. Those restrictions fall into two classes: those involving the construction of the state space and those involving the analysis of the state space. We propose interpretations for performance measures when those restrictions are removed. In this general case, the state space represents an arbitrary, finite state, discrete parameter Markov Chain. We also present algorithms that efficiently construct and analyze the state space in the general case.

Our technique is called Generalized Timed Petri Nets (GTPN). It has been implemented in a tool and has been used to develop models for several interesting architectures. The two most important studies examine bus-based multiprocessors. Performance degradation due to memory and bus interference in multiprocessors with a single-stage interconnection network has been frequently examined. Using the GTPN we are able to derive exact performance estimates in the important case when memory access times are constant and interrequest times are non-zero. Previously only approximate estimates and simulation results existed.

Caches are an important means for reducing memory contention in bus-based multiprocessors. Our second study is the first analytical performance comparison of the key features of protocols that maintain cache consistency when a single shared bus is assumed.

## Acknowledgements

This research would not have been done without the advice and support of many people. My advisor, Mary Vernon, has been very supportive throughout the development of this thesis. Her keen insight, enthusiasm, and willingness to devote a substantial amount of her valuable time, have contributed greatly to my work.

I would like to thank the members of my committee, Mary Vernon, David Dewitt, Peter Glynn, Jim Goodman, and Udi Manber for taking the time to serve on the committee and for their comments and suggestions.

I would like to thank Bill Kalsow for his support of the document preparation software I have used in this thesis. His comments in numerous discussions have also aided my research considerably.

I would like to thank my parents, Sam and Joan, for their many years of support. I would like to thank my daughter, Julia, for bringing me so much joy. Most of all I would like to thank my wife, Mary. During many late nights and weekends she cheerfully kept our home running without me.

## Contents

| Αŀ  | stra  | ct     |                                       | ii   |

|-----|-------|--------|---------------------------------------|------|

| Ac  | knov  | vledge | ments                                 | iii  |

| Lis | st of | Figure | es ·                                  | vii  |

| Li  | st of | Tables | ı.                                    | ix   |

| 1   | Intr  | oducti |                                       | 1    |

|     | 1.1   | Detern | ninistic Times and Analytical Models  | 1    |

|     | 1.2   | Organ  | ization of this Thesis                | 2    |

|     | 1.3   | Relate | d Work                                | 3    |

|     |       | 1.3.1  | Untimed Petri Nets                    | . 3  |

|     |       | 1.3.2  | Performance-oriented Petri Net Models | . 4  |

|     |       | 1.3.3  | Most Relevant Previous TPN Models     | . 5  |

| 2   | The   | GTP    | N Model                               | 8    |

|     | 2.1   | Findir | ng Maximals                           | . 10 |

|     |       | 2.1.1  | The Partition Algorithm               | . 12 |

|     |       | 2.1.2  | The FindMax Algorithm                 |      |

|     | 2.2   | Comp   | uting Probabilities                   |      |

| 3   | GТ    | PN Pe  | erformance Analysis                   | 17   |

| Ü   | 3.1   | Findir | ng Recurrent Classes                  | . 18 |

|     | 3.2   | Absor  | ption Probabilities                   | . 19 |

|     | 3.3   | Long   | Run Expected Fraction of Visits       | . 20 |

|     | 3.4   |        | rce Usage Estimates                   |      |

|     | 3.5   |        | neter Set of the Stochastic Process   |      |

|     | 3.6   |        | outational Issues: Transient States   |      |

|     | 3.0   | 3.6.1  | First Step Analysis                   | . 23 |

|     |       |        | Optimization of First Step Analysis   | 0.0  |

|   |            | 3.6.3    | Computing Mean Time to Absorption                      | 24         |

|---|------------|----------|--------------------------------------------------------|------------|

|   |            | 3.6.4    | More Efficient Solution of an Important Special Case   | <b>25</b>  |

|   | 3.7        | Comp     | utational Issues: Stationary Probability Distributions | <b>25</b>  |

|   | ٠          | 3.7.1    | Spectral Distribution                                  | 26         |

|   |            | 3.7.2    | Ensuring Convergence                                   | 26         |

|   |            | 3.7.3    | Convergence Rate                                       | 27         |

|   | Com        |          | on with SPN Models                                     | 28         |

| 4 |            | Carfi    | ct Resolution                                          | <b>2</b> 8 |

|   | 4.1        | Dache    | bility Assignment                                      | 30         |

|   | 4.2        | Proba    | ling Features                                          | 30         |

|   | 4.3        | Model    | lexity Issues                                          | 31         |

|   | 4.4        | Comp     | lexity issues                                          |            |

| 5 | Tw         | o Exar   | nples                                                  | 33         |

|   | 5.1        | The D    | Dining Philosophers                                    | 33         |

|   | 5.2        | The C    | CRAY-1                                                 | 38         |

|   |            | 5.2.1    | The CRAY-1 Model                                       | 42         |

|   |            | 5.2.2    | Experiments                                            | 44         |

| 6 | Mıı        | ltiproc  | cessor Memory and Bus Interference                     | 46         |

|   | 6.1        | Backg    | ground                                                 | 47         |

|   | 0.1        | 6.1.1    | Multiprocessor Characteristics                         | 47         |

|   |            | 6.1.2    | Previous Results: Bhandarkar                           | 48         |

|   |            | 6.1.3    | Less Restrictive Models                                | 49         |

|   | 6.2        |          | processor Analysis                                     | 50         |

|   |            | 6.2.1    | Measures and the GTPN net                              | 50         |

|   |            | 6.2.2    | Model Validations                                      | <b>52</b>  |

|   |            | 6.2.3    | Comparison with Exponential Memory Access Time Models. | 54         |

|   |            | 6.2.4    | Critical Memory Request Probability                    | 58         |

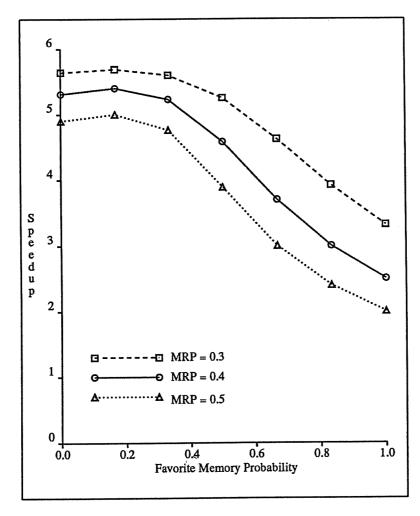

|   |            | 6.2.5    | Non-Uniform Access Probabilities                       | 60         |

|   | 6.3        | Conc     | lusion                                                 | 61         |

| - |            | ala a Ca | onsistency Protocols                                   | 63         |

| 7 |            |          | duction                                                | 63         |

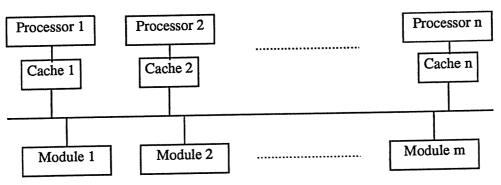

|   | 7.1        | Maria    | iprocessor Characteristics                             | 64         |

|   | 7.2        |          |                                                        | 64         |

|   |            | 7.2.1    | 0.1 0.1                                                | 65         |

|   |            | 7.2.2    | and the Colonian                                       | 66         |

|   | <b>-</b> ~ | 7.2.3    | Protocols                                              |            |

|   | 7.3        | Ine.     | LIOTOCOIS · · · · · · · · · · · · · · · · · · ·        |            |

|        |                                          | VI        |  |  |

|--------|------------------------------------------|-----------|--|--|

| 7      | .3.1 The Basic Protocol                  | 66        |  |  |

| 7      | .3.2 Enhancements                        | 68        |  |  |

| 7      | 3.3 Protocols in the Literature          | 70        |  |  |

| 7.4 T  | The Protocol Models                      | 70        |  |  |

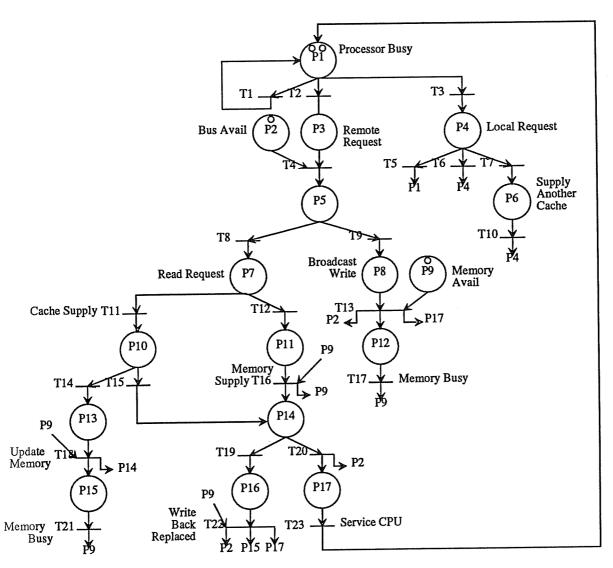

|        | .4.1 The Basic Protocol: Net             | 70        |  |  |

| 7      | .4.2 The Basic Protocol Workload         | <b>75</b> |  |  |

|        | .4.3 The Other Protocols                 | 78        |  |  |

| 7.5 F  | Protocol Performance                     | 78        |  |  |

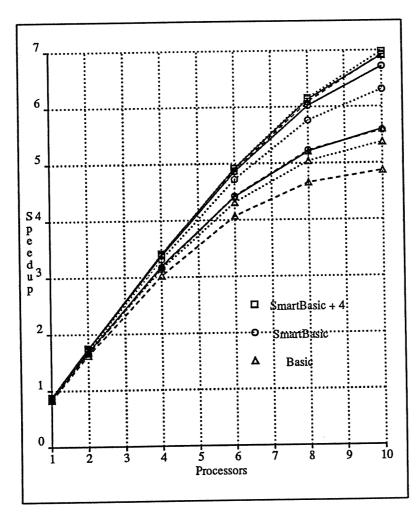

|        | .5.1 Effect of Enhancements              | 79        |  |  |

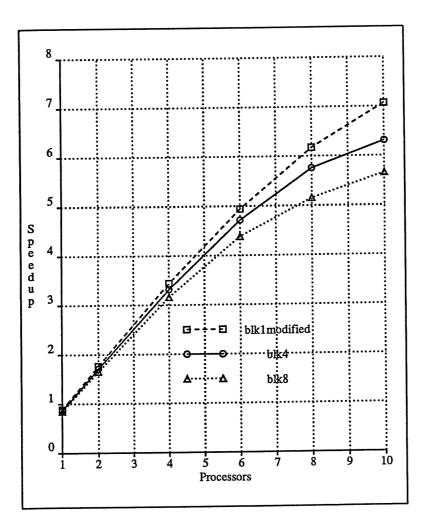

| 7      | .5.2 Effect of Blocksize                 | 81        |  |  |

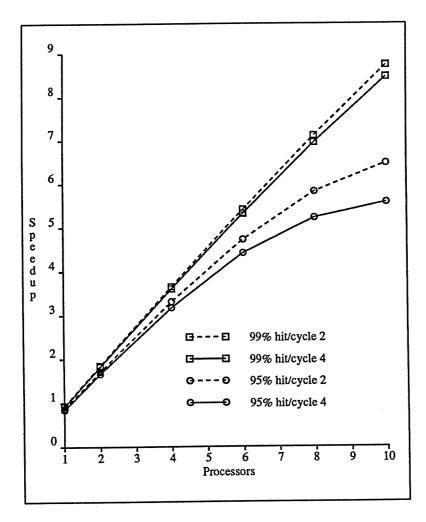

| 7      | .5.3 Effect of Hit Rate and Memory Speed | 83        |  |  |

| 7.6    | Conclusion                               | 83        |  |  |

| 8 Conc | usion                                    | 86        |  |  |

| _      |                                          |           |  |  |

|        | Future Research Directions               | 87        |  |  |

# List of Figures

| Example of an untimed Petri net                                   | 4                     |

|-------------------------------------------------------------------|-----------------------|

| Example of a GTPN net                                             | 9                     |

| Reachability Graph for example                                    | 9                     |

| Overall State Space Algorithm                                     | 11                    |

|                                                                   | 14                    |

| FindMax Example: optimized search                                 | 14                    |

| Competing Geometric Delays in the GTPN                            | 29                    |

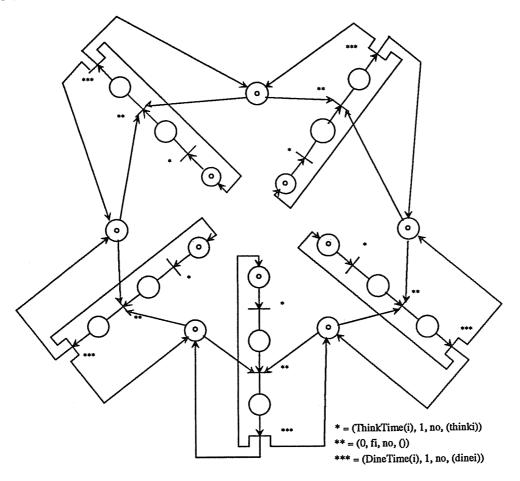

| Dining Philosophers GTPN Model                                    | 34                    |

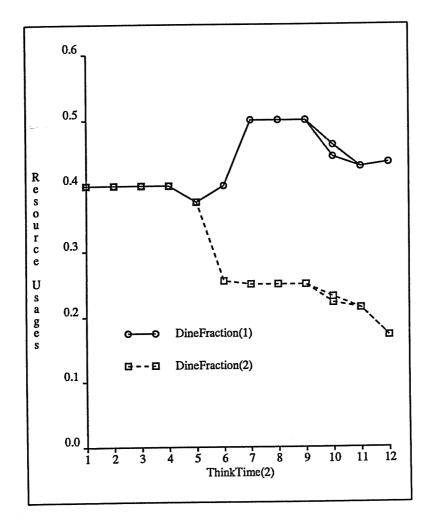

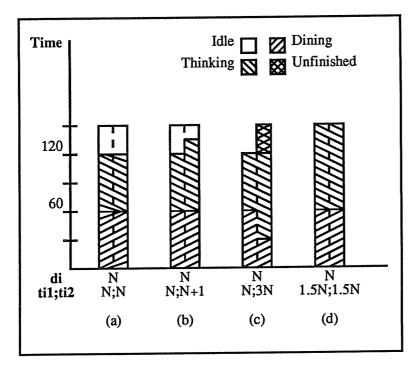

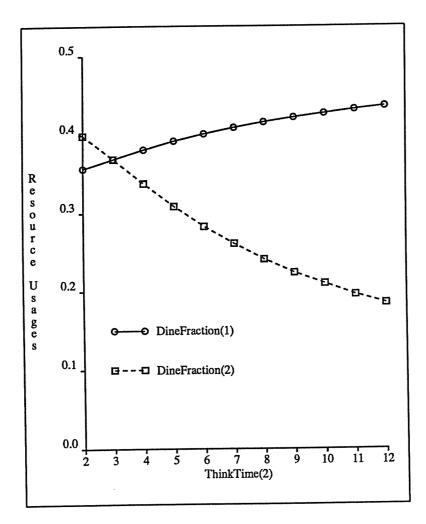

|                                                                   | 36                    |

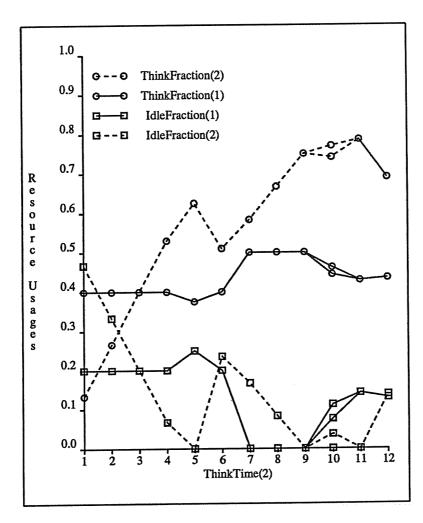

| Dine time for deterministic philosophers                          | 37                    |

| Performance for Selected Parameters                               | 38                    |

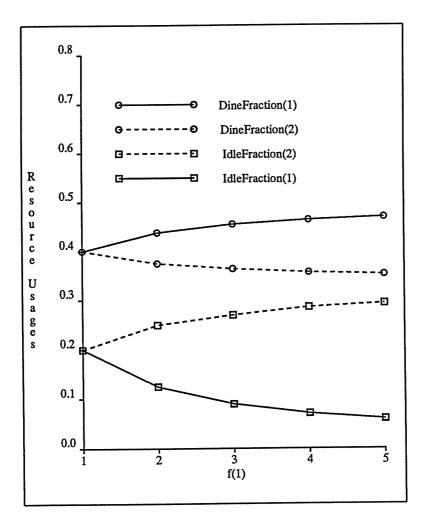

| Performance with Aggressive Philosophers                          | 39                    |

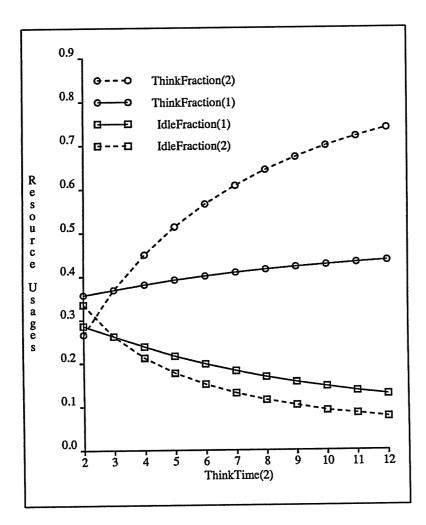

| Idle and think times for geometric philosophers                   | 40                    |

| Dine times for geometric philosophers                             | 41                    |

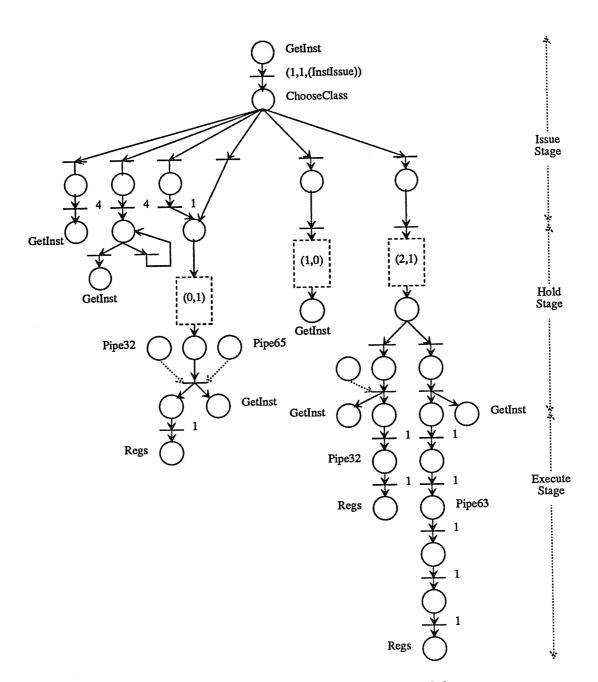

| The CRAY-1 GTPN Model                                             | 43                    |

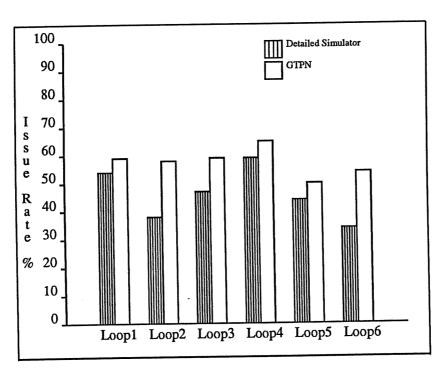

| Instruction Issue Rate for the Loop Benchmarks                    | 45                    |

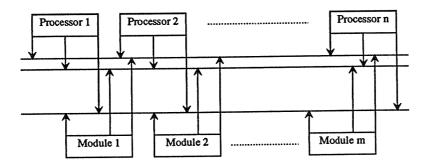

| The Multiprocessor System                                         | 48                    |

| GTPN net for a 3 processor/2 memory/1 bus system. Uniform access. | 51                    |

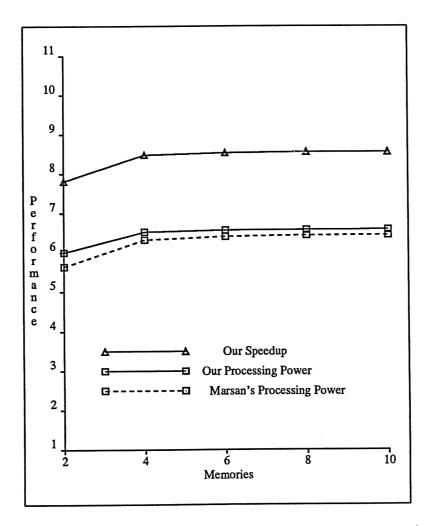

| Expo. access time vs. constant cycle time. 12 processors/2 buses. |                       |

|                                                                   | 56                    |

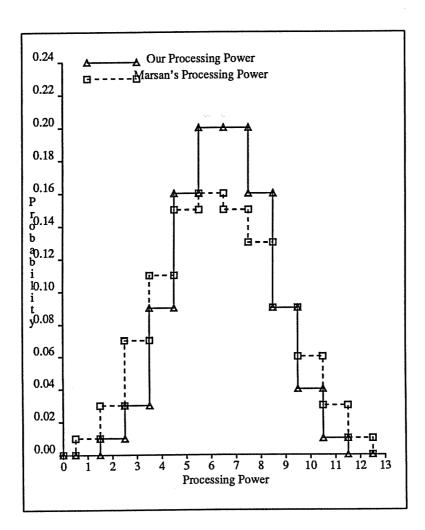

| Probability Distributions for the 6 memory case                   | 57                    |

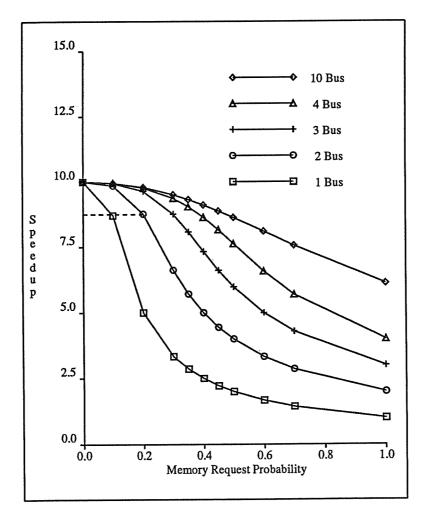

| Measure is speedup. 10 processor/10 memory. Uniform access        | 59                    |

| Favorite Memory nonuniform accesses. 6 processor/6 memory/3 bus.  | 60                    |

| The Multiprocessor Configuration                                  | 64                    |

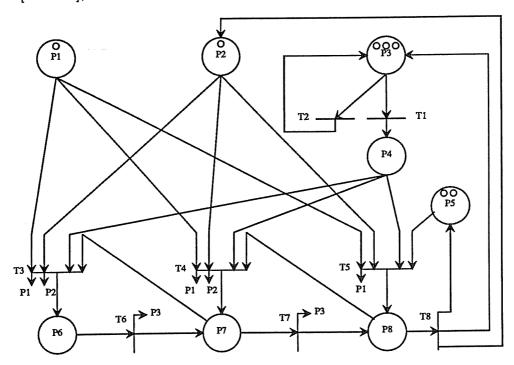

| GTPN Model for the Basic Protocol                                 | 71                    |

|                                                                   | 80                    |

|                                                                   | Example of a GTPN net |

|            |                                              | VIII |

|------------|----------------------------------------------|------|

| 7.4<br>7.5 | Varying Block Size. SmartBasic at 5% sharing |      |

|            | 20% sharing                                  | 84   |

## List of Tables

| 2.1 | Reachable States for example                                                       | 9          |

|-----|------------------------------------------------------------------------------------|------------|

| 6.1 | The attributes of each transition in the multiprocessor net                        | <b>51</b>  |

| 6.2 | Expected number of busy memory modules. Crossbar. $MRP = 1$ .                      | <b>52</b>  |

| 6.3 | Expected number of busy memory modules. 16 processor/16 memories/Multibus. MRP = 1 | 53         |

| 6.4 | Expected number of busy memory modules. 8 processor/8 memory.  MRP = 0.5           | 54         |

| 6.5 | Expected number of busy memory modules. 16 processor/16 memory.                    | 54         |

| 7.1 | The Frequency Attribute of Basic Protocol Model Transitions                        | 73         |

| 7.2 | The Other Attributes of Basic Protocol Model Transitions                           | 74         |

| 7.3 | Meaning of Fundamental Workload Parameters                                         | 76         |

| 7.4 | Values of Fundamental Workload Parameters                                          | 76         |

| 7.5 | Intermediate Workload Values                                                       | 77         |

| 7.6 | Summary of Speed-Up Estimates for 10 Processors                                    | <b>7</b> 9 |

| 7.7 |                                                                                    | 81         |

## Chapter 1

#### Introduction

## 1.1 Deterministic Times and Analytical Models

The goal of our research is to develop analytical performance models of parallel computer architectures. An important feature of computer architectures is deterministic time. Events—for example, a clock cycle or a fetch from memory—often take a constant amount of time. Little work has been done in developing analytical modeling techniques that allow representing deterministic times. Consequently, a substantial part of our work has involved developing a new modeling technique that supports deterministic times.

This new technique is called Generalized Timed Petri Nets (GTPN). As the name suggests, our technique is an extension of a group of previous techniques based on Timed Petri Nets (TPN). Timed Petri Nets are a graphical model description notation. The general approach used by these techniques is as follows. The system is described by a model formulated as a Timed Petri Net. An initial state is also specified. The modeling tool constructs the state space formed by all the states that can be reached from that initial state. The state space is then analyzed in order to determine various performance measures.

The previous TPN models had substantial limitations with respect to both constructing the state space and analyzing the state space. To simplify constructing the state space, restrictions are imposed on the connectivity of the model descriptions when viewed as a graph. These restriction prevent representing important aspects of system behavior. Restrictions are also imposed on the structure of the state space in order to simplify the analysis phase. These restrictions are especially limiting, because of the large semantic gap between the model description and the state space. A model description of 30 lines can easily have a state space of 45,000 with complex probabilities on edges and times-in-state.

A substantial portion of our work has involved removing these restrictions. The

only remaining requirement is that the model's state space be finite (in practice it is usually obvious when an error in the description causes the state space to be infinite). Removal of these restrictions involved two classes of issues: conceptual issues and computational issues. At the conceptual level we had to find reasonable meanings for the situations that are no longer prohibited. At the computational level we had to propose and implement efficient algorithms for constructing and analyzing the state space in the general case.

The state space analysis is based on Markov Chain theory. The use of Markov Chain theory was suggested in the earlier TPN models. However, even in the restricted case they allowed, a rigorous treatment of the relationship to Markov Chain theory, was lacking. We have supplied such a treatment.

Of course, the extensions to previous TPN models we have made in our GTPN are a significant research contribution only to the extent that the GTPN adds to our ability to model interesting systems. We contend that the GTPN does significantly add to our modeling abilities. That contention is based on several modeling studies that have been conducted using the GTPN. By providing a flexible, efficient modeling tool that supports deterministic time, we have been to reach some interesting new results. For example, in a general model of multiprocessor memory and bus interference in single-stage interconnection networks, we are the first to derive exact performance estimates. Previously, only approximate derivations and simulations existed. In another study we provide the first analytical comparison of a wide range of cache consistency protocols that assume a shared bus.

An important result of our studies was demonstrating that interesting systems can have "unusual" state space behavior. By "unusual", we mean two things, both of which will be defined more completely later. First, a system may have multiple long run behaviors. Second, a system may be "periodic" which loosely means that the system may indefinitely oscillate among several probability distributions across the states.

## 1.2 Organization of this Thesis

In this section we describe the organization of the remainder of the thesis. The remainder of this chapter reviews related work in modeling techniques. In particular, it looks at untimed Petri Nets, the general class of Petri Nets with time, and lastly, the most relevant previous TPN models. The next three chapters present and discuss the GTPN. Chapter 2 discusses the GTPN model description semantics and the algorithms used in constructing the state space. Chapter 3 discusses the analysis of the state space. The first part of this chapter discusses how Markov Chain theory can be used to analyze an arbitrary finite state space. The remainder of the chapter covers the numerical issues involved. Stochastic Petri Nets (SPNs) are an important alternative method of including time and probabilities into Petri Nets. Chapter 4 compares and contrasts the GTPN with the SPN models.

Chapters 5 through 7 present applications of the GTPN. Chapter 5 looks at two model studies. The first is of the Dining Philosophers problem. The second is modeling typical workloads on the scalar mode portion of the CRAY-1 supercomputer. Chapter 6 examines memory and bus interference in a multiprocessor with a single-stage interconnection network. Chapter 7 addresses the performance evaluation of alternative shared bus cache consistency protocols.

The last chapter, Chapter 8, concludes the thesis by summarizing our work and then discussing possible future research directions.

#### 1.3 Related Work

In this section we describe untimed Petri Nets and previous Petri Net models with time. This provides a foundation for the presentation of the GTPN which starts in Chapter 2. Subsection 1.3.1 describes untimed Petri Nets. A more thorough introduction to untimed Petri Nets can be found in Peterson [PET81]. Subsection 1.3.2 surveys performance-oriented Petri Nets. Subsection 1.3.3 reviews the most relevant previous: the work of Zuberek, and Razouk and Phelps.

#### 1.3.1 Untimed Petri Nets

Untimed Petri Nets (PNs) contain places P, transitions T, and arcs A. The arcs are directed and can only connect transitions to places and places to transitions. If an arc exists from a place to a transition, then the place is an input place for that transition. If an arc exists from a transition to a place, then the place is an output place for that transition. Places may contain tokens. The state of a PN is defined by the number of tokens in each place and is represented by a vector M called the marking vector. M[i] is the number of tokens in the *i*th place.

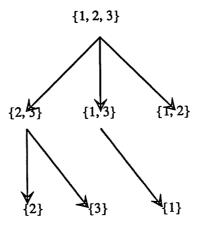

Petri Nets are often illustrated graphically, as shown in Figure 1.1. Circles represent the places. Black dots in the circles represent the tokens. Bars represent the transitions.

The number of arcs connecting a place to a transition is that input place's multiplicity. A transition is enabled if each of its input places contains at least as many tokens as there are arcs from the place to the transition. The tokens on all input places which exactly equal the input's multiplicity are the transition's enabling tokens. An enabled transition can fire. A transition fires by: 1) removing all of its enabling tokens from its input places, and 2) placing on each of its output places one token for each arc from the transition to that output place. Each firing of a transition changes the assignment of tokens to places and thus creates a new state. The reachability set of a PN and a given initial state is the set of all states that can be reached from that initial state via a sequence of transition firings. The reachability graph associated with a reachability set can be constructed as follows. Represent

Figure 1.1: Example of an untimed Petri net

each state by a vertex and place a directed edge from vertex  $v_1$  to vertex  $v_2$  if the state  $v_2$  can result from firing some transition enabled in state  $v_1$ .

## 1.3.2 Performance-oriented Petri Net Models

Ramachandani [RAM74] was the first Petri Net model to include time. His approach introduced a fixed firing time with each transition in a Petri net. Since 1974 many other models have been proposed. These models may be distinguished by two simple criteria. One, is by whether firing times are associated with transitions or with places. The second is by whether firing times are constants or random variables (models with random variable firing times, also sometimes allow constant firing times as a special case).

The second criteria is much more significant. The models assuming constant firing times we will refer to as Timed Petri Nets (TPNs). We will refer to the models assuming firing times are random variables as Stochastic Petri Nets (SPNs). Several of the TPNs use an algebraic approach to the analysis. Ramamoorthy and Ho [RAM80] consider the structure of the net as a graph. For a very restricted class of nets, they find the longest circuit in the graph using a matrix algorithm. Coolahan and Roussopoulos [COO83] derive lower and upper bound timing equations from the net, again by viewing the net as a graph and determining the possible paths through the graph. In contrast to the approaches by Ramamoorthy and Ho and by Coolahan and Roussopoulos, Stotts and Pratt [STO85] build the net's state space. However, they do not introduce a stochastic process interpretation.

The SPNs, models that assume firing times are random variables, on the other hand, almost invariably construct the net's state space, to which stochastic process techniques are applied. The first models assumed that all firing times are exponential random variables. These models were independently proposed by Natkin [NAT80], Symons [SYM80], and Molloy [MOL81,MOL82]. The restriction to exponential random variables allows a simple analysis because the underlying stochastic process is a

continuous-time Markov Chain. Loosening this restriction supports a more flexible semantics, but implies a more complex underlying stochastic process. The more recent models have attempted to deal with this problem. An important such model is Generalized Stochastic Petri Nets (GSPNs) by Marsan, Balbo, and Conte [AJM84]. In the GSPN instantaneous firing times as well as exponential firing times are allowed. The ESP of Cumani [CUM85] is an extension so that firing times have an arbitrary phase-type distribution. The Extended Stochastic Petri Nets of Dugan, Trivedi, Geist, and Nicola [DUG84] is a very general model. The firing times have arbitrary distributions. If the underlying stochastic process is analytically solvable, then it is solved; otherwise, the net is simulated.

Some work has been done on attempting to merge the TPN and SPN approaches. Two noteworthy attempts are Molloy's Discrete-Time Stochastic Petri Nets [MOL85] and the Deterministic Stochastic Petri Nets of Marsan and Chiola [AJM85b]. Both approaches allow deterministic firing times, but only with fairly strong restrictions.

An alternative perspective is reflected in the models of Zuberek [ZUB80], and Razouk and Phelps [RAZ84]. Their models are TPNs but they build the state space and analyze it as a stochastic process. For many systems to be modeled, deterministic time is the right semantics. In addition, interpreting the evolution of a system as a stochastic process allows the powerful results of stochastic process theory to be used. Moreover, often when deterministic time is not the right semantics, the desired random variable can be constructed from deterministic firing times. For these reasons, our approach is built on their work.

Despite the promise of their approach, serious problems existed. They assumed fairly strong restrictions on the structure of the net. In addition, the stochastic process foundation of their analysis was unclear. A more detailed description of their models and restrictions is in the following subsection. In Chapter 4 we compare and contrast our extension of their work with the SPN models.

## 1.3.3 Most Relevant Previous TPN Models

In this subsection we describe the TPN models of Zuberek, and Razouk and Phelps. The TPN model [ZUB80,RAZ84] is a Petri net which has been augmented to include a set of firing durations (D), a set of firing frequencies (F), and a set of named resources (R). Each set is associated with the transitions in the net. Letting S denote the set of reachable states,  $\Re^+$  denote the positive reals, and  $\mathcal P$  denote the power set, the model is formally defined as follows:

$$TPN = (P, T, A, M_0, D, F, R)$$

where

```

P = \{p_1, p_2, \dots, p_n\} (places)

T = \{t_1, t_2, \dots, t_m\} (transitions)

A: \{P \times T\} \cup \{T \times P\} \rightarrow \{0, 1, 2, \dots\} (directed arcs)

M_0: P \rightarrow \{0, 1, \dots\} (initial marking)

D: T \times S \rightarrow \Re^+ \cup \{0\} (firing durations)

F: T \times S \rightarrow \Re^+ \cup \{0\} (firing frequencies)

R: P \cup T \rightarrow \mathcal{P}(\{r_1, r_2, \dots, r_k\}) (resources)

```

The state of a TPN is defined differently than in untimed Petri Nets because firing a transition is not an atomic operation. A transition has an associated deterministic firing duration. There is a start firing, and an end firing event. In between the firing is in progress. The removal of tokens from a transition's input places occurs at start firing. The placement of tokens on a transition's output places occurs at end firing. While the firing of a transition is in progress, the time to end firing, called the remaining firing time (RFT), decreases from the firing duration to zero (without causing a change in the marking of the net). Because firings can be in progress when a marking change occurs, a state is only partially defined by the distribution of tokens. A state must also include the RFT of each firing in progress. A state is thus a marking vector and a set of RFT's.

Also unlike an untimed Petri net, the next state is not generated by a single start firing or end firing event. Instead it is generated by a set of start firings or a set of end firings which occur simultaneously. Given a particular state, the basic rule for finding the possible next states is straightforward. Find how many enablings of each transition exist. (Instead of a transition being either enabled or not, it has a nonnegative number of enablings. N enablings of a transition exist if each of its input places contains a number of tokens equal to at least N times its multiplicity.). Find the maximal sets<sup>1</sup> that can start firing simultaneously. Each maximal defines a next state. The time spent in the original state is zero. The RFT vectors of the transitions which just started firing are set to their transition's duration. The frequencies are used in assigning probabilities to next states formed by the start firings of maximal sets. If there are no enablings, but there are some firings in progress, then the next state is generated by the end firing of all transitions with the smallest RFT (Tmin). The time-in-state value in this case is Tmin. If there are no enablings and no firings in progress, then the net remains in the current state forever.

The rule that next states are generated by sets of events that occur simultaneously, is not strictly necessary. The advantage of having it is that the state spaces generated are dramatically smaller. The disadvantage is that the algorithms for building the state space are more complicated.

Zuberek suggested that the reachability graph of the Timed Petri Net be viewed as a Markov Chain and that performance measures be computed using standard

<sup>&</sup>lt;sup>1</sup>A set with property  $\alpha$  is a maximal set with property  $\alpha$  if it is not a proper subset of any other set with property  $\alpha$ .

techniques for analyzing the Markov Chain's long run behavior. Extensions of his work, however, are desirable in two areas. One, he only proposed a method for constructing a net's reachability graph for a restricted class of nets: nets that are safe and free choice. A net with a given initial state is said to be safe if, for every state in the reachability set, no place has more than one token. A net is free choice if each place that is an input to more than one transition is the only input to those transitions. Two, even for safe and free choice nets, the structure of the reachability graph (i.e. the Markov Chain) may be such that Zuberek's approach gives incorrect values for the performance measures. The states in a discrete time Markov Chain can be divided into classes. A set of classes, called recurrent classes, is important because in the long run the model will reach and stay in one of these classes. Zuberek's approach gives correct values only when there is exactly one recurrent class.

Razouk and Phelps [RAZ84] extend Zuberek's work in the first of the two areas above. They allow a superset of the class of safe, free choice nets. Two or more transitions are said to be in the same conflict set if their sets of input places intersect. Two conflict sets overlap if at least one transition is in both. Razouk and Phelps make the restrictions that conflict sets do not overlap and that all transitions in a conflict set are mutually disabling, i.e. firing of one, disables all the others. They maintain Zuberek's restriction in the second area (they call this, requiring a cyclic net).

Razouk and Phelps also introduce the concept resources, originally proposed in E-Nets [NUT72]. A resource in their model can be associated with one or more transitions. Whenever one of those transitions is firing, the resource is in use. If more than one of these transitions is firing simultaneously, the resource has several usages occurring. By building and analyzing the net's reachability graph we can find the average number of uses of a resource over time. This average, if properly implemented and interpreted, can be used to obtain a variety of meaningful performance estimates.

## Chapter 2

## The GTPN Model

The GTPN model extends the models of Zuberek and Razouk and Phelps by: 1) removing all restrictions on the net except the obvious one that the state space be finite, and 2) computing correct performance estimates for any reachability graph (i.e. an arbitrary embedded discrete parameter, finite state Markov Chain). We also allow the firing duration to be an arbitrary real number (the non-integer case is not discussed by Zuberek or Razouk and Phelps) and we allow resources to be associated with places as well as transitions.

A third extension we have found useful involves firing durations and frequencies. In the models of Zuberek and Razouk and Phelps, the duration and frequency are state-independent constants. In the GTPN model a transition's firing duration and frequency can be expressions containing immediate values (real and integer), names of places, names of transitions, and arithmetic, relational, and logical operators. A place name stands for the number of tokens in that place in the current state. A transition name represents the value one if at least one firing of that transition is in progress in the current state, and is otherwise zero. The state-dependent durations and frequencies become deterministic values when used to determine time-in-state and next state probabilities for a state in the reachability graph. (Note that Petri net inhibitor arcs can be modeled using the state-dependent frequency expressions.)

Besides a firing duration, frequency, and set of resources, a GTPN transition has a flag associated with it that is used in computing the next state probabilities as described in section 2.2.

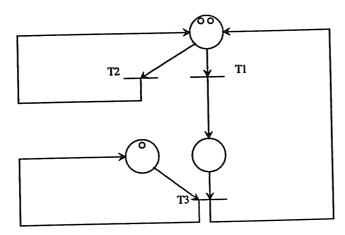

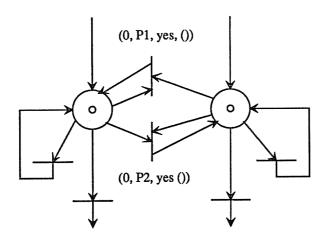

Figure 2.1 shows an example GTPN net, including the initial state distribution of tokens. Each place and transition is labelled. Each transition has, from left to right, its firing duration expression, its frequency expression, its flag, and its list of resources. This example models users at terminals, who with a geometric think time generate requests for a server. There is one token on place P1 for each user. Transitions T1 and T2 implement the think time. Transition T3 implements a load-dependent server with a firing duration that depends on the number of tokens on P2.

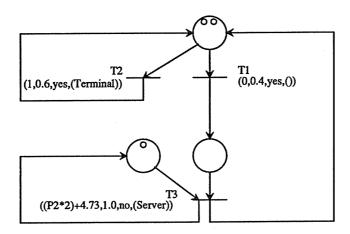

In Figure 2.2 and Table 2.1 we show the reachability graph for the simple GTPN

Figure 2.1: Example of a GTPN net

Figure 2.2: Reachability Graph for example

Table 2.1: Reachable States for example

| States | Marking |    | RFT Set | Resources     |                   |

|--------|---------|----|---------|---------------|-------------------|

|        | P1      | P2 | P3      |               |                   |

| 0      | 1       | 0  | 1       | {}            | {}                |

| 1      | 0       | 0  | 1       | $\{T1,0.0\}$  | {}                |

| 2      | 0       | 0  | 1       | $\{T2,1.0\}$  | $\{Terminal(1)\}$ |

| 3      | 0       | 1  | 1       | {}            | {}                |

| 4      | 0       | 0  | 0       | $\{T3,6.73\}$ | $\{Server(1)\}$   |

in Figure 2.1 assuming only one user. The labels on the edges of the graph are the next state probabilities. The labels on the vertices of the graph are the values for time-in-state. The marking vectors are shown in the table. The RFT sets are shown as a list of pairs, with one pair per in-progress firing of a transition. The first component of each pair is the name of the transition. The second component is the remaining firing time. The resources used and their number of uses are also shown in the table.

The Razouk and Phelps' TPN model does not allow multiple tokens on place P1. Allowing such nets complicates constructing the reachability graph. An overview of our reachability algorithm, which handles these complications, is in Figure 2.3. The TimeInState and ResUsages (number of usages of a resource) functions are used in the performance analysis as described in Section 3. The algorithm has two complex parts: 1) finding the next states when the next states are due to maximal sets of transition enablings which start firing together, and 2) assigning probabilities to next states. These two parts are discussed in the Sections 2.1 and 2.2.

#### 2.1 Finding Maximals

Our first point is somewhat discouraging. In an arbitrary state in a net the number of maximals in the worst case is exponential in the number of enablings.

Theorem 2.1 Consider a state S in a GTPN with n enablings. The number of maximals is  $\Omega(2 \cdot \frac{2^n}{\sqrt{2\pi n}})$ .

pf. First we will construct a state in a net such that the number of maximals is  $\binom{n}{n/2}$ . Consider the case where n is even (The n is odd case is similar.). Consider the net with n transitions and one place P which is an input place for all the transitions. Assume each of the n transitions also has another input place, with one initial token, which is also an output place of the transition. Let the place P have n/2 tokens. In this state, there are n enablings (i.e. each transition is enabled once), and  $\binom{n}{n/2}$  maximals. Thus, the number of maximals is  $\Omega\binom{n}{n/2}$ . The observation that by Stirling's approximation,  $n! = \sqrt{2\pi n}(n/e)^n(1 + O(1/n))$ , completes the proof.

This result should not be given too much weight. In practice, we find that the number of maximals is far less than exponential in the number of enablings. Theorem 2.1 does, however, point out that the space of potential maximals is large. Consequently, an algorithm for finding the maximals must be carefully thought out in order to prevent poor performance when the actual number of maximals is small. The algorithm described below meets this criterion. When we profiled our GTPN tool, the percentage of total program time taken by this algorithm was less than 5% for the analysis of large nets <sup>1</sup>.

$<sup>^{1}</sup>$ we profiled our program using gprof under 4.2 bsd UNIX $^{TM}$  running on a VAX-11/780 $^{TM}$

```

X.State ← Initial State; X.Class ← Frontier

while at least one Frontier state, Y do begin

if Y is a duplicate of an Interior state Z then

Y.Class \leftarrow Duplicate

else begin

Find the set of enablings in Y

If no enablings and the RFT set is empty then

Y.Class \leftarrow Terminal

else if any enablings then begin

Find the set of maximals of enablings

Compute the probability of each maximal

For each maximal M create a new state Z from Y

Remove tokens from the input places of

transitions that have enablings in M

Add a firing, f_t, to the RFT set for each

enabling in M

Set the RFT of each added firing, f_t, to the

firing duration of transition t

Z becomes a child of Y; Z. Class \leftarrow Frontier

for all resources ResUsages[Y] \leftarrow count uses

TimeInState[Y] \leftarrow 0; Y.Class \leftarrow Interior end

else begin

Let Tmin be the smallest RFT in Y

Create state Z from Y by subtracting Tmin from

each RFT in Y

For each firing f_t whose RFT = 0 in Z do

Add tokens to the output places of transition t

Remove f_t from the RFT set

Z becomes a child of Y; TimeInState[Y] \leftarrow Tmin

for all resources ResUsages[Y] \leftarrow count uses

Z.Class ← Frontier; Y.Class ← Interior end

end

```

Figure 2.3: Overall State Space Algorithm

Our algorithm consists of two independent subalgorithms Partition and Find-Max. The Partition algorithm partitions the set of enablings into Generalized Conflict Sets, such that maximals of the partitioned sets can be efficiently combined to generate all the maximals for the original set of enablings. The Partition algorithm does not specify how the maximals for each partition member are found. Maximals are found for each member of the partition by FindMax.

#### 2.1.1 The Partition Algorithm

The Partition algorithm has two parts. The first part constructs a static partition of the set of transitions, T. Define the directly-conflicts-with relation on T as follows. For all  $t_1$  and  $t_2$  in T,  $t_1$  directly-conflicts-with  $t_2$  if the set of input places for  $t_1$  intersects the set of input places for  $t_2$ . Define the conflicts-with relation on T as the transitive closure of the directly-conflicts-with relation. The conflicts-with relation is clearly reflexive, symmetric, and transitive, so it is an equivalence relation on T. The partition of T induced by conflicts-with is denoted by  $\{GCS[i]|1 \le i \le N\}$ , where GCS[i] is the ith member of the partition and N is the size of the partition (GCS) stands for generalized conflict set). Note that a transition which does not share any input places with any other transitions forms a GCS of size one.

Part two of the Partition algorithm uses the conflicts-with partitioning of T to partition the set of enablings, Enablings(S), for each state S. The desired partition of Enablings(S) is

$$\{EGCS[S,i] = Enablings(S) \cap GCS[i] | \text{partition i} \}.$$

At this point, FindMax is applied to each partition member to find its local maximals. Let Maximals[Enablings(S)] be the set of maximals over all the enablings. We have constructed our partition such that Maximals[Enablings(S)] is simply the Cartesian product of the local maximals.

$Maximals[Enabings(S)] = FindMax(S, EGCS[1]) imes \cdots imes FindMax(S, EGCS[N])$

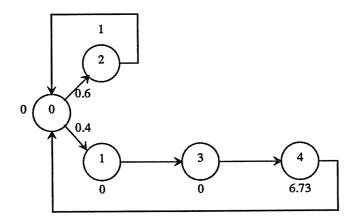

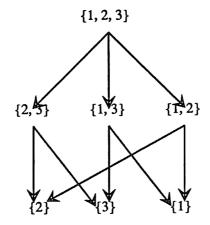

#### 2.1.2 The FindMax Algorithm

We want to find the local maximals for a generalized conflict set, G, in a given state S. Any subset of EGCS[S,G] is a potential local maximal (for brevity's sake we will call a local maximal, a maximal, in this section) The power set, P(EGCS[S,G]), unfortunately, can be a large search space. Our goal is to minimize the number of members of this power set that we examine. Note that set inclusion defines a partial order on P(EGCS[S,G]) which, in turn, induces a directed acyclic graph (see Figure 2.4). This graph has one root which represents the set EGCS[S,G] itself. The FindMax algorithm does a breadth-first search of this graph searching for vertices that are maximals. The traversal is implemented in the standard way using a queue. Initially, the root vertex is the only entry on the queue.

Searching the graph breadth-first causes the order in which vertices are examined to have an important property: if 1) the set of enablings,  $E_1$ , represented by a vertex can fire together, and 2)  $E_1$  is not a subset of any maximal already found, then  $E_1$  is a maximal. In other words, it is impossible that some vertex examined later will have a set of enablings,  $E_2$ , that can all fire together and for which  $E_1$  is a subset. Thus, to find the maximals we just do the breadth-first search, checking each vertex to see if it satisfies properties 1) and 2).

Three methods are used to avoid searching the entire graph. One, if a vertex's set of enablings,  $E_1$ , can all fire together, then none of its descendents needs to be examined (so its children are not added to the queue). Two, a pointer is used to ensure that vertices are never examined more than once. Note that the graph is not a tree. Thus, a naive breadth-first search would cause vertices to be examined multiple times. Three, the pointer used in method two is used to implement a heuristic for pruning subtrees.

Methods two and three are based on a pointer,  $V_p$ , associated with each vertex, V, in the graph. Consider the set of enablings,  $E_1$ , represented by V to be described by a vector of nonnegative integers. The *i*th component of the vector gives the number of enablings of the *i*th transition.  $V_p$  points at one of the components in this vector. The set of transitions to the left of  $V_p$  is  $V_L$ . The set of transitions to the right of  $V_p$  and including the transition pointed to by  $V_p$  is  $V_R$ .

The pointer  $V_p$  can be used to ensure that a vertex is only examined once. The method is as follows. Set the  $V_p$  of the root vertex to point to the leftmost transition. For each parent vertex, subtracting one enabling from the transitions in  $V_R$  defines a child vertex. For each of these child vertices, set its  $V_p$  to point to the transition that was decremented. It can be shown inductively that at each level in the graph, the sets  $V_L$  are distinct for each vertex. Consequently, any child resulting from decrementing  $V_R$  of one parent can never be the same as a child resulting from decrementing  $V_R$  of another parent. Note, also, that the use of  $V_p$  does not cause any state to not be examined that should be examined. For each state, c, that should be examined, there is a vertex, p, whose set of enablings over the transitions in  $V_L$  matches c's set of enablings over the same transitions. Consequently, c will become a child of p.

Method three is a simple optimization made possible by the existence of  $V_p$ . If the enablings in  $V_L$  cannot fire together, then it is irrelevant what enablings are subtracted from  $V_R$ . Consequently, none of the child vertices resulting from decrementing  $V_R$  need be added to the queue.

Figures 2.4 and 2.5 illustrates the FindMax algorithm. Figure 2.4 is the complete directed acyclic graph defined on the power set of  $\{1,2,3\}$  by set inclusion. Figure 2.5 shows only the edges that will be used in the breadth first search. The vertical arrows in the middle row are the pointers used in the optimizations.

Partition and FindMax are used to calculate all maximal sets of enabled transitions which can start firing together. Next state transition probabilities must be assigned to these maximal sets. This is discussed in the next section.

Figure 2.4: FindMax Example: directed acyclic graph

Figure 2.5: FindMax Example: optimized search

#### 2.2 Computing Probabilities

To interpret the reachability graph as a Markov Chain we need to assign probabilities to next states. In the nontrivial case, we need to assign a probability to each maximal set of transitions that can start firing together. From the previous section we know that a maximal is the union of a set of *independent* local maximals, one from each GCS. Thus a reasonable probability for the maximal is the product of the probabilities for the local maximals. Suppose that LocalMax[k, i] is the kth local maximal of the ith generalized conflict set. Suppose that there are N generalized conflict sets and the jth global maximal is the union over all GCS's of the jth local maximal of the ith generalized conflict set. Then

$$Pr\{Maximal[j]\} = \prod_{\{i:i=1,...,N\}} Pr\{LocalMax[j_i,i]\}$$

In order to compute the probability of a local maximal, we take the product of the frequencies of all the enablings in the local maximal. In some cases, this is multiplied by a number NumComb discussed below. Then for each local maximal, we normalize this product by dividing it by the sum of the products over all local maximals. More formally, suppose the *i*th GCS has M local maximals and the frequency expression for the kth enabling in the ith GCS is  $f_k$ . Then, if NumComb is used, our formula for  $Pr\{LocalMax[j_i,i]\}$  is

$$Pr\{LocalMax[j_i,i]\} = \frac{NumComb[LocalMax[j_i,i]] \times \prod\limits_{\{k:k \in LocalMax[j_i,i]\}} f_k}{\sum\limits_{\{m:m=1,...,M\}} NumComb[LocalMax[m,i]] * \prod\limits_{\{k:k \in LocalMax[m,i]\}} f_k}$$

If NumComb is not used, our formula for  $Pr\{LocalMax[j_i, i]\}$  is

$$Pr\{LocalMax[j_i,i]\} = rac{\prod\limits_{\{k:k\in LocalMax[j_i,i]\}}f_k}{\sum\limits_{\{m:m=1,...,M\}}\prod\limits_{\{k:k\in LocalMax[m,i]\}}f_k}$$

NumComb means number of combinations and is a combinatoric value associated with each local maximal. This value is defined as the number of ways tokens can be removed from input places in order to implement that local maximal. As a simple example, suppose the local maximal consists of one enabling of one transition with one input place, two arcs connect the place to the transition, and the input place has three tokens. In this case, the combinatoric value NumComb is  $\binom{3}{2}$ .

Computing NumComb[LocalMax] is done by decomposing it first on the transitions in the local maximal and second on the input places for the given transition. The number of ways that the tokens can be removed from the given input place by the given transition is a binomial coefficient. As we consider each transition,

the value in the upper position of this binomial coefficient is changed to reflect any removals made by transitions considered earlier.

More formally, consider the local maximal, LMax, of the *i*th generalized conflict set. Let InputPlace[t] be the set of input places for transition t. Let Enab[t] be the number of enablings of transition t in this maximal. Let TokNeeded[t,p] be the number of tokens needed from input place p by one enabling of transition t. Note that Enab[t] \* TokNeeded[t,p] is the number of tokens needed from place p by transition t in this maximal. Let TokLeft[p] initially be the number of tokens on input place p in the parent state. After looking at an input place, p, TokLeft[p] is updated to reflect the start firing of all the enablings of transition t. With this notation we have:

$$NumComb[LMax] = \prod_{\{t: t \in LMax\}} \prod_{\{p: p \in InputPlaces[t]\}} \binom{TokLeft[t, p]}{Enab[t] * TokNeeded[t, p]}$$

From practical experience it appears that in some cases it is reasonable to use this combinatoric value when assigning probabilities to local maximals. A boolean flag associated with each transition specifies whether this should be done. Only if the flag is yes for all transitions in the maximal, is NumComb used. Note that if NumComb is used, the next state probabilities are the same as if we constructed the reachability graph by allowing one start firing event at a time with all CntComb flags set to zero, and then summed the probabilities over all paths leading to the state which represents the maximal set.

The motivation for our method of assigning probabilities to local maximals is that it assigns the right probabilities in the important case where all the enablings in a local maximal are independent events. In the case where there are dependencies between the enablings it is difficult to envision a single formula that will always generate the "right" probabilities. This case motivated our introduction of state-dependent frequency expressions. Such frequency expressions can specify what probabilities maximals should have in different markings. Allowing state-dependent frequency expressions also allows the possibility that in some states a transition's frequency expression may evaluate to zero even though it has one or more enablings. We remove these enablings from the set of considered enablings before finding the local maximals.

### Chapter 3

## GTPN Performance Analysis

For the purpose of performance analysis, we view the GTPN as a stochastic process. The time-in-state is a deterministic function, TimeInState, of the state. Nevertheless, the process is stochastic because of the probability distribution over the possible next states. Since the time-in-state can be an arbitrary real number, the process is a continuous time stochastic process. The parameter set is described in Section 3.5. The states of the stochastic process are divided into classes. In the long run, with probability one, the process will reach and stay in one of the set of classes called recurrent classes <sup>1</sup>. Consequently, the long run fraction of time spent in each state depends on which recurrent class the process reaches in the long run. For each recurrent class the long run fraction of time spent in each state forms a probability distribution over the states. Thus, there is a vector of long run probability distributions with one component for each recurrent class. In addition, we can compute the probability (the absorption probability) of reaching each recurrent class in the long run. These absorption probabilities allow us to assign relative weights to the components of the vector of long run probability distributions.

The number of usages of a given resource is also deterministic for a given state; it is a function ResUsages of the state. Consequently, ResUsages, being a function of a random variable, is a random variable. A performance estimate for a resource is a vector with one component for each recurrent class. The value for recurrent class R's vector component is the long run expectation and distribution of that resource's ResUsages random variable, with respect to R's long run probability distribution. In other words, the expectation is the weighted sum of the long run fractions of time spent in each state, given that in the long run the process is in class R. The weight of a state is the number of resource usages in that state. The distribution of a ResUsages random variable is obtained by summing the probabilities of the

<sup>&</sup>lt;sup>1</sup>Note that a terminal state in the reachability graph is a recurrent class due to the self-loop we added (see Figure 2.3).

states that use the resource the same number of times, given that in the long run the process is in class R.

Our approach to computing performance estimates uses the key observation <sup>2</sup> that the times at which state changes occur form an embedded, discrete time, finite state Markov Chain. Consequently, our approach has four parts: 1) building the Markov Chain, 2) aggregating the states in order to reduce the size of the state space, 3) analyzing the Markov Chain, and 4) computing resource usage distributions and expectations in the original stochastic process.

Building the Markov Chain involves building the reachability graph and assigning next state probabilities, as described in Chapter 2. Our aggregation rule is: Any state  $S_2$  can be aggregated with its parent state,  $S_1$ , if and only if  $S_1$  is  $S_2$ 's only parent and  $S_2$  is  $S_1$ 's only child. The number of usages of a resource in an aggregated state equals the sum of its usages in the internal states weighted by the relative fraction of time spent in each internal state. Part 3, the Markov Chain analysis, has three steps: a) finding the chain's recurrent classes, b) finding the absorption probability for each recurrent class, and c) finding, for each recurrent class, the long run fraction of visits to each state. These steps are discussed, respectively, in sections 3.1, 3.2, and 3.3.

Part 4 has two steps: a) for each recurrent class R, computing the long run fraction of time spent in each state (the TimeInState function and the long run fraction of visits to each state are used to do this), b) for each recurrent class R, use the ResUsages functions and the long run fraction of time spent in each state to find the long run distribution and expected number of usages of each resource. These two steps are discussed in section 3.4.

As mentioned above, the long run resource usage distributions and expectations are the performance estimates (given that the process is in class R in the long run). For each resource we thus have a vector of performance estimates. If desired, the expectations could be weighted by the absorption probabilities to give a single performance estimate.

In section 3.5 we give a more precise definition of the parameter set of the GTPN stochastic process. In sections 3.6 and 3.7 we discuss the important numerical issues involved in analyzing the Markov Chain.

#### 3.1 Finding Recurrent Classes

In order to find the recurrent classes we need to first define a recurrent class. Recall that  $\forall n \ P_{ij} = Pr\{X_{n+1} = j | X_n = i\}$ .  $P = [P_{ij}]$  is the one-step transition probability matrix.  $P^{(n)}$ , the n-step transition probability matrix is defined similarly.  $f_{ii}^{(n)}$  is the probability that, starting from state i, the first return to state i occurs at the nth transition. A state is recurrent if  $\sum_{n=0}^{\infty} f_{ii}^{(n)} = 1$ . In other words, a state is recurrent

<sup>&</sup>lt;sup>2</sup>The GSPN model uses a similar observation.

if and only if, after the process starts from state i, with probability one the process returns to state i in a finite length of time. A state is *transient* if it is not recurrent. State j is said to be *accessible* from state i if  $P_{ij}^{(n)} > 0$  for some integer  $n \ge 0$ . Two states i and j that are each accessible to the other, are said to *communicate*.

Note the following facts. Accessibility defines a partial order on the states. This partial order implies a directed graph with the vertices being the states. Communication is an equivalence relation on the states. Thus it partitions the states into subsets called classes. The communication classes are the strongly connected components of the accessibility graph. These strongly connected components form a directed acyclic graph, DAG.

All the states in a class are recurrent or none are, so we can speak of recurrent classes and transient classes. In the case of a finite state space <sup>3</sup>, the recurrent classes are the leaves of the DAG [KEM76] of strongly connected components. The interior nodes of the DAG are the transient classes.

Given that the recurrent classes are the leaves of this DAG, the algorithm to find the recurrent classes is immediate. The reachability graph of the GTPN is the accessibility graph. Create the DAG by finding the strongly connected components of the accessibility graph. We do this using Tarjan's O(n) algorithm [SED81]. Then find the leaves of the DAG by a depth first search starting at the initial state.

#### 3.2 Absorption Probabilities

In a finite state Markov Chain, if we start in a state in a transient class we will eventually reach and stay forever in one of the recurrent classes. We are said to be absorbed by a particular recurrent class. Computing the probability of absorption in a particular recurrent class R given a particular initial state, i, can be done using a standard technique called first-step analysis [TAY84]. On the first state change, the process will move from state i to a state j that is in a transient class or in a recurrent class. If j is in class R, the future probability of being absorbed by class R is one. If j is in another recurrent class, then, by the memoryless property, the probability of being absorbed by class R is the same as if j were the initial state.

More formally, suppose that the states in all the transient classes are numbered 0, ..., r-1 and consider a fixed recurrent class R and fixed initial state i. Let  $U_i = Pr\{$  Absorption in class  $R|X_0 = i\}$  for  $0 \le i < r$ .

$$U_i = \sum_{\{j \in R\}} P_{ij} + \sum_{j=0}^{r-1} P_{ij} U_{jR}, \qquad i = 0, 1, ..., r-1$$

This equation cannot be be solved in isolation. However, if we consider all possible initial states, then we have a system of linear equations that can be solved for the

<sup>&</sup>lt;sup>3</sup>This is not true if the the state space is countably infinite. A simple counterexample is a one-dimensional, asymmetric random walk.

$U_i$ 's. The mean time to absorption can be computed using a similar system of linear equations. Section 3.6 discusses the numerical issues involved.

#### 3.3 Long Run Expected Fraction of Visits

If R is a recurrent class in a finite state space, then  $\forall j \in R$  a number  $\pi_j$  exists such that  $\forall i \in R$

$$\lim_{m \to \infty} E\left[\frac{1}{m} \sum_{k=0}^{m-1} 1_{\{X_k = j\}} | X_0 = i\right] = \lim_{m \to \infty} \frac{1}{m} \sum_{k=0}^{m-1} P_{ij}^{(k)} = \pi_j$$

The leftmost expression above is the long run expected fraction of visits spent in state j.  $1_{\{X_k=j\}}$  is the indicator random variable that equals one when the outcome chosen is in the event  $\{X_k=j\}$  and 0 otherwise.

We want to find these  $\pi_j$ 's for each class R. We do this by noting that each recurrent class R in a finite state space has one and only one stationary probability distribution and the vector  $\pi_R$  of its  $\pi_j$ 's is this stationary probability distribution. This stationary probability distribution is easy to find since it is the unique solution to the set of equations

$$\pi_R = \pi_R P_R \qquad ext{and} \qquad \sum_{j \in R} \pi_j = 1$$

The matrix  $P_R$  is  $P_R = \{P_{ij} | i \in R\}$ . We solve this system of equations numerically using an iterative matrix algorithm, the Power Method [SAU81]. The numerical issues involved in computing this stationary probability distribution are discussed in section 3.7.

It is also true that an arbitrary Markov Chain with a finite state space has at least one stationary probability distribution over the entire state space. However, if the Markov Chain has more than one recurrent class, then any linear combination that sums to one of the stationary probability distributions of the individual recurrent classes is a stationary probability distribution of the chain as a whole.

Our approach is correct regardless of whether the recurrent classes are periodic or aperiodic. Recall that the *period* of a state is the greatest common divisor of all integers  $n \geq 1$  for which  $P_{ii}^{(n)} > 0$ . A state is aperiodic if its period is 1, else is periodic. All the states in a class have the same period so we can refer to a class as periodic or aperiodic. Only for the states i in an aperiodic recurrent class does the limit  $\lim_{n\to\infty} P_{ii}^{(n)}$  exist. However, the long run expected fractions of visits and the stationary probability distribution exist in both cases. Again we assume a finite state space.

#### 3.4 Resource Usage Estimates

We find, for each recurrent class R, the long run expected fraction of time spent in each state. Then, we find the long run distribution and expectation of each resource with respect to each recurrent class.

Let S be the set of states. Let  $RelTime(S_1)$  be the long run expected fraction of time spent in state  $S_1$ , given that the process is absorbed in class R. From the Markov Chain we know the long run expected fraction of visits to each state k,  $\pi_k$ , given absorption in class R.  $RelTime(S_1)$  can be computed, using the TimeInState function, as follows:

$$RelTime(S_1) = rac{\lim\limits_{n o \infty} rac{1}{n} \sum\limits_{t=0}^{n-1} E[1_{\{X(t)=S_1\}} TimeInState(X(t))]}{\lim\limits_{n o \infty} rac{1}{n} \sum\limits_{t=0}^{n-1} E[TimeInState(X(t))]} = rac{TimeInState(S_1)\pi_{S_1}}{\sum\limits_{k \in S} TimeInState(k)\pi_k}$$

Recall that  $1_A$  is the indicator random variable for the event A. To show why the last equality holds we derive its denominator. A similar derivation holds for the numerator. Let S be the set of states.

$$\lim_{n \to \infty} \frac{1}{n} \sum_{t=0}^{n-1} E[TimeInState(X(t))]$$

$$= \lim_{n \to \infty} \frac{1}{n} \sum_{t=0}^{n-1} [\sum_{k \in S} TimeInState(k) Pr\{X(t) = k\}]$$

$$= \sum_{k \in S} TimeInState(k) \lim_{n \to \infty} \frac{1}{n} \sum_{t=0}^{n-1} Pr\{X(t) = k\}$$

$$= \sum_{k \in S} TimeInState(k) \pi_k$$

To find the long run distribution of the number of usages of a resource for each absorbing recurrent class, we simply sum over all of the states in the class that use the resource the same number of times, the long run fraction of time spent in that state. To find the long run expected number of usages of each resource for each absorbing recurrent class, we simply take the expectation of the random variable ResUsages:

$$E[ResUsages] = \sum_{k \in S} ResUsages(k) Pr\{statek\} = \sum_{k \in S} ResUsages(k) RelTime(k)$$

#### 3.5 Parameter Set of the Stochastic Process

Since firing durations can be zero in the GTPN model, a GTPN can be in two or more states at the same "time". This slightly complicates viewing a GTPN as a stochastic process. In this subsection we discuss that complication and how it can be resolved. The complication is that the right halfline cannot be the parameter set of the GTPN stochastic process. To see this, recall that a stochastic process is a family of random variables indexed by the parameter set and a random variable is a function from the sample space into the reals. If the right halfline were the parameter set, then on some sample path at some parameter t, the random variable X(t) could simultaneously hold more than one value in its range. This contradicts X(t)'s being a function.

This complication is resolved by using a different parameter set. The parameter set used is the lexicographically ordered Cartesian product of the nonnegative reals and the natural numbers. The parameters are assigned in the following way. Consider an arbitrary sample path. At any time t in the nonnegative reals, if there are  $n(n \geq 0)$  instantaneous state changes, then X(t,0) is the state before the first (if any) state change, X(t,1) is the state after the first state change, ... X(t,n-1) is the state after the n-1th state change,  $X(t,m), m \geq n$  is the state after the nth instantaneous state change. Since at most a countably infinite number of instantaneous state changes can occur, the process is never in two or more states at the same "time". Note that the parameter set of the embedded Markov Chain need only be the nonnegative integers with the nth parameter meaning the nth state change.

## 3.6 Computational Issues: Transient States

As discussed in section 3.2, two of the characteristics of the system's performance that we need to determine are the absorption probabilities and mean time to absorption. First Step Analysis was proposed as the method for computing these characteristics. In this section we discuss the computational issues involved in determining those characteristics. Section 3.6.1 discusses some of the efficiency issues involved in implementing First Step Analysis for computing the absorption probabilities. Section 3.6.2 describes an optimization which can significantly accelerate solution of the First Step Analysis equations. Section 3.6.3 covers the analogous material for computing the mean time to absorption. In an important special case that arises frequently in GTPN models, an alternative to First Step Analysis can be used to compute absorption probabilities. Section 3.6.4 describes this still more efficient method.

#### 3.6.1 First Step Analysis

Using First Step Analysis implies that r systems of n linear equations are solved where r is the number of recurrent classes, and n is the number of transient states in the Markov Chain. Solving one system of equations determines the absorption probability of interest for one recurrent class. Since the GTPN is intended to be a practical tool, an efficient solution method is important.

We write the systems of linear equations in matrix form as follows:

$$U_R = P_{TR} + P_T U_R, (3.1)$$

where  $U_R$  is the  $n \times 1$  vector of absorption probabilities for recurrent class R from transient states 0, 1, ..., n-1,  $P_{TR}$  is the  $n \times 1$  vector of one-step transition probabilities from transient state i to any state in R, and  $P_T$  is the  $n \times n$  one-step transition probability matrix for the transient states.

The standard form for a system of linear equations is Ax = b where A is  $n \times n$ , x is  $n \times 1$ , and b is  $n \times 1$ . Our form maps into the standard form by letting A = (P - I),  $x = U_R$ , and  $b = -P_{TR}$ :

$$(P_T - I)U_R = -P_{TR}. (3.2)$$

There are many methods of solving systems of linear equations. Gaussian elimination is the primary direct method. Iterative methods, such as the Gauss-Seidel method, are much more efficient for large matrices. Before selecting a solution method, however, we will discuss an important optimization that can be applied to First Step Analysis.

#### 3.6.2 Optimization of First Step Analysis

An optimization exists that can significantly accelerate solution of the linear systems of equations for First Step Analysis. This optimization is based on a key observation: by permuting the rows and columns of the matrix  $P_T$ ,  $P_T$  can be put into block upper triangular form, where each diagonal block represents the transitions within one transient class of the Markov Chain. To see this, recall that the Markov Chain classes are the strongly connected components in the reachability graph. They thus form a directed acyclic graph (DAG), the condensed graph. As with any DAG, the vertices of the condensed graph can be numbered via a topological sort so that the number assigned to a vertex is always less than the numbers assigned to its children. This numbering defines the permutation that generates the block upper triangular form. We find the strongly connected components using Tarjan's O(n) algorithm, and perform the topological sort on the DAG using another linear-time depth-first search [SED81].

After the permutation, equation 3.2 is of the following form:

$$\begin{pmatrix} A_{11} & A_{21} & \dots & A_{1N} \\ & A_{22} & & A_{2N} \\ & & \ddots & \vdots \\ & & & A_{NN} \end{pmatrix} \begin{pmatrix} U_1 \\ U_2 \\ \vdots \\ U_n \end{pmatrix} = \begin{pmatrix} -P_{1R} \\ -P_{2R} \\ \vdots \\ -P_{nR} \end{pmatrix}$$

(3.3)

where the elements are matrices, each diagonal block  $A_{ii}$  is square of order  $n_i$  and

$$\sum_{i=1}^N n_i = n.$$

The system 3.3 can be solved as a sequence of N smaller problems. Problem i is of order  $n_i$  and the matrix of coefficients is  $A_{ii}$ , i = 1, 2, ..., N. The procedure is as follows [PIS84] (see also [TAR76]):

- 1. Solve the last subsystem, with  $A_{NN}$  as the matrix of coefficients, for the last  $n_N$  unknowns. Compute the vector  $x_N$  of order  $n_N$ .

- 2. Subtract the products  $A_{jN}x_N$  from the right-hand side for j=1,...,N-1. A block upper triangular matrix of order N-1 is obtained, and the procedure is repeated until the complete solution is obtained.

Note that the assumption must be made that the diagonal blocks in Equation 3.2 are nonsingular. The solution of each subsystem can be done by any method for solving linear equations, such as Gaussian elimination or the Gauss-Seidel iteration.

## 3.6.3 Computing Mean Time to Absorption

The mean time to absorption can also be computed using a first-step analysis. One system of n linear equations is solved where n is the number of transient states. Each transient state i has one equation. Starting in state i, the mean time to absorption is the time-in-state for state i plus zero if the next state is in a recurrent class and plus  $P_{ij}$  times the mean time to absorption for state j if state j is transient. Note that the Markov property is again being used. Formally, each equation is of the form:

$$U_i = TimeInState(i) + \sum_{j=0}^{n-1} P_{ij}U_j, \qquad i = 0, 1, ..., n-1$$

If the integer 1 replaces the time-in-state, then the mean number of visits to transient states before absorption can be computed. The mean number of visits to a given set of transient states before absorption can be computed if the time-in-state is replaced by the integer 1 when visiting a state in the given set and is replaced by the integer 0, otherwise.

The discussion in Section 3.6.2 applies here also. In particular, the system of equations can be changed into the form Ax = b, permuted into block lower triangular form, and then solved as outlined.

## 3.6.4 More Efficient Solution of an Important Special Case

In a special case that occurs frequently in GTPN models, an efficient alternative approach based on the condensed reachability graph (i.e. one vertex per strongly connected component) can be used to compute absorption probabilities. In this alternative, probabilities are assigned to the edges leaving each vertex in the condensed graph A depth first search is then done. During the depth first search the probability along each path to each leaf is determined by taking the product of the edge probabilities along the path. The absorption probability for a given leaf is then simply the sum of the path probabilities terminating at that leaf.

The difficulty with this approach is with determining the edge probabilities leaving a vertex in the condensed graph, If all the exit edges originate at the same vertex  $V_1$  within the strongly connected component, then there is not a problem. Find all the edges of which  $V_1$  is the parent that are exit edges. Sum their probabilities as edges in the original graph. The probability of each edge in the condensed graph is its probability in the original graph normalized by this sum.

The problem is when more than one vertex, say  $V_1$  and  $V_2$ , in the original graph are parents of exit edges. Determining the probability that each of these parent vertices is the vertex from which exiting occurs is dependent on the detailed structure of the strongly connected component. Our current implementation uses this condensed graph approach when the special case of one parent vertex in the strongly connected component is met. When the special case is not met, first-step analysis with Gauss-Seidel iteration is used. We plan to implement the optimization described in section 3.6.2 with subsystem solution by Gauss-Seidel iteration.

# 3.7 Computational Issues: Stationary Probability Distributions

In this section we discuss the method we use to calculate the stationary probability distribution for each recurrent class in the Markov Chain. Let R denote a recurrent class with states j=0,1,...,n, and let  $\pi_j$  represent the long run expected fraction of visits to state j, given that the modeled system is absorbed in class R.

Recall that the vector  $\pi_R = (\pi_0, \pi_1, ..., \pi_n)$  is uniquely determined by the following equations:

$$\pi_R = \pi_R P_R \quad \text{and} \quad \sum_{j=1}^n \pi_j = 1,$$

(3.4)

where  $P_R$  is the  $n \times n$  state transition probability matrix for R.

Because the matrix  $P_R$  is sparse, but potentially very large, iterative methods are more practical than direct methods. One of the most widely used iterative methods, the Power Method [JOH82,WIL65], views equation 3.4 as an eigenvalue

problem. In particular,  $\pi_R$  is the eigenvector associated with the unit eigenvalue of  $P_R$ . Applying the Power Method to iteratively solve for  $\pi_R$ , is done as follows:

$$\pi_R^{k+1} = \pi_R^k P_R.$$

Since our current implementation uses the Power Method, the remainder of this section focuses on issues related to it and, in particular, with ensuring convergence.

## 3.7.1 Spectral Distribution

An eigenvalue,  $\lambda$ , of a real  $n \times n$  matrix A, is *strictly dominant*, if its modulus is strictly greater than those of all the other eigenvalues of A. Direct application of the Power Method converges to an eigenvector corresponding to the dominant eigenvalue, if and only if the matrix has a simple, strictly dominant eigenvalue.

This constraint on the direct application of the Power Method can be expressed in terms of the periodicity of the recurrent class in the Markov Chain. In order to make that connection between the spectral distribution and the periodicity of the Markov Chain class, we need the theorems of Perron and Frobenius [CIN75,SEN81,BER79]. These theorems state the following:

An irreducible non-negative matrix, A, has a real, positive, and simple eigenvalue,  $\alpha$ , which is greater than or equal to all other eigenvalues of A in modulus. The eigenvector corresponding to the eigenvalue  $\alpha$  is strictly positive. If A is aperiodic, (i.e.  $A^k > 0$  for some k), then  $\alpha$  is strictly greater than all other eigenvalues of A. A periodic matrix with period  $\delta$ , has exactly  $\delta$  eigenvalues with absolute values equal to  $\alpha$ . These eigenvalues are all distinct and are given by:

$$\lambda_k = \alpha \left[e^{2\pi i/\delta}\right]^{k-1}, k = 1, 2, ..., \delta, i = \sqrt{-1}$$

If A is a stochastic matrix (i.e. all rows sum to one), then  $\alpha=1$ . An aperiodic stochastic matrix thus has a simple unit eigenvalue and all other eigenvalues are of strictly smaller modulus. A periodic stochastic matrix with period  $\delta$  has exactly  $\delta$  eigenvalues of unit modulus all of which are simple. These eigenvalues can be regarded as a set of points around the unit circle in the complex plane, which goes over into itself under a rotation of the plane by the angle  $2\pi/\delta$ .

## 3.7.2 Ensuring Convergence

According to the above discussion, the Power Method can only be applied directly to find the stationary probability distribution when the recurrent class is aperiodic. To handle the case of a periodic recurrent class, the following theorem [STE73] concerning shifting and scaling the matrix becomes important:

**Theorem 3.1** Let A be a complex  $n \times n$  matrix, and let  $\lambda$  be an eigenvalue of A with eigenvector x. Then:

- 1.  $a\lambda$  is an eigenvalue of aA with eigenvector x.

- 2.  $\lambda b$  is an eigenvalue of A bI with eigenvector x.

This theorem allows us to transform the matrix  $P_R$  to ensure that the unit eigenvalue is strictly greater than all other eigenvalues in modulus. In particular, we make the following transformations on  $P_R$ :

$$P_R' = \varepsilon (P_R - I) + I = \varepsilon P_R + (1 - \varepsilon)I$$

$0 < \varepsilon < 1$ .