#### CACHE COHERENCE TECHNIQUES FOR MULTICORE PROCESSORS

by

Michael R. Marty

A dissertation submitted in partial fulfillment of

the requirements for the degree of

Doctor of Philosophy

(Computer Sciences)

at the

UNIVERSITY OF WISCONSIN - MADISON

2008

© Copyright by Michael R. Marty 2008

All Rights Reserved

### Abstract

The cache coherence mechanisms are a key component towards achieving the goal of continuing exponential performance growth through widespread thread-level parallelism. This dissertation makes several contributions in the space of cache coherence for multicore chips.

First, we recognize that rings are emerging as a preferred on-chip interconnect. Unfortunately a ring does not preserve the total order provided by a bus. We contribute a new cache coherence protocol that exploits a ring's natural round-robin order. In doing so, we show how our new protocol achieves both fast performance and performance stability—a combination not found in prior designs.

Second, we explore cache coherence protocols for systems constructed with several multicore chips. In these Multiple-CMP systems, coherence must occur both within a multicore chip and among multicore chips. Applying hierarchical coherence protocols greatly increases complexity, especially when a bus is not relied upon for the first-level of coherence. We first contribute a hierarchical coherence protocol, DirectoryCMP, that uses two directory-based protocols bridged together to create a highly scalable system. We then contribute TokenCMP, which extends token coherence, to create a Multiple-CMP system that is flat for correctness yet hierarchical for performance. We qualitatively argue how TokenCMP reduces complexity and our simulation results demonstrate comparable or better performance than DirectoryCMP.

Third, we contribute the idea of virtual hierarchies for designing memory systems optimized for space sharing. With future chips containing abundant cores, the opportunities for space sharing the vast resources will only increase. Our contribution targets consolidated server workloads on a tiled multicore chip. We first show how existing flat coherence protocols fail to accomplish the memory system goals we identify. Then, we impose a two-level virtual coherence and caching hierarchy on a physically flat multicore that harmonizes with workload assignment. In doing so, we improve performance by exploiting the locality of space sharing, we provide performance isolation between workloads, and we maintain globally shared memory to support advanced virtualization features such as dynamic partitioning and content-based page sharing.

### Acknowledgments

This dissertation is dedicated to my wife Kathleen because it would not have happened without her support, encouragement, patience, and love. I am forever indepted to her. Thank you. Along with Kathleen, my parents always supported my endeavors, never doubted my abilities, and deserve much thanks.

The University of Wisconsin provided me with the opportunities that opened the doors in my life, both personally and professionally. I thank my advisor Mark Hill for supporting my pursuit of this Ph.D. Mark is truly one of the best in the field and I had no idea how good he really is until the latter stages of my graduate student career. The other director of the Multifacet project, David Wood, always provided excellent technical advice and wisdom. I also thank Bart Miller for providing my first opportunity for conducting research. I thank the rest of my committee for their helpful feedback: Guri Sohi, Mikko Lipasti, and Remzi Arpaci-Dusseau. Other faculty that I learned from include Mike Swift, Mary Vernon, Ben Liblit, Susan Horwitz, Tom Reps, Somesh Jha, and Ben Liblit.

Graduate school was a rewarding experience because of all the great students I've met and friends I've made. I can't possibly list the names of all the people that have made a positive impact on my experience over the last 6.5 years. I thank Brad Beckmann for his mentoring, for stimulating my research, and for helping me become a better golfer and sports fan; Kyle Nesbit for becoming an excellent colleague; Dan Gibson for always offering sound technical opinions, witty entertainment, and for the Ostrich wallet; Yasuko Watanabe for coffee break conversations, encouragement, and for showing me around the Bay Area during interviews. Thank you to Philip Wells for literally jump-starting my research on virtual hierarchies and for keeping the coffee machine in running condition. Along with Philip, I studied for the qualifying exam with Matt Allen and Allison Holloway. I thank them for their support and for helping me pass. Natalie Enright for the support, encouragement, and for listening to my various rants and raves over the years. Andy Phelps for providing wisdom that only an experienced engineer can give. Min Xu and Alaa

Alameldeen for offering key advice during the critical moments of the Ph.D. process. Luke Yen for being a good colleague in the Multifacet project. Nidhi Aggarwal and Dana Vantrease for making conferences more fun. Kevin Moore for being an easy-going officemate. The other former and current Multifacet students who've provided encouragement and support, Derek Hower, Milo Martin, Dan Sorin, Carl Mauer, Jayaram Bobba, Michelle Moravan, and more.

Finally I thank the Wisconsin Computer Architecture Affiliates, the Computer Systems Laboratory, the Wisconsin Condor project, and the National Science Foundation for supporting my research.

### Table of Contents

| Abstract          | i                                                          |  |  |  |

|-------------------|------------------------------------------------------------|--|--|--|

| Acknowledgments   | Acknowledgments iii                                        |  |  |  |

| Table of Contents | v                                                          |  |  |  |

| List of Figures   | x                                                          |  |  |  |

| List of Tables    | xii                                                        |  |  |  |

|                   | e Coherence and Multicore                                  |  |  |  |

| 1.1.1             | Interconnect Engineering Constraints                       |  |  |  |

| 1.1.2             | Building Larger Systems with Multicore Building Blocks 4   |  |  |  |

| 1.1.3             | Workload Consolidation and Space-sharing                   |  |  |  |

| 1.1.4             | Bandwidth and Latency Trends                               |  |  |  |

| 1.2 Thes          | is Contributions                                           |  |  |  |

| 1.2.1             | Ring-Order: novel coherence ordering for ring-based CMPs 6 |  |  |  |

| 1.2.2             | Multiple-CMP Coherence: DirectoryCMP and TokenCMP 7        |  |  |  |

| 1.2.3             | Virtual Hierarchies                                        |  |  |  |

| 1.2.4             | Relationship to My Previously Published Work 11            |  |  |  |

| 1.3 Disse         | ertation Structure                                         |  |  |  |

| Chapter 2 Backgr  | ound: Cache Coherence                                      |  |  |  |

| 2.1 Mult          | iprocessor Memory Consistency 13                           |  |  |  |

| 2.1.1             | Overview                                                   |  |  |  |

| 2.1.2             | Impact of Caches on Memory Consistency    15               |  |  |  |

| 2.1.3             | Cache Coherence Invariant and Permissions 17               |  |  |  |

|         | 2.2 | Cache Coherence Techniques for SMP and ccNUMA Machines | 20 |

|---------|-----|--------------------------------------------------------|----|

|         |     | 2.2.1 Snooping on a Bus                                | 21 |

|         |     | 2.2.2 Greedy Snooping on a Ring                        | 23 |

|         |     | 2.2.3 Greedy Snooping on Arbitrary Topologies          | 26 |

|         |     | 2.2.4 Ordered Snooping on Arbitrary Topologies         | 28 |

|         |     | 2.2.5 Directory Coherence                              | 30 |

|         |     | 2.2.6 Token Coherence                                  | 32 |

|         | 2.3 | Hierarchical Coherence                                 | 35 |

|         | 2.4 | Multicore Considerations                               | 36 |

| Chapter | 3 I | Evaluation Methodology                                 | 39 |

| _       |     |                                                        | 39 |

|         | 3.2 | Methods                                                | 39 |

|         | 3.3 | Workload Descriptions                                  | 41 |

|         | 3.4 | Modeling a CMP with GEMS                               | 42 |

| Chapter | 4 ( | Cache Coherence for Rings                              | 45 |

|         | 4.1 | Rings: Motivation and Background                       | 45 |

|         | 4.2 | Ring-based Cache Coherence                             | 49 |

|         |     | 4.2.1 Ordering-Point                                   | 51 |

|         |     | 4.2.2 Greedy-Order                                     | 55 |

|         |     | 4.2.3 Ring-Order                                       | 59 |

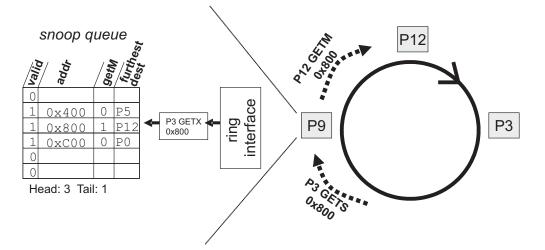

|         | 4.3 | Implementation Issues                                  | 64 |

|         |     | 4.3.1 Interface to DRAM                                | 64 |

|         |     | 4.3.2 Exclusive State                                  | 67 |

|         |     | 4.3.3 Ring Interface                                   | 67 |

|         |     | 4.3.4 Bidirectional Rings                              | 69 |

|         | 4.4 | Evaluation                                             | 71 |

vii

|         |     | 4.4.1  | Target System and Parameters                             | 71  |

|---------|-----|--------|----------------------------------------------------------|-----|

|         |     | 4.4.2  | Performance                                              | 73  |

|         |     | 4.4.3  | Performance Stability                                    | 76  |

|         |     | 4.4.4  | Sensitivity Study                                        | 79  |

|         |     | 4.4.5  | Summary of Evaluation                                    | 83  |

|         | 4.5 | Futu   | re Work                                                  | 83  |

|         |     |        |                                                          | 84  |

|         |     | 4.5.2  | Embedding Ring Protocols in Hierarchy                    | 85  |

|         |     | 4.5.3  | Hierarchical Ring Protocols                              | 86  |

|         | 4.6 | Relat  | ted Work                                                 | 87  |

|         | 4.7 | Conc   | lusion                                                   | 89  |

|         |     |        |                                                          |     |

| Chapter | 5 ( | Cohere | nce for Multiple-CMP Systems                             | 91  |

|         | 5.1 | Mult   | iple-CMP Cache Coherence                                 | 91  |

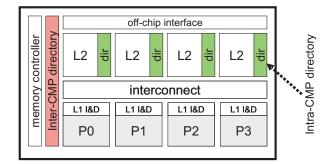

|         | 5.2 | Direc  | ctoryCMP: A 2-level directory protocol for M-CMPs        | 93  |

|         |     | 5.2.1  | DirectoryCMP: Overview                                   | 94  |

|         |     | 5.2.2  | DirectoryCMP: MOESI Intra-CMP Protocol                   | 95  |

|         |     | 5.2.3  | DirectoryCMP: MOESI Inter-CMP Protocol                   | 99  |

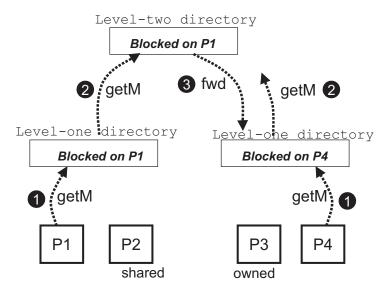

|         |     | 5.2.4  | DirectoryCMP: Inter-Intra CMP Races                      | 100 |

|         |     | 5.2.5  | DirectoryCMP: Implementing Blocking                      | 103 |

|         |     | 5.2.6  | DirectoryCMP: Discussion                                 | 104 |

|         | 5.3 | Toke   | nCMP: Flat for Correctness, Hierarchical for Performance | 105 |

|         |     | 5.3.1  | TokenCMP: Flat Correctness Substrate                     | 106 |

|         |     | 5.3.2  | TokenCMP: Hierarchical Performance Policies              | 110 |

|         |     | 5.3.3  | TokenCMP: Invoking Persistent Requests                   | 114 |

|         |     | 5.3.4  | TokenCMP: Qualitative Complexity Comparison              | 115 |

### viii

| 5.4       | Evalu   | uation                                        | 118 |

|-----------|---------|-----------------------------------------------|-----|

|           | 5.4.1   | Baseline System                               | 118 |

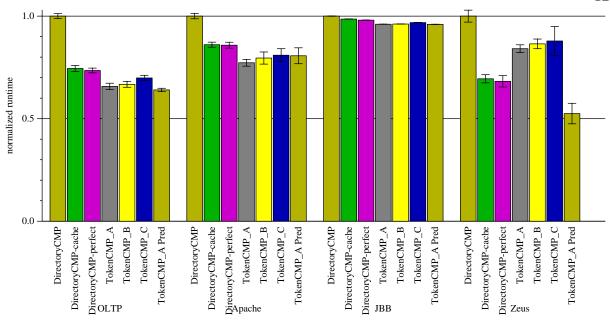

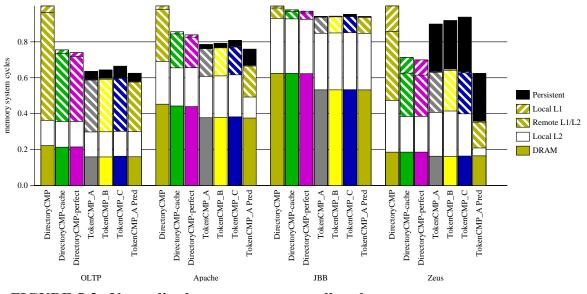

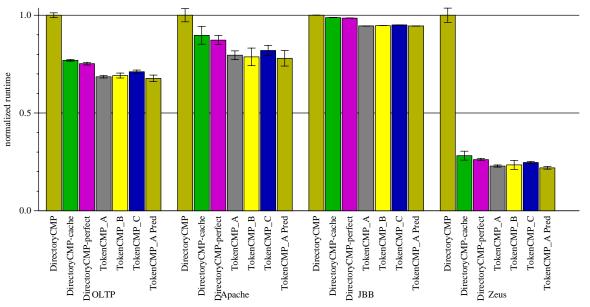

|           | 5.4.2   | Baseline Results                              | 120 |

|           | 5.4.3   | Sensitivity                                   | 126 |

|           | 5.4.4   | Summary of Evaluation                         | 130 |

| 5.5       | Relat   | ed Work                                       | 131 |

| 5.6       | Discu   | ussion and Future Work                        | 132 |

|           | 5.6.1   | TokenCMP                                      | 132 |

|           | 5.6.2   | DirectoryCMP                                  | 133 |

| 5.7       | Conc    | lusion                                        | 134 |

| Chapter 6 | Virtual | Hierarchies                                   | 135 |

| 6.1       | Moti    | vation                                        | 135 |

|           | 6.1.1   | Space Sharing                                 | 135 |

|           | 6.1.2   | Tiled Architectures                           | 136 |

|           | 6.1.3   | Server Consolidation                          | 136 |

| 6.2       | Flat I  | Directory-based Coherence                     | 138 |

|           | 6.2.1   | DRAM Directory w/ Directory Cache             | 139 |

|           | 6.2.2   | Duplicate Tag Directory                       | 140 |

|           | 6.2.3   | Static Cache Bank Directory                   | 142 |

| 6.3       | Virtu   | al Hierarchies                                | 143 |

|           | 6.3.1   | Level-One Intra-VM Directory Protocol         | 145 |

|           | 6.3.2   | Virtual-Hierarchy-Dir-Dir                     | 148 |

|           | 6.3.3   | Virtual-Hierarchy-Dir-Bcast                   | 151 |

|           | 6.3.4   | Virtual Hierarchy Target Assumptions          | 154 |

|           | 6.3.5   | Virtual Hierarchy Data Placement Optimization | 155 |

| 6.3.6 Virtual-Hierarchy-Dir-NULL                               | 157 |

|----------------------------------------------------------------|-----|

| 6.4 Evaluation Methodology                                     | 158 |

| 6.4.1 Target System                                            | 159 |

| 6.4.2 Approximating Virtualization                             | 160 |

| 6.4.3 Scheduling                                               | 161 |

| 6.4.4 Workloads                                                | 161 |

| 6.4.5 Protocols                                                | 162 |

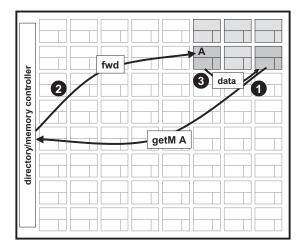

| 6.5 Evaluation Results                                         | 165 |

| 6.5.1 Homogenous Consolidation                                 | 166 |

| 6.5.2 Mixed Consolidation                                      | 174 |

| 6.6 Related Work                                               | 175 |

| 6.7 Future Work                                                | 177 |

| 6.8 Conclusion                                                 | 179 |

| Chapter 7 Summary and Reflections                              | 180 |

| 7.1 Summary                                                    | 180 |

| 7.2 Reflections                                                | 181 |

| References.                                                    | 185 |

| Appendix A: Supplements for Ring-based Coherence (Chapter 4)   | 196 |

| Appendix B: Supplements for Multiple-CMP Coherence (Chapter 5) | 202 |

| Appendix C: Supplements for Virtual Hierarchies (Chapter 6)    | 205 |

## List of Figures

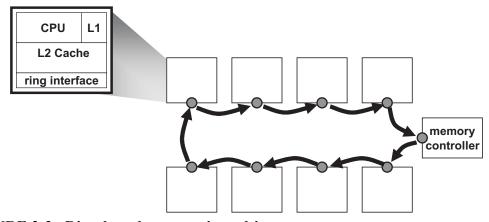

| 1-1  | Base CMP design for ring-based coherence in Chapter 4                      | . 7 |

|------|----------------------------------------------------------------------------|-----|

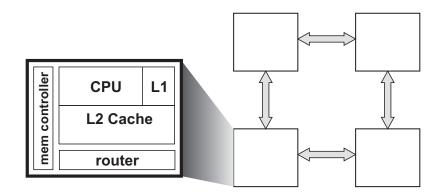

| 1-2  | Base CMP Design for Chapter 5 on Multiple-CMP coherence.                   | . 8 |

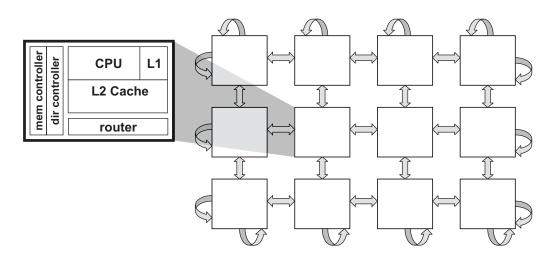

| 1-3  | CMP Design for the Virtual Hierarchies work of Chapter 6                   | 10  |

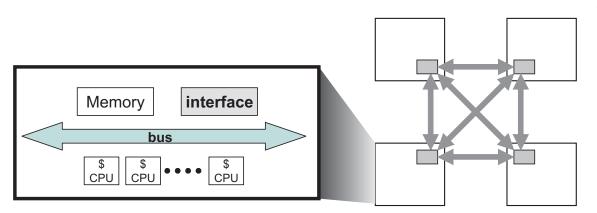

| 2-1  | Bus-based symmetric multiprocessor                                         | 21  |

| 2-2  | Ring-based symmetric multiprocessor                                        | 24  |

| 2-3  | SMP with no interconnect ordering                                          | 27  |

| 2-4  | Directory-based multiprocessor in a 2D torus interconnect                  | 30  |

| 2-5  | Multiprocessor built with bus-based SMP nodes                              | 35  |

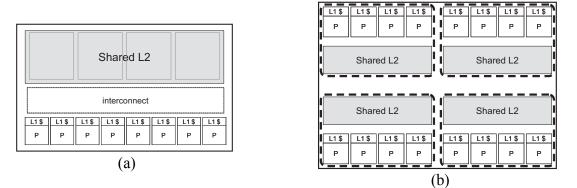

| 2-6  | CMPs with one or more shared L2 caches                                     | 37  |

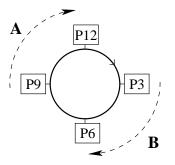

| 4-1  | Example CMPs with a Ring Interconnect                                      | 46  |

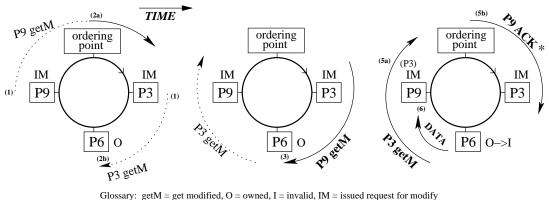

| 4-2  | Ring Reordering.                                                           | 50  |

| 4-3  | Example of Ordering-Point                                                  | 52  |

| 4-4  | ORDERING-POINT Consistency Example.                                        | 55  |

| 4-5  | Example of GREEDY-ORDER                                                    | 56  |

| 4-6  | Example of RING-ORDER                                                      | 60  |

| 4-7  | Example of RING-ORDER's possible use of a content-addressable snoop queue. | 68  |

| 4-8  | Target 8-core CMP with on-chip memory controllers                          | 71  |

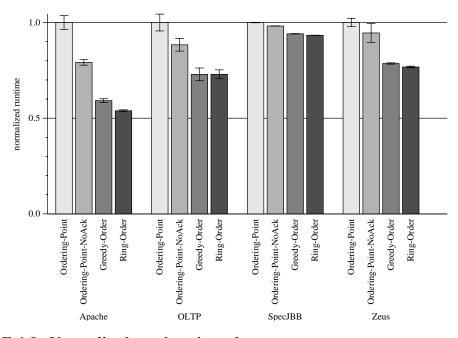

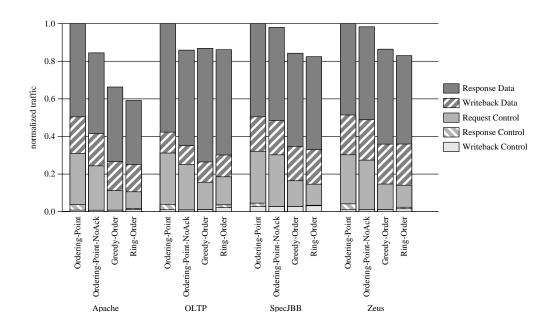

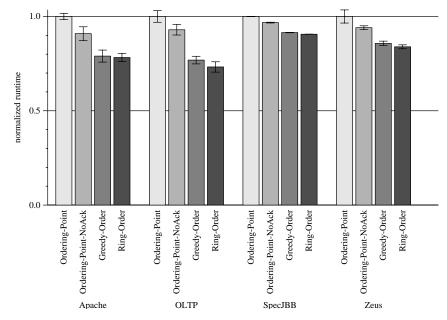

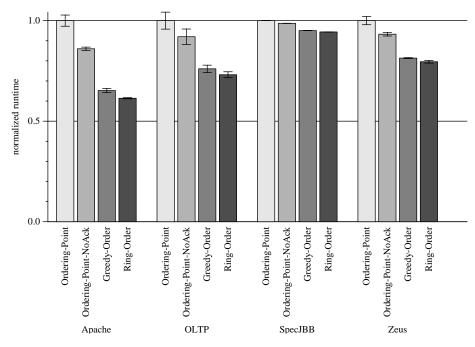

| 4-9  | Normalized runtime, in-order cores                                         | 73  |

| 4-10 | Normalized ring traffic                                                    | 75  |

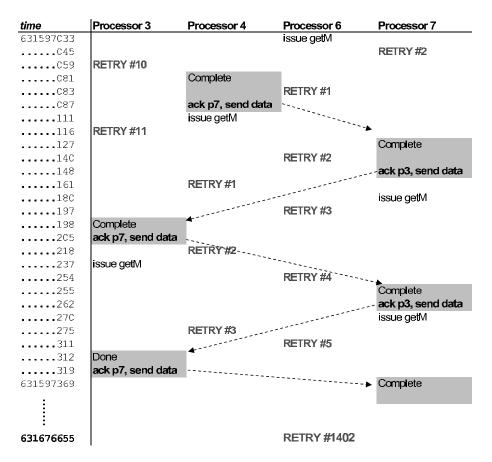

| 4-11 | Excerpt of a GREEDY-ORDER trace running OMPmgrid for a single cache block. | 77  |

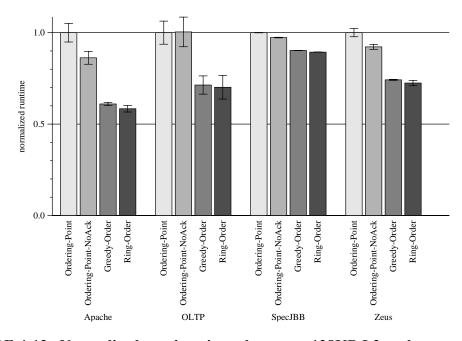

| 4-12 | Normalized runtime, out-of-order cores                                     | 79  |

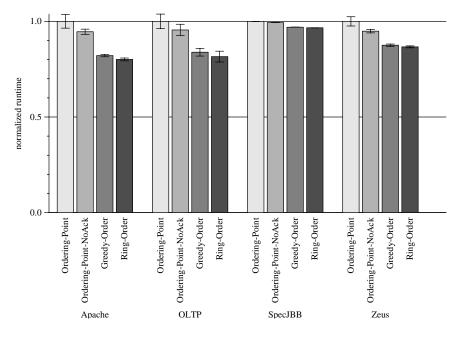

| 4-13 | Normalized runtime, in-order cores, 128KB L2 caches                        | 80  |

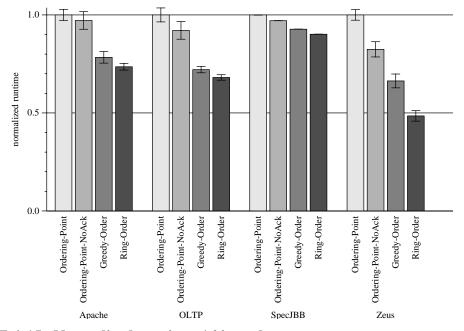

| 4-14 | Normalized runtime, Four in-order cores                                    | 81  |

| 4-15 | Normalized runtime, 16 in-order cores                                      | 81  |

| 4-16 | Normalized runtime, 8 in-order cores, 5-cycle link latency                 | 82  |

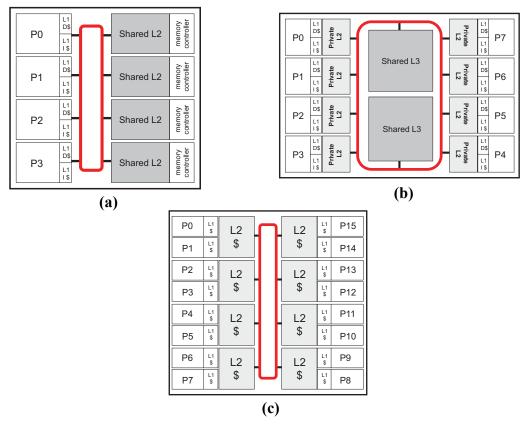

| 5-1  | M-CMP System                                                               | 92  |

| 5-2  | Target CMP assumed for DirectoryCMP                                        | 94  |

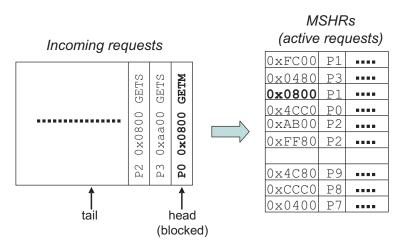

| 5-3  | Blocking Directory Example                                                 | 101 |

| 5-4  | Example of blocking a request                                              | 103 |

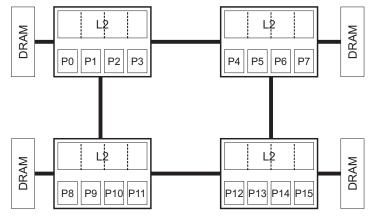

| 5-1  | Baseline 4-CMP Topology                                                    | 119 |

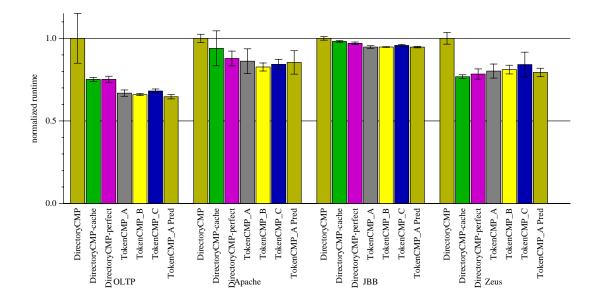

| 5-2  | Normalized runtime                                                                 | <b>xi</b><br>121 |

|------|------------------------------------------------------------------------------------|------------------|

| 5-3  | Normalized memory system stall cycles                                              | 122              |

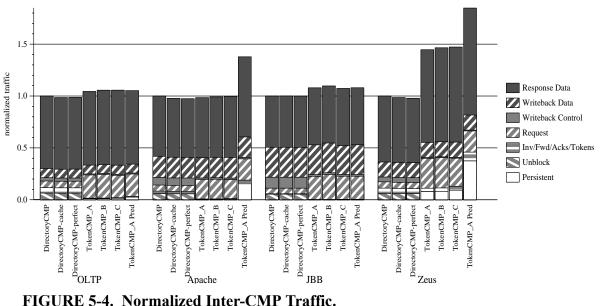

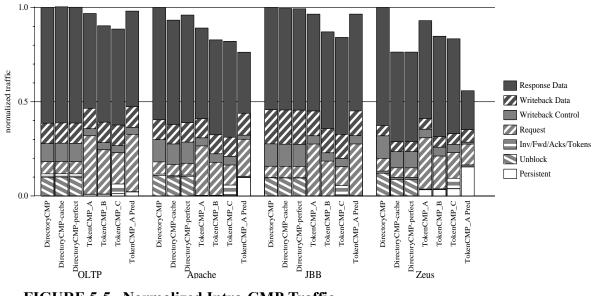

| 5-4  | Normalized Inter-CMP Traffic                                                       | 124              |

| 5-5  | Normalized Intra-CMP Traffic                                                       | 125              |

| 5-6  | Normalized runtime, out-of-order cores                                             | 127              |

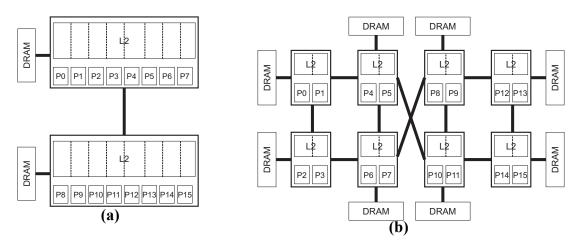

| 5-7  | Alternative 16-core M-CMP Configurations                                           | 128              |

| 5-8  | Normalized runtime, 2 CMPs with 8 cores/CMP                                        | 129              |

| 5-9  | Normalized runtime, 8 CMPs with 2 cores/CMP                                        | 129              |

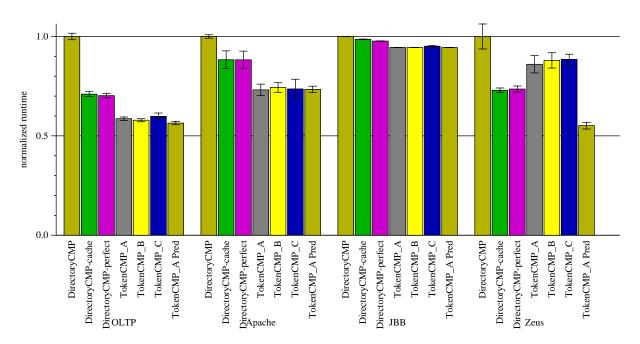

| 6-1  | Tiled CMP architecture                                                             | 137              |

| 6-2  | CMP running consolidated servers                                                   | 137              |

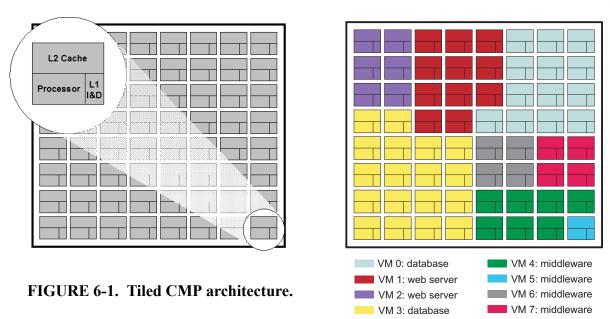

| 6-3  | DRAM-DIR directory protocol with its global indirection for local intra-VM sharing | 139              |

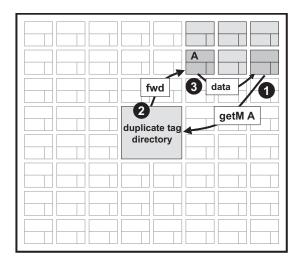

| 6-4  | TAG-DIR with its centralized duplicate tag directory                               | 141              |

| 6-5  | STATIC-BANK-DIR protocol with interleaved home tiles                               | 142              |

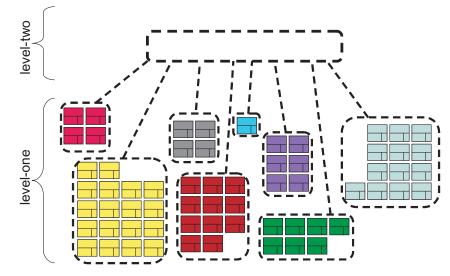

| 6-6  | Logical view of a virtual hierarchy                                                | 144              |

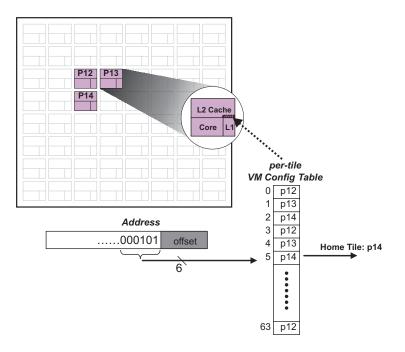

| 6-7  | Example of VM Config Table                                                         | 147              |

| 6-8  | VH's first level of coherence enables fast and isolated intra-VM coherence.        | 148              |

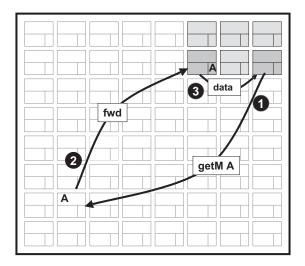

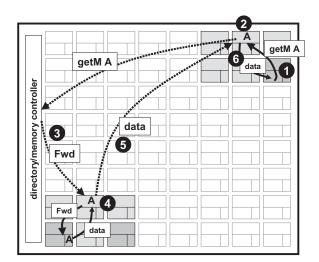

| 6-9  | VH <sub>Dir-Dir</sub> Example                                                      | 150              |

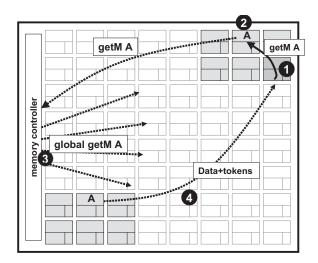

| 6-10 | VH <sub>Dir-Bcast</sub> Example                                                    | 151              |

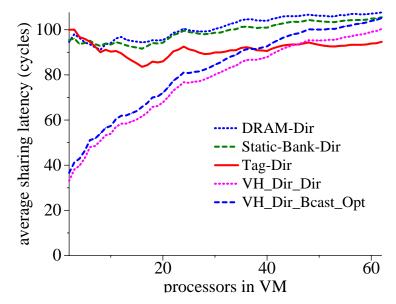

| 6-11 | Microbenchmark result.                                                             | 165              |

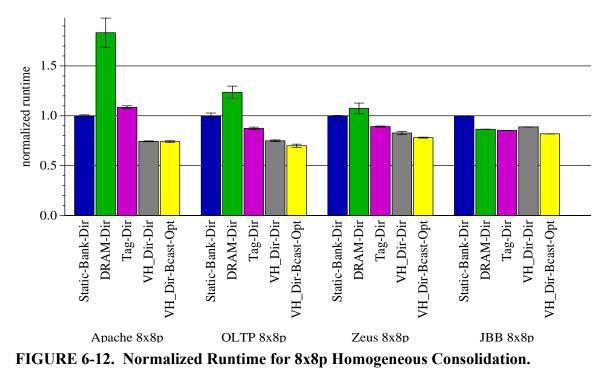

| 6-12 | Normalized Runtime for 8x8p Homogeneous Consolidation                              | 166              |

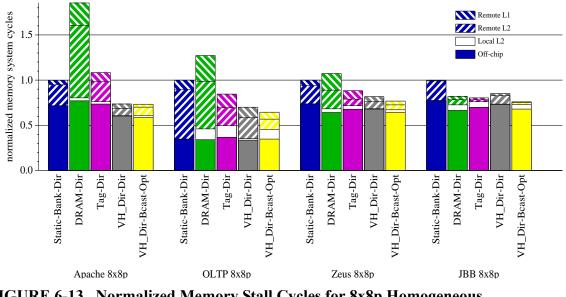

| 6-13 | Normalized Memory Stall Cycles for 8x8p Homogeneous Consolidation                  | 168              |

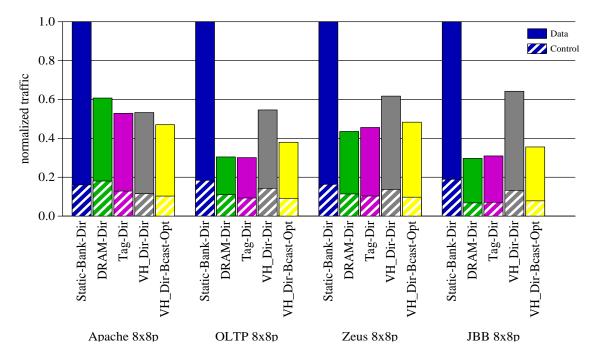

| 6-14 | Normalized On-chip Interconnect Traffic for 8x8p Homogenous Configurations.        | 170              |

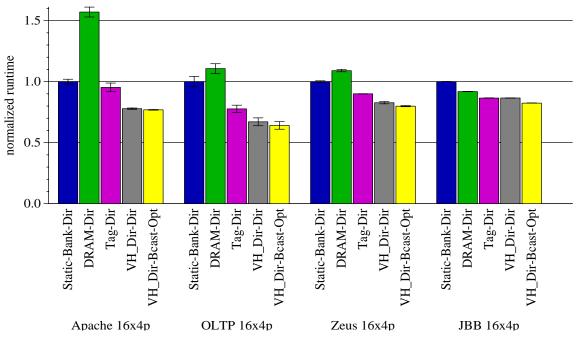

| 6-15 | Normalized Runtime for 16x4p Homogeneous Consolidation                             | 171              |

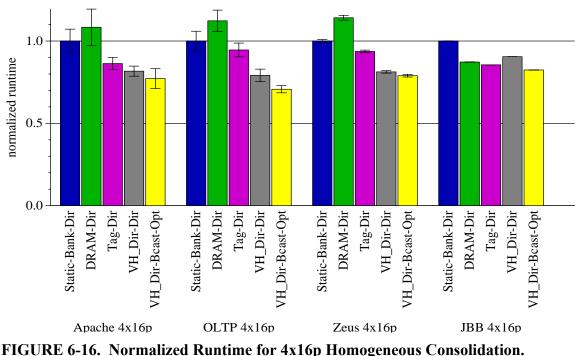

| 6-16 | Normalized Runtime for 4x16p Homogeneous Consolidation                             | 172              |

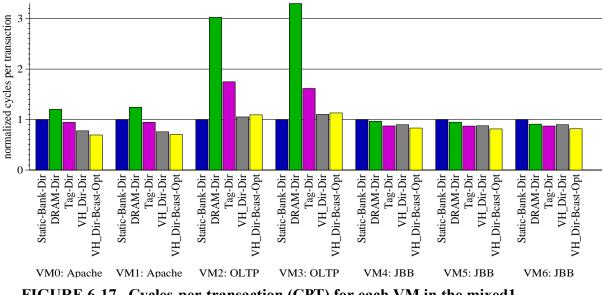

| 6-17 | Cycles-per-transaction (CPT) for each VM in the mixed1 configuration               | 174              |

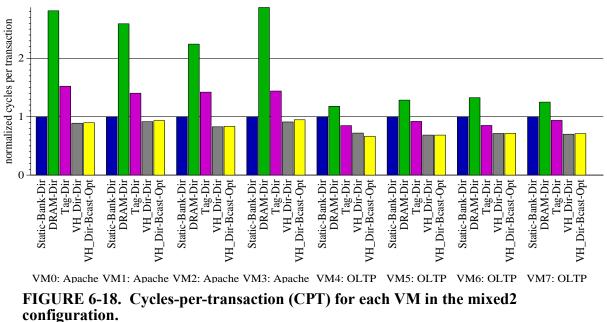

| 6-18 | Cycles-per-transaction (CPT) for each VM in the mixed2 configuration               | 175              |

### List of Tables

| 2-1 | Cache Coherence States                                                          |

|-----|---------------------------------------------------------------------------------|

| 4-1 | Baseline Memory System Parameters for Ring-based CMPs                           |

| 4-2 | Breakdown of L2 Misses                                                          |

| 4-3 | Total processor snoops per cycle                                                |

| 4-4 | MIC hit rate for Ring-Order                                                     |

| 4-5 | Observed L1 Miss Latencies in Cycles (MAX, AVG) 78                              |

| 4-6 | Maximum Observed # Retries for Greedy-Order                                     |

| 4-7 | Distribution of Retries for Greedy-Order                                        |

| 4-8 | Out-of-Order Core Parameters                                                    |

| 5-1 | DirectoryCMP Stable States at Intra-CMP L2 Directory                            |

| 5-2 | Transient Safe States                                                           |

| 5-3 | TokenCMP L2 Controller States    111                                            |

| 5-1 | Baseline M-CMP Memory System Parameters                                         |

| 5-1 | L1 Lookups                                                                      |

| 5-2 | L2 Lookups (including tag access for demand misses) 123                         |

| 5-3 | Persistent Requests caused by Timeout 126                                       |

| 5-4 | Out-of-Order Core Parameters 126                                                |

| 6-1 | Virtual Hierarchy Simulation Parameters                                         |

| 6-2 | Server Consolidation Configurations                                             |

| 6-3 | STATIC-BANK-DIR's Slowdown with Block Address Interleaving                      |

| 6-4 | Relative Performance Improvement from Low vs. High Replication                  |

| A-1 | Raw Numbers for Baseline Results of Section 4.4.2.    196                       |

| A-2 | ORDERING-POINT Cache Controller State Transitions                               |

| A-3 | GREEDY-ORDER Cache Controller State Transitions                                 |

| A-4 | RING-ORDER Cache Controller State Transitions                                   |

| B-1 | DirectoryCMP L2 Controller States                                               |

| B-2 | Raw Numbers for Figures 5-2 and 5-3 (all counts in thousands except avg cycles) |

| C-1 | Raw Numbers for Figure 6-13 (all counts in thousands except average cycles)     |

### Chapter 1

### Introduction

Computing has revolutionized society and serves as an engine of the world's economy. Much of this revolution can be attributed to the advent and incredible progress of the low-cost microprocessor. Advancement of microprocessors is largely driven by Moore's Law, which predicts that the number of transistors per silicon area doubles every eighteen months [103]. While Moore's Law is expected to continue at least into the next decade, computer architects are embarking on a fundamental shift in how the transistor bounty is used to increase performance.

Performance improvements of microprocessors historically came from both increasing the speed (frequency) at which the processors run, and by increasing the amount of work performed in each cycle (e.g., by increasing the amount of parallelism). The increasing transistor bounty has led to different ways of increasing parallelism. Early advancement of microprocessors increased parallelism by widening the basic word length of machines from 4-bits currently to 64-bits. Architects then sought to increase parallelism by executing multiple instructions simultaneously (instruction-level parallelism or ILP) through pipelining techniques and superscalar architectures and to reduce the latency of accessing memory with ever larger on-chip caches. Microprocessors further increased ILP by implementing out-of-order execution engines that completed useful work instead of stalling on data and control dependencies.

It now appears that existing techniques for increasing ILP can no longer deliver performance improvements that track Moore's Law due to energy, heat, and wire delay issues [5]. Therefore, mainstream microprocessor vendors have turned their attention to thread-level parallelism (TLP) by designing chips with multiple processors, otherwise known as Multicore or Chip Multiprocessors (CMPs). By extracting higher-level TLP on multicores, performance can continue to improve while managing the technology issues faced by increasing the performance of conventional single-core designs (uniprocessors).

Industry is embracing multicore by rapidly increasing the number of processing cores per chip. In 2005, AMD and Intel both offered dual-core x86 products [66], and AMD shipped its first quad-core product in 2007 [12]. Meanwhile Sun shipped an 8-core, 32-threaded CMP in 2005 [75] and plans a 16-core version in 2008. It is conceivable that the number of cores per chip will increase exponentially, at the rate of Moore's Law, over the next decade. In fact an Intel research project explores CMPs with eighty identical processor/cache cores integrated onto a single die [64], and Berkeley researchers suggest future CMPs could contain thousands of cores [15]!

#### **1.1 Cache Coherence and Multicore**

The shift towards multicore will rely on parallel software to achieve continuing exponential performance gains. Most parallel software in the commercial market relies on the shared-memory programming model in which all processors access the same physical address space. Although processors logically access the same memory, on-chip cache hierarchies are crucial to achieving fast performance for the majority of memory references made by processors. Thus a key problem of shared-memory multiprocessors is providing a consistent view of memory with various cache hierarchies. This *cache coherence* problem is a critical correctness and performance-sensitive design point for supporting the shared-memory model. The cache coherence mechanisms not only govern communication in a shared-memory multiprocessor, but also typically determine how the

memory system transfers data between processors, caches, and memory. Assuming the sharedmemory programming model remains prominent, future workloads will depend upon the performance of the cache coherent memory system and continuing innovation in this realm is paramount to progress in computer design.

Cache coherence has received much attention in the research community, but the prior work targeted multiprocessor machines (MPs) comprised of multiple single-core processors. Perhaps the most important difference in the design of CMPs, compared with prior MPs, is the opportunity to take a holistic approach to design. Prior machines were usually constructed of commodity uniprocessors where the design focus was on single-core performance. The cache coherent memory system is now a first-order design issue at the chip level. We identify some concrete CMP-specific trends and opportunities below.

#### **1.1.1 Interconnect Engineering Constraints**

Many cache coherence schemes are tightly coupled to the interconnect ordering properties. The interconnect of future multicores will face different engineering constraints than prior multiprocessors [81]. Not only do the electrical characteristics of on-chip networks differ from their off-chip counterparts, there now exists a complex trade-off between interconnect resources, cache capacity, processor capability, and power usage [79] that did not exist when uniprocessors were designed indepedently from the multiprocessor interconnect.

Most of the commercially successful multiprocessors used buses to interconnect the uniprocessors and memory. With the increasing numbers of cores within a CMP, a bus will suffer scalability limits. Prior solutions for more scalable multiprocessors implement packet-switched interconnects in topologies such as grids or tori. Multicores likely will eventually integrate packet-switched interconnects on-chip, but intermediate solutions may be preferable until technology scaling further reduces the cost of packet-switching. Furthermore, as we will see in Chapter 2, implementing coherence on such an unordered interconnect requires additional techniques such as using additional levels of indirection. CMPs may implement an interconnect that is simpler than a packet-switched interconnect yet offers better properties than a bus. A ring is one such alternative explored in Chapter 4 of this dissertation.

#### 1.1.2 Building Larger Systems with Multicore Building Blocks

Vendors have long showed an interest in leveraging commodity hardware to build larger, more capable systems. The majority of these prior systems integrated several commodity uniprocessors to create a larger shared-memory machine. In this new era, the basic commodity building block is now a multiprocessor itself instead of a uniprocessor. Therefore hierarchical systems, requiring hierarchical cache coherence techniques, will become much more widespread.

Memory systems are complex and difficult to implement correctly, as evident by the number of bugs in shipped products [113]. A considerable portion of memory system complexity comes from the coherence protocol. While model checking techniques [36, 109] have successfully found subtle bugs during the design phase [69, 100], hierarchical coherence makes the state-space of the protocols explode. In Chapter 5, we explore hierarchical coherence in a M-CMP system and demonstrate a new framework for making coherence flat for correctness, yet hierarchical for performance.

#### 1.1.3 Workload Consolidation and Space-sharing

Server consolidation is becoming an increasingly popular way to manage systems. For example, web and database programs running on separate servers will consolidate onto a single server running under virtual machines. Server consolidation, and more generally workload consolidation, can increase utilization of machines and reduce administrative costs. Opportunities for consolidation may also increase as the number of threads per CMP rise faster than the ability of programmers to exploit them for single programs. Rather than just *time sharing* jobs on one or a few cores, we expect abundant cores will encourage a greater use of *space sharing* [42]. With space sharing, single- or multi-threaded jobs are simultaneously assigned to separate groups of cores for long time intervals. Currently proposed CMP memory systems do not appear to target consolidated workloads with space sharing of resources. Chapter 6 presents techniques motivated by workload consolidation and space sharing.

#### 1.1.4 Bandwidth and Latency Trends

Two primary technology trends driving CMP design and research is increasing on-chip wire delay and the increasing gap between processor and memory speed. In conventional processors of the 80s and early 90s, the entire chip could be reached in a single cycle. Technology scaling in the coming decade may require dozens of cycles for a signal to traverse from one edge of the die to the other [44]. Moreover, with the rising gap between processor and memory speed, maximizing on-chip cache capacity is crucial to attaining good performance.

Memory system designers employ hierarchies of caches to manage latency and bandwidth. Many of today's CMPs (including research designs) assume private L1 caches and a shared L2 cache. At some point, however, the limited bandwidth and latency of a single shared L2 cache will require additional levels in the hierarchy. One option designers can consider is implementing a physical hierarchy that consists of multiple clusters, where each cluster consists of a group of processor cores that share an L2 cache. The effectiveness of such a physical hierarchy, however, may depend on how well the applications map to the hierarchy. In Chapter 6, we develop a mechanism to create a virtual hierarchy to match the workload's characteristics.

#### **1.2 Thesis Contributions**

This section describes the research contributions of the dissertation. Although each contribution targets a different CMP design point, the concepts readily adapt to other designs as discussed throughout the dissertation.

#### **1.2.1 RING-ORDER: novel coherence ordering for ring-based CMPs.**

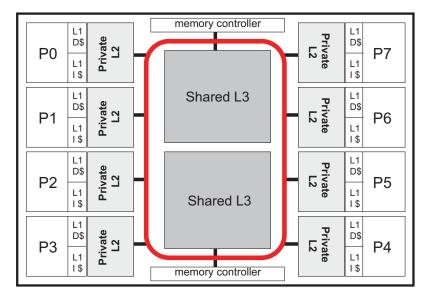

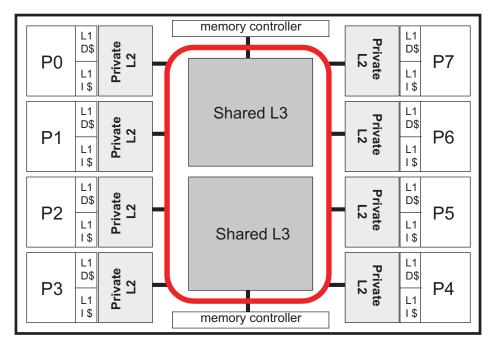

Chapter 4 develops a new method of coherence for ring-based interconnects. Rings are emerging as a viable interconnect for future CMPs. Compared to buses, crossbars, and packet-switched interconnects, rings may offer a preferred compromise between speed, scalability, complexity, and resource usage. Rings are currently used by the IBM Cell [71, 61] and are under consideration by Intel for future CMPs [63]. Figure 1-1 illustrates the base CMP design, with eight cores and shared L3 caches, targeted in Chapter 4.

Unfortunately the order of a ring is not the same as the order of a bus. Therefore coherence protocols for rings must specifically consider the ordering of a ring. An existing ring-based protocol uses a greedy order (GREEDY-ORDER) where a request may require an unbounded number of retries to resolve races. Another approach re-establishes the order of a bus by using an ordering

FIGURE 1-1. Base CMP design for ring-based coherence in Chapter 4

point. Alternatively a protocol that relies on no interconnect ordering, such as a directory-based scheme, can deploy on a ring with considerable protocol overhead.

The primary contribution of Chapter 4 develops a new coherence protocol called RING-ORDER. This scheme exploits the ordering properties of a ring by completing requests in the natural round-robin order. A secondary contribution demonstrates the use of an ordering point (ORDERING-POINT) to re-establish a total bus order on a ring and compares it with RING-ORDER and GREEDY-ORDER. We show that RING-ORDER performs up to 86% faster than ORDERING-POINT and offers stable performance by never using retries.

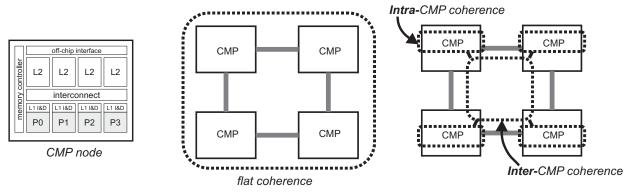

#### **1.2.2 Multiple-CMP Coherence: DirectoryCMP and TokenCMP**

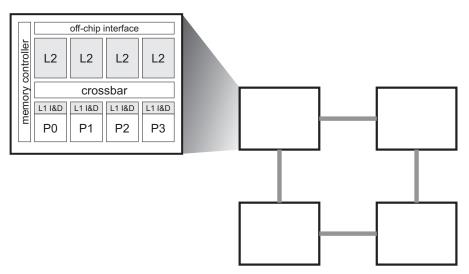

Chapter 5 considers coherence for systems comprised of multiple CMPs (Multiple-CMPs or M-CMPs). M-CMP systems will require cache coherence both within a CMP and between CMPs. One approach uses hierarchical coherence by combining an intra-CMP protocol for on-chip coherence with an inter-CMP protocol for off-chip coherence. Unfortunately coupling two proto-

FIGURE 1-2. Base CMP Design for Chapter 5 on Multiple-CMP coherence.

cols together greatly increases complexity. Another approach completely ignores the hierarchy of an M-CMP system by using a protocol that makes no distinction between an on- and off-chip cache. Although applying existing, flat protocols to an M-CMP can offer correct function, performance will suffer because the physical hierarchy is not exploited for lower latency and bandwidth.

The primary contribution of Chapter 5 develops the TokenCMP framework for M-CMP coherence. TokenCMP extends token coherence [93] to make the system flat for correctness. The flat correctness substrate greatly eases complexity and allows the successful model-checking of the system. We then develop simple broadcast-based performance policies to exploit the physical hierarchy in the common case.

A secondary contribution develops a detailed specification of a protocol, DirectoryCMP, that uses directories for both intra-CMP and inter-CMP coherence. This two-level directory approach gives considerable scalability to the system, but comes with a high level of complexity due to various races possible between the protocols. We solve the problem of races by using blocking directories with an algorithm for avoiding deadlock between dependent directories. Both DirectoryCMP and TokenCMP operate on completely unordered interconnects.

Chapter 5 primarily evaluates TokenCMP and DirectoryCMP in an M-CMP configuration shown in Figure 1-2. Although the number of cores in this target design is modest, the techniques we propose in Chapter 5 will generalize to slightly larger systems. We assume no interconnect ordering for either the on-chip and off-chip interconnection networks to ensure our schemes scale to increasing cores-per-CMP and CMPs. In addition to reducing complexity, we also show that TokenCMP can perform up to 32% faster than DirectoryCMP.

#### **1.2.3 Virtual Hierarchies**

Chapter 6 proposes the virtual hierarchy framework as a new way to build CMP memory systems. In a virtual hierarchy (VH), we overlay a coherence and cache hierarchy onto a fixed physical system. Unlike a physical hierarchy, a virtual hierarchy can adapt to fit how workloads are space-shared for improved performance and performance isolation.

Chapter 6 applies a virtual hierarchy to a case study of a many-core CMP running several consolidated multithreaded workloads with space-sharing of on-chip resources. With the large number of threads available in future CMPs, consolidating workloads onto a single machine will become more prevalent. Yet proposed memory systems for future CMPs do not target spaceshared workload consolidation.

The primary contribution we make develops a two-level virtual hierarchy on a physically-flat CMP that harmonizes with workload assignment. A virtual hierarchy fulfills our goals of performance, performance stability, and globally-shared memory to support dynamic reconfiguration

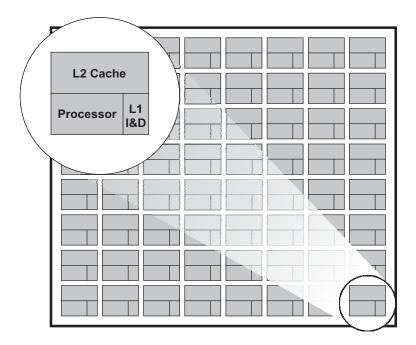

FIGURE 1-3. CMP Design for the Virtual Hierarchies work of Chapter 6

and content-based page sharing. To implement a virtual hierarchy, we develop two protocols:  $VH_{Dir-Dir}$  and  $VH_{Dir-Bcast}$ .  $VH_{Dir-Dir}$  is an extension of DirectoryCMP, using fully mapped directories at both levels, to create a virtual hierarchy.  $VH_{Dir-Bcast}$  uses the same first-level protocol as  $VH_{Dir-Dir}$ , but reduces global memory state by instead using a token-based broadcast protocol at the second level. Compared to flat directory schemes, we show that VH protocols offer superior performance and performance isolation when running consolidated workloads. In particular,  $VH_{Dir-Dir}$  improves performance by up to 45% compared to the best-performing baseline protocol.

The long-term CMP we consider in Chapter 6 is a tiled architecture consisting of 64 tiles as shown in Figure 1-3. Each tile contains an in-order processor core, private L1 instruction and data caches, and an L2 cache bank. The CMP implements a packet-switched interconnect in an 8x8 grid topology. While a tiled architecture offers no physical hierarchy, the virtual hierarchy offers the latency and bandwidth advantages of a hierarchy without actually building one.

#### **1.2.4 Relationship to My Previously Published Work**

This dissertation encompasses work that previously appeared in three conference publications. The work on ring-based cache coherence appears in the proceedings of the 39th International Symposium on Microarchitecture [96], co-authored with Mark Hill. Chapter 4 describes the work in more detail and considers additional issues not addressed in the paper. The evaluation in this dissertation also assumes better cache snooping capabilities and performs additional sensitivity analysis to ring and CMP parameters.

The work on TokenCMP work was previously published in the proceedings of the 11th annual High-Performance Computer Architecture conference [95], with co-authors include Jesse D. Bingham, Alan J. Hu, Milo M. Martin, Mark D. Hill and David A. Wood. Chapter 5 includes more description and specification of DirectoryCMP, more qualitative complexity arguments for TokenCMP, an additional TokenCMP performance protocol, and an updated evaluation with more sensitivity analysis. However Chapter 5 does not include the paper's model checking results because it was performed by other co-authors.

The work on Virtual Hierarchies is published, with co-author Mark Hill, in the proceedings of the 34th International Symposium on Computer Architecture [97] as well as the 2008 edition of IEEE Micro's Top Picks [98]. Chapter 6 changes some naming conventions, adds detail to protocol descriptions, and contains some minor evaluation differences.

#### **1.3 Dissertation Structure**

Chapter 2 presents a background on the cache coherence problem and an overview of prior solutions for SMPs. We also discuss differences when considering coherence for CMPs. Chapter

3 discusses the tools, methodology, and workloads used for evaluation. Chapter 4 presents our work on ring-based cache coherence protocols. Chapter 5 develops hierarchical coherence for M-CMP systems. Chapter 6 presents the work on virtual hierarchies. Finally, Chapter 7 concludes and offers reflections on the research.

### Chapter 2

### Background: Cache Coherence

This chapter presents an overview of the cache coherence problem and some related work on existing techniques. The scope and the amount of related work is large, so we focus on the aspects most fundamental and related to the research in this dissertation. Section 2.1 develops the cache coherence problem in terms of multiprocessor memory consistency. Section 2.2 presents back-ground on existing coherence techniques developed for prior multiprocessors. Section 2.3 considers some existing hierarchical systems. In Section 2.4, we discuss some of the impacts that emerging CMP-based multiprocessors have on the cache coherence problem.

#### 2.1 Multiprocessor Memory Consistency

#### 2.1.1 Overview

Serial programs running on von Neumann machines present a simple intuitive model to the programmer. Instructions *appear* to execute in the order specified by the programmer or compiler regardless if the implementation of the machine actually executes them in a different order. Importantly, a program's load returns the last value written to the memory location. Likewise a store to a memory location determines the value of the next load. This definition leads to straightforward implementations and semantics for programs running on a single uniprocessor.

Multithreaded programs running on multiprocessor machines complicate both the programming model and the implementation to enforce a given model. In particular, the value returned by a given load is not clear because the most recent store may have occurred on a different processor core<sup>1</sup>. Thus architects define *memory consistency models* [3] to specify how a processor core can observe memory accesses from other processor cores in the system.

Sequential consistency is a model defined such that the result of any execution is the same as if the operations of all processors were executed in some sequential order, and the operations of each individual processor appear in this sequence in the order specified by its program [83]. Other, more relaxed consistency models [3] can give the system builder more flexibility in implementing optimizations to reduce memory latency. For example, a relaxed memory model makes it straightforward to implement write buffers with bypassing.

While relaxed models can improve performance by retiring memory instructions before they have been observed by other processors in the system, proper synchronization of multithreaded programs is still required. Systems using a relaxed memory consistency model either include additional instructions that allow a programmer to enforce orderings between loads and stores [49], or define semantics such that a programmer can synchronize using carefully constructed sequences of loads and stores.

Regardless of sequential or relaxed consistency, the addition of cache memories impacts how consistency is implemented.

This chapter on background material will use the term "processor" to refer to a single processing element and its private cache hierarchy. Terminology in the multicore era is evolving to use the term "processor" to refer to an entire chip that consists of multiple "processor cores" or just "cores". Future chapters will adhere to this new terminology by using the term "core" instead of "processor" when referring to a single processing element. "Multiprocessors" will refer to systems that contain several cores, including multicore and prior systems constructed of single-core chips.

#### 2.1.2 Impact of Caches on Memory Consistency

Cache memories have been paramount in facilitating the rapid performance progress of microprocessors over the past twenty years. They allow processor speeds to increase at a greater rate than DRAM speeds by exploiting locality in memory accesses. The beauty of caches is their effective operation with very little impact on the programmer or compiler. In other words, details of the cache hierarchy do not affect the instruction set architecture and their operation is all hard-ware-based and automatic from a programmer's point-of-view.

While implementing a cache hierarchy had little ramification on a uniprocessor's memory consistency, caches complicate multiprocessor memory consistency. The root of the problem lies in store propagation. While two processors in a system, P1 and P2, may both load the same memory block into their respective private caches, a subsequent store by either of the processors would cause the values in the caches to differ. Thus if P1 stores to a memory block present in both the caches of P1 and P2, P2's cache holds a potentially stale value because of P1's default operation of storing to its own cache. This cache incoherence would not be problematic if P2 never again loads to the block while still cached or if the multiprocessor did not support the transparent shared-memory abstraction. But since the point of multiprocessor memory models is to support shared by P1, as defined by the model. That is, P1's store must potentially affect the status of the cache line in P2's cache to maintain consistency, and the mechanisms for doing so are defined as *cache coherence*.

A system is cache coherent if the execution results in a valid ordering of reads and writes to a memory location. One valid ordering is a total order of all reads and writes to a location such that the value returned by each read operation is the value written by the last write to that location. More formally, a read of address A by processor P1 ( $\text{Read}_{P1}$  A) is ordered after a write of address A by processor P2 (Write<sub>P2</sub> A) if the value received by ( $\text{Read}_{P1}$  A) is the value written by (Write<sub>P2</sub> A) or some other write to A ordered between (Write<sub>P2</sub> A) and ( $\text{Read}_{P1}$  A). In a cache coherent memory system, any write must be totally ordered with respect to other writes and reads to the same location. However a common optimization allows a partial ordering of reads to a location such that at any time in the system, either a single writer may exist or multiple readers (but not both). An important implication of this definition, known as *write serialization*, is that all writes to a location are seen in the same order to all processors.

Cache coherence is an important, but incomplete piece of multiprocessor memory consistency. The mechanisms and protocols to implement cache coherence typically do so at a block (or line) granularity such that interactions between different cache blocks are mostly independent. Further mechanisms, usually implemented in the processor's load and store unit, complete the consistency model implementation by enforcing *when* various loads and stores to *different* blocks can retire. Nonetheless, to enforce ordering requirements of a given consistency model, it is the responsibility of the coherence protocol to indicate when a load or store operation to a block *completes*. Thus the strategy of this dissertation treats cache coherence as an independent issue of memory consistency that is necessary but not sufficient to implement a given model. All the protocols we discuss can support any memory consistency model, but our descriptions will assume sequential consistency.

#### 2.1.3 Cache Coherence Invariant and Permissions

A commonly used approach to cache coherence encodes a permission to each block stored in a processor's cache. Before a processor completes a load or a store, it must hit in the cache and the cache must hold the appropriate permission for that block. If a processor stores to a block that is cached by other processors, it must acquire store permission by revoking read permission from other caches. This type of protocol is called an invalidation-based approach which maintains the following invariant for a given cache block:

# At any point in logical time, the permissions for a cache block can allow either a single writer or multiple readers.

Permissions in a cache are reflected by a *coherence state* stored in the cache tag for a block. States used by most existing cache coherence protocols are typically a subset of those in Table 2-1 [128]. The *coherence protocol* ensures the invariants of the states are maintained. For example, a processor can write to a block if the state is M or E because the coherence protocol ensures that all other copies of the block in other caches are in state I. A processor can read the block when the cache state is one of {M, E, O, S}. The cache coherence protocol enforces the coherence invariant through state machines at each cache controller and by exchanging messages between controllers.

States M, S, and I represent the minimum set that allow multiple processors to simultaneously hold read permission for a block (in State S), or to denote that a single processor holds write permission (State M). State O and E are used to implement coherence protocol optimizations. For example, State O helps the protocol satisfy a read request by accessing the cache of another processor (the owner) instead of accessing slower DRAM. State E optimizes for unshared data by giving a processor implicit write permission on a read miss.

|                  | permission  | invariant                       |

|------------------|-------------|---------------------------------|

| Modified (M)     | read, write | all other caches in I or NP     |

| Exclusive (E)    | read, write | all other caches in I or NP     |

| Owned (O)        | read        | all other caches in S, I, or NP |

| Shared (S)       | read        | no other cache in M or E        |

| Invalid (I)      | none        | none                            |

| Not Present (NP) | none        | none                            |

**TABLE 2-1.** Cache Coherence States

If a processor's read misses in its cache, or the block is in the Invalid state, the processor issues a *GETS* (or *GET\_INSTR* for an instruction read miss) coherence request to obtain data for read permission. The coherence protocol must obtain the most recently stored data to that block and ensures that write permission is revoked from other processors. This means that any processor in one of states {M, O, E} must supply the data and can remain in a state with read-only permission (O or S). However if no cache exists in state M, O, or E, then memory should supply the data. The requesting processor must ultimately end up in a state with read permission (M, O, E, or S) to finish its request.

If a processor misses in its cache for a write, or the block is not in state M or E, the processor issues a *GETM* coherence request. The coherence protocol must obtain the most recently stored data to that block, like a GETS, but also ensures read permission in all other caches is revoked. If a processor already holds the data in read-only permission, a possible optimization implements an UPGRADE message that only invalidates other caches instead of obtaining the data. This dissertation does not discuss or implement the UPGRADE message because we seek to maintain conceptual simplicity and because our empirical data shows they would rarely be used.

Satisfying a processor's GETS or GETM request requires several mechanisms of the cache coherence protocol to obtain the appropriate data and coherence permission. Many of these mechanisms are listed below:

- GETS messages must reach the processor in state M, E, or O, if one exists, to obtain the most-recently written value.

- GETM message must reach all processors in state M, O, E, S.

- The protocol must provide indication to the processor when its GETM request can assume all other processors have invalidated their caches.

- A processor must eventually succeed in completing its GETS or GETM operation. This property is also referred to as the *liveness* of the processor, or as a system that prevents *starvation* of a processor.

- The protocol must determine when memory responds. While cache tags can be augmented to indicate a coherence state, doing so for standard DRAM chips is a significant compromise.

- The protocol must ensure the coherence invariant in the face of other concurrent requests for the same block. This problem is exacerbated by unordered interconnects that can induce many *race conditions* (or races). A coherence race occurs when the timing of one request can interact with another concurrent request.

- The protocol must correctly replace dirty data to DRAM.

Before we further discuss invalidate-based coherence protocols, we briefly touch upon an alternative approach to coherence. An alternative to revoking coherence permission from caches is to *update* the values of other caches on any store if they hold the block. Examples of update protocols include the Xerox Dragon [16] and DEC Firefly [133]. While update protocols immedi-

ately propagate the most recent store value to all other caches holding the block, the main disadvantages are the amount of bandwidth consumed and the difficulty in preserving write serialization. In particular, when a processor stores to a block multiple times before another processor reads the block, all updates except for the most recent were unnecessary. And when two processors attempt to update a value simultaneously, achieving atomicity of a single write with respect to another can become challenging. For these reasons, most systems implement invalidate-based coherence.

#### 2.2 Cache Coherence Techniques for SMP and ccNUMA Machines

This section presents background work on cache coherence protocols for a large class of prior shared-memory multiprocessor machines. Prior multiprocessors were generally classified as symmetric multiprocessors (SMPs) or cache-coherent non-uniform memory access multiprocessors (ccNUMA). SMP machines generally offered the same memory access latency to all processors across the entire address space. On the other hand, ccNUMA machines exhibited different access latencies depending on memory region and the physical location of a processor.

Sections 2.2.1 through 2.2.4 present *snooping* protocols. We consider snooping protocols as those that broadcast a coherence request to all nodes such that distributed algorithms and state machines can implement the cache coherence protocol. In these systems, a node is considered a uniprocessor with its private cache hierarchy. In Section 2.2.5, we present the background on directory-based systems. Finally in Section 2.2.6, we review an approach to coherence called token coherence proposed in 2003.

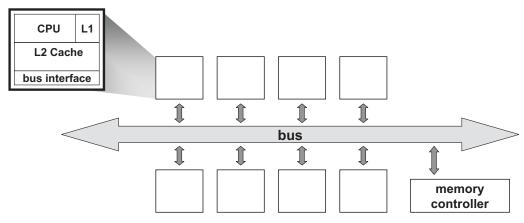

FIGURE 2-1. Bus-based symmetric multiprocessor

#### 2.2.1 Snooping on a Bus

The first widely-adopted approach to cache coherence is snooping on a bus. A bus connects all components to an electrical, or logical, set of wires. A bus provides key ordering and atomicity properties that enable straightforward coherence operations. First, all endpoints on a bus observe transmitted messages in the same *total order*. Second, buses provide *atomicity* such that only one message can appear on the bus at a time and that all endpoints observe the message. Third, buses implement *shared lines* that allow any endpoint to manipulate a signal or condition that is globally visible to all other endpoints during a bus transaction. Shared lines facilitate both bus arbitration and cache coherence operations. For example, a shared *owner* line can indicate if any processor is in State S.

A bus-based SMP is shown in Figure 2-1 where each processor and memory node in the system connects to the bus. With all coherence messages broadcast on a bus and with message arrivals ordered the same way for all nodes, coherence controllers at each node implement a state machine to maintain proper coherence permissions and to potentially respond to a request with data. For example, when a GETM request appears on the bus, all nodes *snoop* their caches and the memory controller prepares to fetch the data from DRAM. If the tag exists in a processor's cache in State S, the coherence state is changed to I in order to revoke read permission. If the processor's cache contains a tag in state {M, E, or O}, it asserts the shared owned line to inhibit a memory response and then places data on the bus before invalidating its cache tag. The shared owned line provides an important function in a bus-based protocol by signalling when the memory controller should not respond with data that is modified in a processor's cache. Once a processor is able to transmit its request on the bus, its transaction will complete. Therefore the liveness (and fairness) of a bus-based snooping protocol only depends on the method of bus arbitration employed.

To implement sequential consistency (or a memory ordering instruction in a relaxed consistency model), the processor must know when it can retire the load or store instruction. For a store instruction that required a GETM coherence request, enforcing strict ordering requires notification when the GETM appears to have completed invalidating all other caches. For a load instruction that required a GETS coherence request, any prior stores must appear to have completed. But since a bus serializes all requests, the bus can indicate completion before caches have actually completed snooping the message. Therefore, for a GETM, a processor can assume all other caches have invalidated their caches as soon as its own GETM message appears on the bus. This assumption may require other actions to maintain sequential consistency, such as requiring a cache controller to complete buffered snooping operations before transmitting a new message on the bus [114].

Replacements in a bus-based snooping protocol are straightforward. Unmodified copies (E and S state) can silently replace by taking no action. To write back modified data to memory, the node must initiate a WRITEBACK bus transaction that contains the data and is accepted by mem-

ory. The atomic nature of the bus ensures that racing coherence requests are ordered with respect to the writeback operation.

Snooping coherence on a bus was first described by Goodman [50]. Early bus implementations used electrically shared wires that held the bus for an entire coherence transaction. Higherperforming buses used split transactions to allow other processors to acquire the bus while waiting for a response. More modern snooping systems implement a logical bus using additional switches, state, and logic rather than shared electrical wires. Furthermore, they can also implement the ordering of a bus only for coherence control messages. For example, the Sun Starfire [30] system implements a logical bus only for coherence request messages, but data responses travel on a different switched interconnect. Even higher-performing buses use pipelining techniques to achieve more concurrency. While these more aggressive buses may relax the atomicity property, they still provide a total order of coherence requests that enables a straightforward implementation of snooping like described in this section.

# 2.2.2 Greedy Snooping on a Ring

While buses offer a total order that enable simple coherence protocols, it is difficult to implement a bus that keeps pace with increasing core frequencies. Implementing a faster interconnect requires designers to use point-to-point links instead of electrically or logically shared wires. One option uses a ring topology where each node is connected to two other nodes such that they form a closed loop. All messages nominally travel through the ring in the same direction, and messages between nodes are never reordered.

FIGURE 2-2. Ring-based symmetric multiprocessor

A ring-based SMP is shown in Figure 2-2. A ring offers fast point-to-point links but avoids some of the complexity of general purpose, packet-switched interconnects in arbitrary topologies. Routers and switches on a ring can be fast and simple. The router at each node consists of a single input port and a single output port. Nodes have the opportunity to insert and remove messages from the ring using distributed arbitration [122].

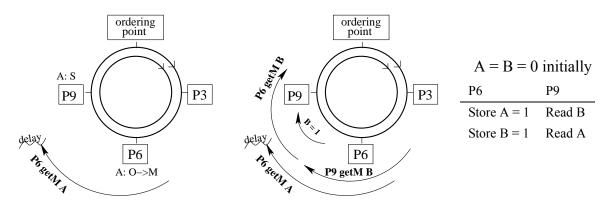

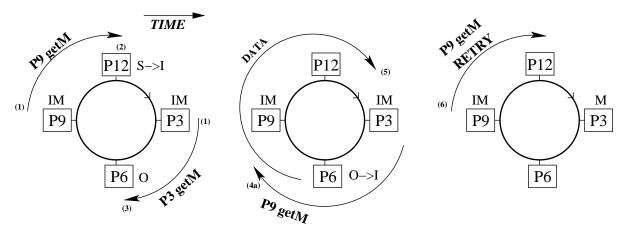

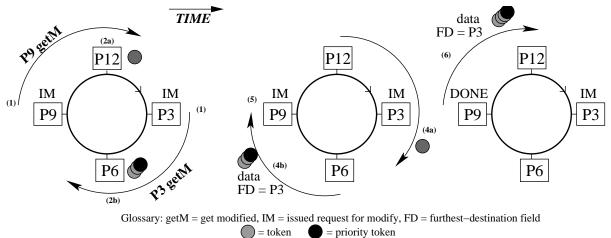

Unfortunately the order of a ring interconnect is not the same as the order provided by a bus because the order a node observes messages can depend on ring position. Furthermore a ring does not offer shared lines used by the bus-based snooping protocols described in the prior section. Therefore snooping coherence protocols for rings must adapt to the lack of total bus ordering and the lack of atomic shared lines.

Barroso et al. [17] examined snooping on a ring and proposed an approach that we generalize and call *greedy snooping*. The primary commercial systems using ring-based coherence, the IBM Power4/5, also uses a greedy-like snooping protocol for coherence on a ring [82]. What follows in this section is a high-level description of greedy snooping before it is examined in lower-level detail in Chapter 4. A greedy snooping protocol broadcasts coherence requests to all other nodes in the system. A GETS request seeks to find the owner of the cache line to obtain data, which is the cache in state O, E, or M. A GETM request additionally seeks to invalidate all other sharers. While a ring naturally accomplishes the broadcast operation, there is no total ordering or atomicity. Therefore unlike the bus protocol of the previous section, a requestor cannot be assured that its coherence request is ordered once the message is transmitted and racing (or conflicting) coherence requests must be handled differently.

First, all processors in a greedy protocol send the result of the snoop operation to the requestor to indicate when a request successfully completes. This *snoop response message* indicates if the processor cached the block, invalidated its cache on a GETM request, and if it was the owner and will respond with data. The snoop response itself does *not* contain data and instead indicates *acknowledgement* (ACK) of processing a coherence request. Fortunately a ring can reduce the cost of a snoop response from every processor by *combining* responses into a single message (or field) as a message traverses the ring.

Second, the lack of bus ordering means the greedy protocol must handle racing requests to ensure correct coherence. With no total ordering, racing coherence requests for the same block address *greedily* order based on which request reaches the owning processor first. The owning processor acknowledges the winning request and proceeds to handle it by sending data and/or transferring ownership. Other racing (or conflicting) requests for the same block address are forced to *retry* their request by re-issuing the request message on the interconnect. Processors retry their request when the snoop response messages indicate that the request message was not acknowledged by the owner. Because of this greedy order, some requestors may issue an

unbounded number of retries due to pathological behavior that may continually cause a request to lose the race to the owner. Therefore, a greedy protocol may exhibit liveness issues without additional mechanisms.

A greedy protocol on a ring also requires additional mechanisms to interface with memory. In a bus-based system, the memory controller responds to a GETS or GETM request if not inhibited by the shared owner line. Without shared lines, either memory must contain additional state to determine if it should source the data, or the requestor must explicitly request data from memory if it discovers there is no other cache that owns the block.

Like bus-based snooping protocols, replacement operations with a greedily-ordered snooping protocol are straightforward. Unmodified shared copies can silently replace whereas modified data is simply placed on the ring for writeback to memory. Races between a replacing node and a requesting node will result in the requestor issuing a retry.

Additional details of how a greedy protocol operates in a ring topology are deferred to Chapter 4, where we consider ring-based coherence in more detail.

## 2.2.3 Greedy Snooping on Arbitrary Topologies

Building faster and more scalable systems requires interconnects beyond buses and rings. Figure 2-3 shows the topology of a 4-processor system using point-to-point links in a 2x2 grid topology. Like rings, a 2x2 grid has no total ordering of messages and is considered unordered.

The greedy snooping protocol described in the last section, for ring-based interconnects, can also operate on completely unordered topology like shown in Figure 2-3. However we are not aware of any prior commercial system that does greedy snooping on an unordered interconnect.

### FIGURE 2-3. SMP with no interconnect ordering

Nonetheless, we describe this approach because of the increasing popularity of broadcast-based protocols on unordered interconnects.

To greedily snoop on an arbitrary topology, processors directly broadcast coherence messages to all other processors in the system. The messages seek to locate the owner of a cache block and to invalidate shared copies on a GETM request. As described in the prior section, if multiple processors simultaneously broadcast request messages for the same block address, the message that reaches the owning processor succeeds whereas other racing requests must retry. A processor issues a retry when it receives a snoop response from every processor in the system and none of the responses indicate the owning processor acknowledged the request. Instead of collecting combined snoop responses on a ring, every processor responds with an explicit snoop response message to indicate snoop completion and to indicate that the owner was found. To prevent incorrect coherence when GETS and GETM requests race, the owner status of a block is always transferred with the data response to any requestor.

Another approach to snooping coherence on an unordered interconnect is token coherence, to be discussed in Section 2.2.6. Moreover, emerging details [72] about Intel's upcoming CSI speci-

fication indicate that unordered broadcast coherence is also used along with a Forwarding (F) state that appears similar to greedy snooping's required owner (O) state. However they suggest conflict is explicitly detected and resolved by an ordering point instead of using retries. At this time and to our knowledge, no additional details are published about their protocol. The following section discusses a protocol that always uses an ordering point to avoid races and conflict.

### 2.2.4 Ordered Snooping on Arbitrary Topologies

It is often said that all problems in computer science can be solved with a level of indirection. We now describe a protocol, based on the AMD Opteron [7], that adds a level of indirection to achieve coherence ordering on an unordered interconnect without the use of retries. A processor first sends its coherence request message to an *ordering point* to establish the total order. In the Opteron system, the memory controller functions as the ordering point. The ordering point then broadcasts the request message to all other processors in the system. The ordering point also *blocks* on that address to prevent subsequent coherence requests for the same cache line to race with a request in progress.

To indicate completion of a read or write, the requestor must wait for an explicit acknowledgement (ACK) message from every other processor in the system after they complete their snoops. Once the requestor has received all acknowledgements and data, it unblocks the memory controller by sending a *completion* message. The memory controller can then initiate a broadcast for the next waiting request for that block. Since the memory controller fully buffers and orders requests, there are no inherent liveness or starvation issues with the protocol itself.

Once again, the lack of shared lines requires a mechanism to fetch data from DRAM when no other processor caches the block. One option is for memory to respond with data on any GETS and GETM request. However if a cache holds a dirty copy of the line, then it too responds to the requestor with the more recent data. Thus this approach results in two data responses on any sharing between processors. Another option is for the requesting processor to re-request the data from the memory controller once it receives a snoop response from every processor indicating no other sharers. The memory controller can reduce the latency overhead of this approach by prefetching the data from DRAM when it receives the initial GETS or GETM message. A third option, implemented by Martin et al.'s adaptation of this protocol [90], adds an owner-bit to memory to indicate that memory owns the block and should respond with data.

Unlike bus-based and greedy snooping protocols, replacing dirty data to memory requires additional messaging to ensure coherence. For example, consider a processor P1 replacing dirty data to memory. If a race occurs where P2 issues a request to the memory controller while the dirty data from P1 is in-flight to memory, P2 could receive stale data from memory instead of P1's most-recently modified data. To solve this race, one solution requires P1 to enter a transient state upon sending dirty data to memory. P1 also maintains a copy of data, while in the writeback transient state, to respond to subsequent requests until it receives an ACK message from the memory controller. We refer to this type of replacement operation as a *two-phase writeback*. Another type of writeback first requests permission with the memory controller to replace the block and then sends data after receiving an acknowledgement. This is known as a *three-phase writeback* [54].

The primary disadvantage of the Opteron-like protocol is its excessive use of bandwidth for broadcasts and snoop responses as the system size increases. The following section considers another approach that uses an ordering point but that uses additional state to reduce bandwidth.

FIGURE 2-4. Directory-based multiprocessor in a 2D torus interconnect

### **2.2.5 Directory Coherence**

This section presents an overview of directory-based coherence. Directory coherence offers increased scalability by reducing the amount of messages required for coherence requests [4]. Like the Opteron approach of Section 2.2.4, a level of indirection enables coherence on an unordered interconnect. Unlike the Opteron approach, directory protocols include additional state at the ordering point to reduce the bandwidth of broadcasts and system-wide snoop acknowledgement messages.

A directory contains state about the sharing status of a given block to determine the actions needed when a coherence request is received. A typical directory includes a list of sharers for each block, and a field that points to the current owner. A directory can also take other forms, such as a linked list of sharers [53], or sharing lists at a coarser granularity than single processor-cache nodes [52]. Directory-based cache coherence was first suggested by Tang [129] and Censier et al. [28]. Examples of commercial machines using directories include the SGI Origin [84] and the Alpha 21364 [104].

A directory system, like the Alpha 21364 [104], is shown in Figure 2-4. Each uniprocessor node contains a router to interface with the interconnect, as well as a directory controller that implements the coherence protocol for the portion of memory directly accessible by its memory controller. Thus every cache line address maps to an interleaved *home node* that contains the appropriate directory and memory controller for the line. The directory state for each line is usually stored in DRAM either in a reserved portion of DRAM, on separate chips, or by exploiting ECC re-encoding techniques [115, 48].

If a processor misses in its private cache hierarchy on a read request, it issues a GETS coherence request to the home node for the memory line. The directory controller at the home node accesses the directory state for the line in question. If the entry for the line indicates no sharers, the block is *idle*. In this case, the directory fetches data from DRAM, returns the data to the requestor, and updates the directory state to indicate that the requestor now owns the block. On the other hand, if the directory entry for the GETS request indicates another node owns the block, then the directory controller generates a *forward* message to the owning node and adds the requestor identification to the sharing list. The owning node responds with data directly to the requestor.

If a GETM request reaches the directory with a non-zero sharers list, then the directory controller generates *invalidation* (INV) messages to every sharing node. Upon invalidating its cache, the recipient of an invalidation message sends an acknowledgement (ACK) message to the requestor. The GETM requestor completes its write when it has received data and has received an acknowledgement message for every invalidated sharer. To maintain the coherence invariant in unordered interconnects, directories use transient or busy states while forward and invalidate messages reach their destined caches. Subsequent requests reaching a busy directory are either buffered [2] or negatively acknowledged (*NACKed*) [84]. Requests that are NACKed must be retried by the requestor. Such a NACKing protocol may use an unbounded number of retries for the request, which can lead to starvation under pathological situations. In Chapter 4, we observe a similar starvation scenario with a ring-based protocol that uses unbounded retries.

## 2.2.6 Token Coherence

The previous techniques to coherence, snooping and directory, both require the careful coordination of message exchanges and of state-machine transitions to ensure the coherence invariant. The properties of the interconnect also further complicate the design of the protocol to ensure the invariant. A technique proposed in 2003, *token coherence*, directly enforces the coherence invariant through a simple technique of counting and exchanging tokens.

Token coherence [93] associates a fixed number of tokens with each block. In order to write a block, a processor must acquire all the tokens. To read a block, only a single token is needed. In this way, the coherence invariant is directly enforced by counting and exchanging tokens. Cache tags and messages encode the number of tokens using  $Log_2N$  bits, where N is the fixed number of tokens for each block.

Token coherence allows processors to aggressively seek tokens without regard to order. A *performance policy* is used to acquire tokens in the common case. For example, a processor in a multiprocessor could predict which processor possesses the tokens and only send a message directly to it. However prediction can be incorrect and a processor's request may fail to acquire

the needed tokens. Thus while a performance policy seeks to maximize performance, token coherence also provides a *correctness substrate* to ensure coherence and liveness.