# REVISITING VIRTUAL MEMORY

By

#### Arkaprava Basu

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

(Computer Sciences)

at the

UNIVERSITY OF WISCONSIN-MADISON

2013

Date of final oral examination: 2<sup>nd</sup> December 2013.

The dissertation is approved by the following members of the Final Oral Committee:

Prof. Remzi H. Arpaci-Dusseau, Professor, Computer Sciences

Prof. Mark D. Hill (Advisor), Professor, Computer Sciences

Prof. Mikko H. Lipasti, Professor, Electrical and Computer Engineering

Prof. Michael M. Swift (Advisor), Associate Professor, Computer Sciences

Prof. David A. Wood, Professor, Computer Sciences

© Copyright by Arkaprava Basu 2013

All Rights Reserved

Dedicated to my parents Susmita and Paritosh Basu for their selfless and unconditional love and support.

## **Abstract**

Page-based virtual memory (paging) is a crucial piece of memory management in today's computing systems. However, I find that need, purpose and design constraints of virtual memory have changed dramatically since translation lookaside buffers (TLBs) were introduced to cache recently-used address translations: (a) physical memory sizes have grown more than a millionfold, (b) workloads are often sized to avoid swapping information to and from secondary storage, and (c) energy is now a first-order design constraint. Nevertheless, level-one TLBs have remained the same size and are still accessed on every memory reference. As a result, large workloads waste considerable execution time on TLB misses and all workloads spend energy on frequent TLB accesses.

In this thesis I argue that it is *now time to reevaluate virtual memory management*. I reexamine virtual memory subsystem considering the ever-growing latency overhead of address translation and considering energy dissipation, developing three results.

First, I proposed direct segments to reduce the latency overhead of address translation for emerging big-memory workloads. Many big-memory workloads allocate most of their memory early in execution and do not benefit from paging. Direct segments enable hardware-OS mechanisms to bypass paging for a part of a process's virtual address space, eliminating nearly 99% of TLB miss for many of these workloads.

Second, I proposed opportunistic virtual caching (OVC) to reduce the energy spent on translating addresses. Accessing TLBs on each memory reference burns significant energy, and virtual memory's page size constrains L1-cache designs to be highly associative -- burning yet

more energy. OVC makes hardware-OS modifications to expose energy-efficient virtual caching as a dynamic optimization. This saves 94-99% of TLB lookup energy and 23% of L1-cache lookup energy across several workloads.

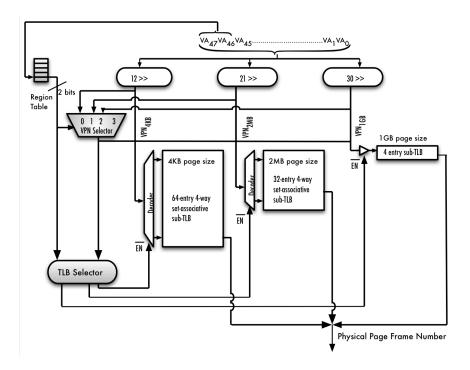

Third, large pages are likely to be more appropriate than direct segments to reduce TLB misses under frequent memory allocations/deallocations. Unfortunately, prevalent chip designs like Intel's, statically partition TLB resources among multiple page sizes, which can lead to performance pathologies for using large pages. I proposed the merged-associative TLB to avoid such pathologies and reduce TLB miss rate by up to 45% through dynamic aggregation of TLB resources across page sizes.

# **Acknowledgements**

It is unimaginable for me to come this far to write the acknowledgements for my PhD thesis without the guidance and the support of my wonderful advisors – Prof. Mark Hill and Prof. Mike Swift.

I am deeply indebted to Mark not only for his astute technical advice, but also for his sage life-advices. He taught me how to conduct research, how to communicate research ideas to others and how to ask relevant research questions. He has been a pillar of support for me during tough times that I had to endure in the course of my graduate studies. It would not have been possible for me to earn my PhD without Mark's patient support. Beyond academics, Mark has always been a caring guardian to me for past five years. I fondly remember how Mark took me to my first football game at the Camp Randall stadium a few weeks before my thesis defense so that I do not miss out an important part of the *Wisconsin Experience*. Thanks Mark for being my advisor!

I express my deep gratitude to Mike. I have immense admiration for his deep technical knowledge across the breadth of computer science. His patience, support and guidance have been instrumental in my learning. My interest in OS-hardware coordinated design is in many ways shaped by Mike's influence. I am indebted to Mike for his diligence in helping me shape research ideas and present them for wider audience. It is hard to imagine for me to do my PhD in virtual memory management without Mike's help. Thanks Mike for being my advisor!

I consider myself lucky to be able to interact with great faculty of this department. I always found my discussions with Prof. David Wood to be great learning experiences. I will

have fond memories of interactions with Prof. Remzi Arpaci-Dusseau, Prof. Shan Lu, Prof. Karu Sankaralingam, Prof. Guri Sohi.

I thank my student co-authors with whom I had opportunity to do research. I learnt a lot from my long and deep technical discussion with Jayaram Bobba, Derek Hower and Jayneel Gandhi. I have greatly benefited from bouncing ideas off them. In particular, I acknowledge Jayneel's help for a part of my thesis.

I would like to thank former and current and students of the department with whom I had many interactions, including Mathew Allen, Shoaib Altaf, Newsha Ardalani, Raghu Balasubramanian, Yasuko Eckert, Dan Gibson, Polina Dudnik, Venkataram Govindaraju, Gagan Gupta, Asim Kadav, Jai Menon, Lena Olson, Sankaralingam Panneerselvam, Jason Power, Somayeh Sardashti, Mohit Saxena, Rathijit Sen, Srinath Sridharan, Nilay Vaish, Venkatanathan Varadarajan, James Wang. They made my time at Wisconsin enjoyable.

I would like to extend special thanks to Haris Volos, with whom I shared an office for more than four years. We shared many ups and downs of the graduate student life. Haris helped me in taking my first steps in hacking Linux kernel during my PhD. I am also thankful to Haris for gifting his car to me when he graduated and left Madison!

I thank AMD Research for my internship that enabled me to learn great deal about research in the industrial setup. In particular, I want to thank Brad Beckmann and Steve Reinhardt for making the internship both an enjoyable and learning experience. I would like to thank Wisconsin Computer Architecture Affiliates for their feedbacks and suggestions on my research works. I want to extend special thanks to Jichuan Chang with whom I had opportunity to collaborate for a part of my thesis work. Jichuan has also been great mentor to me.

I want to thank my personal friends Rahul Chatterjee, Moitree Laskar, Uttam Manna, Tumpa MannaJana, Anamitra RayChoudhury, Subarna Tripathi for their support during my graduate studies.

This work was supported in part by the US National Science Foundation (CNS-0720565, CNS-0834473, CNS-0916725, CNS-1117280, CNS-1117280, CCF-1218323, and CNS-1302260), Sandia/DOE (#MSN 123960/DOE890426), and donations from AMD and Google.

And finally, I want to thank my dear parents Paritosh and Susmita Basu – I cannot imagine a life without their selfless love and support.

# **Table of Contents**

| Chapter 1 | Introduction                            |    |

|-----------|-----------------------------------------|----|

| Chapter 2 | Virtual Memory Basics                   | 12 |

| 2.1 Bet   | fore Memory Was Virtual                 | 12 |

| 2.2 Inc   | eption of Virtual Memory                | 13 |

| 2.3 Vir   | tual Memory Usage                       | 15 |

| 2.4 Vir   | tual Memory Internals                   | 16 |

| 2.4.1     | Paging                                  | 17 |

| 2.4.2     | Segmentation                            | 29 |

| 2.4.3     | Virtual Memory for other ISAs           | 32 |

| 2.5 In t  | his Thesis                              | 34 |

| Chapter 3 | Reducing Address Translation Latency    | 36 |

| 3.1 Inti  | roduction                               | 36 |

| 3.2 Big   | g Memory Workload Analysis              | 39 |

| 3.2.1     | Actual Use of Virtual Memory            | 41 |

| 3.2.2     | Cost of Virtual Memory                  | 45 |

| 3.2.3     | Application Execution Environment       | 48 |

| 3.3 Eff   | icient Virtual Memory Design            | 49 |

| 3.3.1     | Hardware Support: Direct Segment        | 50 |

| 3.3.2     | Software Support: Primary Region        | 53 |

| 3.4 Sof   | ftware Prototype Implementation         | 58 |

| 3.4.1     | Architecture-Independent Implementation | 58 |

| 3.4.2     | Architecture-Dependent Implementation   | 60 |

| 3.5 Eva   | aluation                                | 62 |

| 3.5.1     | Methodology                             | 62 |

| 3.5.2     | Results                                 | 66 |

| 3.6 Dis   | seussion                                | 69 |

| 3.7 Lin   | nitations                               | 75 |

| 3.8 Rel   | ated Work                               | 76 |

| Chapter 4 | Reducing Address Translation Energy     | 80 |

| 4.1 Inti  | roduction                               | 80 |

| 4.2 Mot   | ivation: Physical Caching Vs. Virtual Caching         | 84  |  |  |

|-----------|-------------------------------------------------------|-----|--|--|

| 4.2.1     | Physically Addressed Caches                           | 84  |  |  |

| 4.2.2     | 4.2.2 Virtually Addressed Caches                      |     |  |  |

| 4.3 Ana   | lysis: Opportunity for Virtual Caching                | 89  |  |  |

| 4.3.1     | Synonym Usage                                         | 89  |  |  |

| 4.3.2     | 4.3.2 Page Mapping and Protection Changes             |     |  |  |

| 4.4 Opp   | ortunistic Virtual Caching: Design and Implementation | 92  |  |  |

| 4.4.1     | OVC Hardware                                          | 93  |  |  |

| 4.4.2     | OVC Software                                          | 98  |  |  |

| 4.5 Eva   | uation                                                | 101 |  |  |

| 4.5.1     | Baseline Architecture                                 | 101 |  |  |

| 4.5.2     | Methodology and Workloads                             | 102 |  |  |

| 4.5.3     | Results                                               | 103 |  |  |

|           | C and Direct Segments: Putting it Together            |     |  |  |

| 4.7 Rela  | ted Work                                              | 109 |  |  |

| Chapter 5 | TLB Resource Aggregation                              | 113 |  |  |

| 5.1 Intro | oduction                                              | 113 |  |  |

| 5.2 Prob  | olem Description and Analysis                         | 121 |  |  |

| 5.2.1     | Recap: Large pages in x86-64                          | 121 |  |  |

| 5.2.2     | TLB designs for multiple page sizes                   | 122 |  |  |

| 5.2.3     | Problem Statement                                     | 127 |  |  |

| 5.3 Desi  | gn and Implementation                                 | 128 |  |  |

| 5.3.1     | Hardware: merged-associative TLB                      | 128 |  |  |

| 5.3.2     | Software                                              | 133 |  |  |

| 5.4 Dyn   | amic page size promotion and demotion                 | 136 |  |  |

| 5.5 Eval  | uation                                                | 138 |  |  |

| 5.5.1     | Baseline                                              | 138 |  |  |

| 5.5.2     | Workloads                                             | 138 |  |  |

| 5.5.3     | Methodology                                           | 139 |  |  |

|           | ılts                                                  |     |  |  |

|           | Enhancing TLB Reach                                   |     |  |  |

| 5.6.2     | TLB Performance Unpredictability with Large Pages     | 141 |  |  |

| 5.6.3     | Performance benefits of merged TLB                    | 142 |  |  |

| 5.7 Rela  | ted Work                                              | 144 |  |  |

| 5.8     | Conclusion                                     | 148 |

|---------|------------------------------------------------|-----|

| Chapte  | er 6 Summary, Future Work, and Lessons Learned | 149 |

| 6.1     | Summary                                        | 149 |

| 6.2     | Future Research Directions                     | 151 |

| 6       | 2.1 Virtual Machines and IOMMU                 | 152 |

| 6       | 2.2 Non-Volatile Memory                        | 153 |

| 6       | 2.3 Heterogeneous Computing                    | 154 |

| 6.3     | Lessons Learned.                               | 155 |

| Bibliog | graphy                                         | 159 |

| Appen   | dix: Raw Data Numbers                          | 163 |

1

# Introduction

"Virtual memory was invented at the time of scarcity. Is it still a good idea?"

--Charles Thacker, 2010 ACM Turing award lecture.

Page-based virtual memory (paging) is a crucial piece of memory management in today's computing systems. software accesses memory using a virtual address that must be translated to a physical address before the memory access can be completed. This virtual-to-physical address translation process goes through the page-based virtual memory subsystem in every current commercial general-purpose processor that I am aware of. Thus, efficient address translation mechanism is prerequisite for efficient memory access and thus ultimately for efficient computing. Notably though, virtual address translation mechanism's basic formulation remains largely unchanged since the late 1960s when translation lookaside buffers (TLB) were

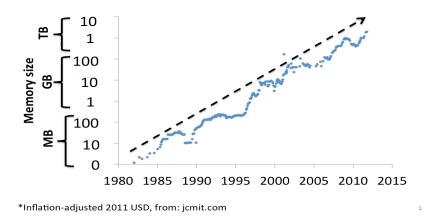

## Memory capacity for \$10,000\*

Figure 1-1. Growth of physical memory.

introduced to efficiently cache recently used address translations. However, the purpose, usage and the design constraints of virtual memory have witnessed a sea change in the last decade.

In this thesis I argue that it is *now time to reevaluate the virtual memory management*. There are at least two key motivations behind the need to revisit virtual memory management techniques. First, there has been *significant change in the needs and the purpose of virtual memory*. For example, the amount of memory that needs address translation is a few orders of magnitude larger than a decade ago. Second, there are new key constraints on how one designs computing systems today. For example today's systems are most often power limited, unlike those from a decade ago.

**Evolved Needs and Purposes:** The steady decline in the cost of physical memory enabled a million-times larger physical memory in today's systems then during the inception of the page-based virtual memory. Figure 1-1 shows the amount of physical memory (DRAM) that

could be purchased in 10,000 inflation-adjusted US dollar since 1980. One can observe that physical memory has become exponentially cheaper over the years. This has enabled installed physical memory in a system to grow from few megabytes to a few gigabytes and now even to a few terabytes. Indeed, HP's DL980 server currently ships with up to 4TB of physical memory and Windows Server 2012 supports 4TB memories, up from 64GB a decade ago. Not only can modern computer systems have terabytes of physical memory but the emerging big memory workloads also need to access terabytes of memory at low latency. In the enterprise space, the size of the largest data warehouse has been increasing at a cumulative annual growth rate of 173 percent — significantly faster than Moore's law [77]. Thus modern systems need to efficiently translate addresses for terabytes of memory. This ever-growing memory sizes stretches current address-translation mechanisms to new limits.

Unfortunately, unlike the exponential growth in the installed physical memory capacity, the size of the TLB has hardly scaled over the decades. The TLB plays a critical role to enable efficient address translation by caching recently used address translation entries. A miss in the TLB can take several memory accesses (e.g., up to 4 memory access in x86-64) and may incur 100s of cycles to service. Table 1-1 shows the number of L1-DTLB (level 1 data TLB) entries per core in different Intel processors over the years. The number of TLB entries has grown from 72 entries in Intel's Pentium III (1999) processors to 100 entries in Ivy Bridge processors (2012). L1-DTLB sizes are hard to scale since L1-TLBs are accessed on each memory reference and thus need to abide by strict latency and power budgets. While modern processors have added second level TLBs (L2-TLB) to reduce performance penalty on L1-TLB misses, recent research

Table 1-1. L1-Data-TLB sizes in Intel processors over the years.

| Year            | 1999          | 2001        | 2008      | 2012         |

|-----------------|---------------|-------------|-----------|--------------|

| L1-DTLB entries | 72            | 64          | 96        | 100          |

|                 | (Pentium III) | (Pentium 4) | (Nehalem) | (Ivy Bridge) |

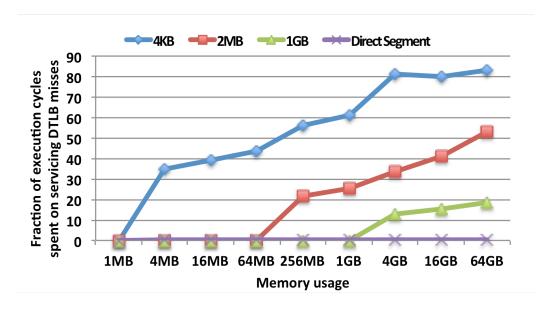

suggests that there is still considerable overhead due to misses in L1-TLB that hit in the L2-TLB [59]. Large pages that map larger amounts of memory with a single TLB entry can help reduce the number of TLB misses. However, efficient use of large pages remains challenging [69,87]. Furthermore, my experiments show that even with use of large pages, a double-digit percentage of execution cycles can still be wasted in address translation. Further, like any cache design, the TLB needs access locality to be effective. However, many emerging big data workloads like graph analytics or data streaming applications demonstrate low access locality and thus current TLB mechanisms may be less suitable for many future workloads [77].

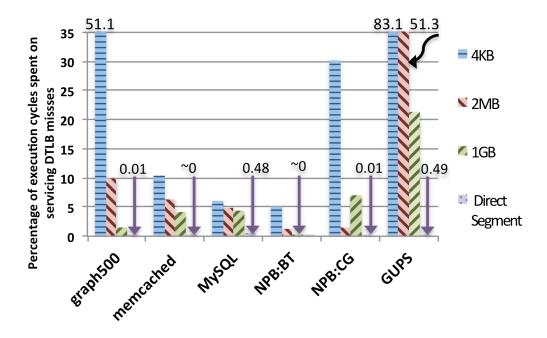

In summary, the every-increasing size of memory, growing data footprint of workloads, slow scaling of TLBs and low access locality of emerging workloads leads to an ever-increasing address translation overhead of page-based virtual memory. For example, my experiments on an Intel Sandy Bridge machine showed that up to 51% of the execution cycles could be wasted in address translation for the graph-analytics workloads *graph500* [36].

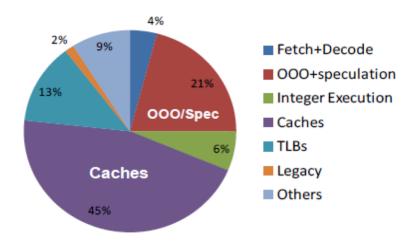

Figure 1-2. TLB power contribution to on-chip power budget. Data from Avinash Sodani's (Intel) MICRO 2011 Keynote talk.

**New Design Constraint:** Power dissipation is a first-class design constraint today. It was hardly the case when the virtual memory subsystems were first designed. The current focus on energy efficiency motivates reexamining processor design decisions from the previous performance-first era, including the crucial virtual memory subsystem.

Virtual memory's address translation mechanism, especially the TLB accesses, can contribute significantly to the power usage of a processor. Figure 1-2 shows the breakdown of power dissipation of a core (including caches) as reported by Intel [83]. TLBs can account up to 13% of the core's power budget. My own experiments find that 6.6-13% of on-chip cachehierarchy's dynamic energy is attributed to TLB accesses. Further, TLBs also show up as a hotspot due to high energy density [75]. The primary reason behind the substantial energy budget of TLB's is frequent accesses to TLB. Most, if not all, commercial general-purpose processors

today access caches using physical addresses. Thus every memory reference needs to complete a TLB access before the memory access is completed. Furthermore, since a TLB is on the critical path of every memory access, fast and thus often energy-hungry transistors are used to design TLBs.

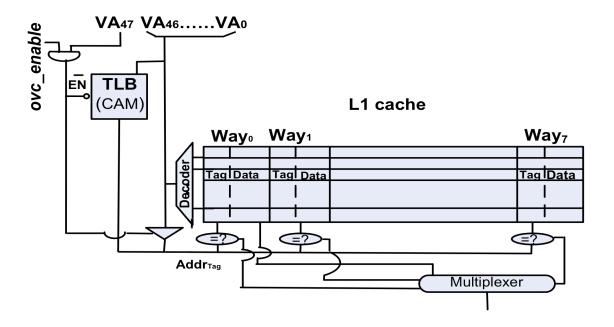

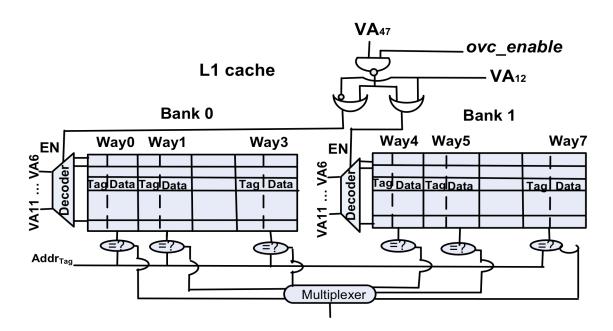

The energy dissipation is further exacerbated by the designs from performance-first era that hide TLB lookup latency from the critical path of the memory accesses. They do so by accessing the TLB in parallel to indexing into a set-associative L1 cache with page offset of the virtual address. The TLB output is used only during the tag comparison at the L1 cache. However, such a virtually indexed physically tagged cache design requires that the page offset be part of L1 cache indexing bits – forcing the L1 cache to be more highly associative than required for low cache miss rates. For example, a typical 32KB L1 cache needs to be at least 8-way set-associative to satisfy this constrain with 4KB pages. Each access to a higher-associativity structure burns more energy and thus ultimately adds to the power consumption.

In summary, many aspects of current virtual memory's address translation mechanisms warrant a fresh cost-benefit analysis considering energy dissipation as a first-class design constraint.

**Proposals:** In this thesis I aim to reduce the latency and the energy overheads virtual memory's address translation primarily through three pieces of work. First, I propose *direct segments* [8] to reduce TLB miss overheads for big memory workloads. Second, I propose *opportunistic virtual caching* [9] to reduce address translation energy. Finally, I also propose a *merged-associative TLB*, which aims to improve TLB designs for large page sizes by eliminating

performance unpredictability with use of large pages in commercially prevalent TLB designs. In the following, I briefly describe these three works.

1. Direct Segments (Chapter 3): I find that emerging big-memory workloads like in-memory object-caches, graph analytics, databases and some HPC workloads incur high address-translation overheads in conventional page-based virtual memory (paging) and this overhead primarily stems from TLB misses. For example, on a test machine with 96GB physical memory, graph500 [36] spends 51% of execution cycles servicing TLB misses with 4KB pages and 10% of execution cycles with 2 MB large pages. Future big-memory-workload trends like evergrowing memory footprint and low access locality are likely to worsen this further.

My memory-usage analysis of a few representative big memory workloads revealed that despite the cost of address translation, many key features of paging, such as swapping, fine-grain page protection, and external-fragmentation minimization, are not necessary for *most of their memory usage*. For example, databases carefully size their buffer pool according to the installed physical memory and thus rarely swap it. I find that only a small fraction of memory allocations, like those for memory-mapped files and executable code, benefit from page-based virtual memory. Unfortunately, current systems enforce page-based virtual memory for all memory, irrespective of its usage, and incur page-based address translation cost for all memory accesses.

To address this mismatch between the big-memory workloads' needs, what the systems support, and the high cost of address translation, I propose that processors support two types of address translation for non-overlapping regions of a process's virtual address space: 1) conventional paging using of TLB, page table walker etc., 2) a new fast translation mechanism

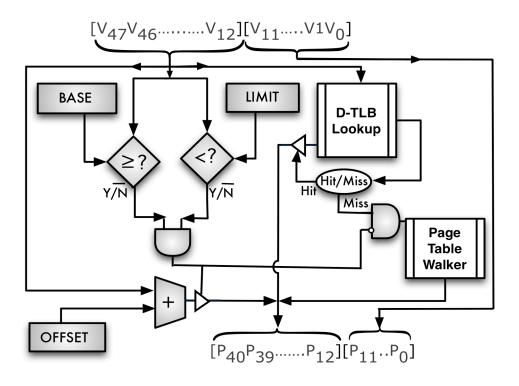

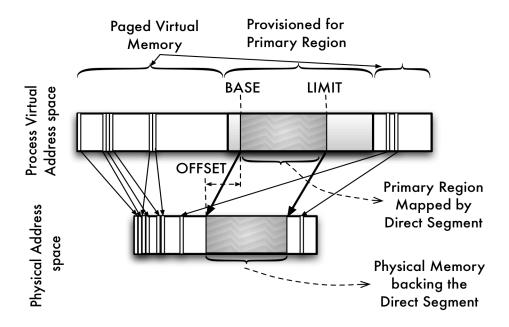

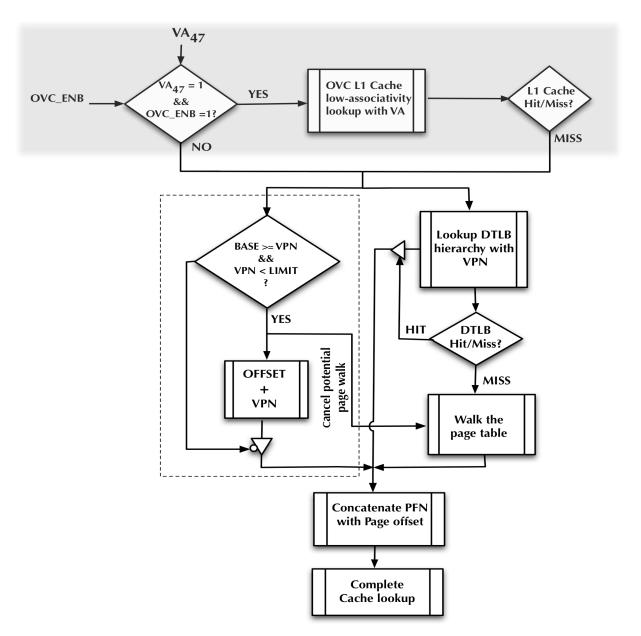

that uses a simple form of segmentation (without paging) called a *direct segment*. Direct segment hardware can map an arbitrarily large contiguous range of virtual addresses having uniform access permissions to a contiguous physical address range with a small, fixed hardware: *base*, *limit* and *offset* registers for each core (or context). If a virtual address is between the base and limit register values then the corresponding physical address is *calculated* by adding the value of the offset register to the virtual address. Since addresses translated using a direct segment need no TLB lookup; no TLB miss is possible. Virtual addresses outside the direct segment's range are mapped using conventional paging through TLBs and are useful for memory allocations that benefit from page-based virtual memory. The OS then provides a software abstraction for direct segment to the applications – called a *primary region*. The primary region captures memory usage that may not benefit from paging in a contiguous virtual address range, and thus could be mapped using direct segment.

My results show that direct segments can often eliminate 99% of TLB misses across most of the big memory workloads to reduce time wasted on TLB misses to 0.5% of execution cycles.

**2. Opportunistic Virtual Caching (Chapter 4):** I proposed Opportunistic Virtual Caching (OVC) to reduce energy dissipated due to address translation. I find that looking up TLBs on each memory access can account for 7-13% of the dynamic energy dissipation of whole on-chip memory hierarchy. Further, the L1 cache energy dissipation is exacerbated by designs that hides TLB lookup latency from the critical path.

OVC addresses this energy wastage by enabling energy-efficient virtual caching as *a dynamic optimization under software control*. The OVC hardware allows some of the memory

blocks be cached in the L1 cache with virtual addresses (virtual caching) to avoid energy-hungry TLB lookups on L1 cache hits and to lower the associativity of L1 cache lookup. The rest of the blocks can be cached using conventional physical addressing, if needed.

The OS, with optional hints from applications, determines which memory regions are conducive to virtual caching and uses virtual caching or conventional physical caching hardware accordingly. My analysis shows that many of challenges to efficient virtual caching, like inconsistencies due to read-write synonyms (different virtual addresses mapping to same physical address), occur rarely in practice. Thus, the vast majority of memory allocation can make use of energy-efficient virtual caching, while falling back to physical caching for the rest, as needed.

My evaluation shows that OVC can eliminate 94-99% of TLB lookup energy and 23% of L1 cache dynamic lookup energy.

**3. Merged-Associative TLB (Chapter 5):** While the proposed direct segments can eliminate most of DTLB misses for big memory workloads that often have fairly predictable memory usage and allocate most memory early in execution, it may be less suitable when there are frequent memory allocation/deallocations. In contrast, support for large pages is currently the most widely employed mechanism to reduce TLB misses and could be more flexible under frequent memory allocation/deallocation by enabling better mitigation of memory fragmentation.

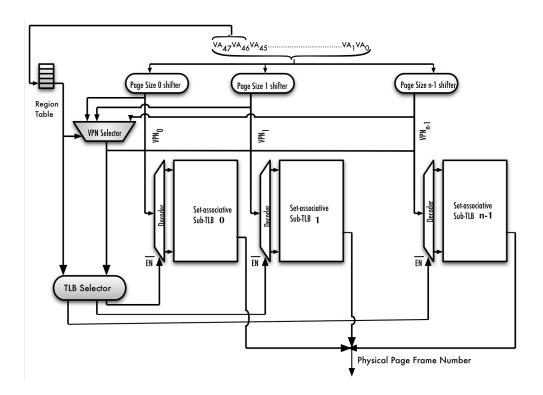

In the third piece of work I try to improve large-page support in commercially prevalent chip designs like those from Intel (e.g., Ivy Bridge, Sandy Bridge) that support multiple page sizes by providing separate sub-TLBs for each distinct page sizes (called a split-TLB design). Such a static allocation of TLB resources based on page sizes can lead to performance pathologies where use of larger pages can increase TLB miss rates and disallow TLB resource aggregation. A few competing commercial designs, like AMD's, instead employ a single fully associative TLB, which can hold entries for any page size. However, fully associative designs are often slower and more power-hungry than a set-associative one. Thus, a single set-associative TLB that can hold translations for any page size is desirable. Unfortunately, such a design is challenging as the correct index into a set-associative TLB for a given virtual address depends upon the page size of translation, which is unknown till the TLB lookup itself completes.

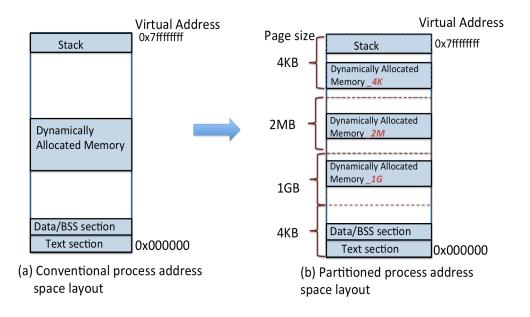

I proposed a *merged-associative TLB* to address this challenge by partitioning the abundant virtual address space of a 64-bit system among the page sizes instead of partitioning scarce hardware TLB resources. The OS divides a process's virtual address space into a fixed number of non-overlapping regions. Each of these regions contains memory mapped using a single page size. This allows the hardware to decipher page size by examining a few high-order bits of the virtual address even before the TLB lookup. In turn, this enables the hardware to *logically aggregate* the TLB resources for different page sizes into a larger set-associative TLB that can hold address translations for any page size. A merged-associative TLB can effectively achieve miss rates close to a fully associative TLB without actually having one and avoid performance pathologies of split-TLB design.

My experiments show that the merged-associative TLB successfully eliminates performance unpredictability possible with use of large pages in a conventional split-TLB

design. Furthermore, the merged-associative TLB could reduce the TLB miss rate by up to 45% in one of the applications studied.

**Organization of the thesis:** The organization of the rest of the thesis is as follows.

Chapter 2 describes the background of the virtual memory address translation mechanisms.

Chapter 3 describes the direct segments work that was published in 40<sup>th</sup> International Symposium on Computer Architecture (ISCA 2013). The content of the chapter mostly follows from the published paper but adds discussion on how direct segment could work in presence of physical page frames with permanent faults.

Chapter 4 describes the opportunistic virtual caching (OVC) work that was published in 39<sup>th</sup> International Symposium on Computer Architecture (ISCA 2012). The chapter follows the published paper for most part but adds a section on how OVC and direct segments could work together in a system.

Chapter 5 describes merged-associative TLB work, which is not yet published.

Chapter 6 concludes the thesis and describes potential future extensions to the thesis.

2

# **Virtual Memory Basics**

In this chapter, I briefly discuss the history of evolution of virtual memory and basic mechanisms for virtual memory. While I primarily focus on the virtual memory as provided in x86-64 instruction set architecture (ISA), I also discuss virtual memory in contemporary ISAs like ARM, PowerPC, SPARC.

## 2.1 Before Memory Was Virtual

From the early days of electronic computing the designers recognized that fast access to large amount of storage is hard and thus computer memories must be organized hierarchically [26]. Computer memories have been commonly organized in at least two levels – "main memory" and "auxiliary memory" or storage. A program's information (code, data etc.) could be referenced only when it resides in main memory. The obvious challenge is to determine, at each moment, which information should reside in main memory and which in auxiliary memory. This problem has been widely known as *storage allocation problem*. Until late 1950s, any

program that needed to access more information than could fit in the main memory, required to contain the logic for addressing the storage allocation problem [95]. Further, to allow multiprogramming and multitasking early systems divided physical memory with special set of registers as in DEC's PDP-10 [95]. The challenges for automatic storage allocation and multiprogramming not only complicated the task of writing large programs but also made effectively sharing the main memory, a key computing resource, difficult.

## 2.2 Inception of Virtual Memory

As programs got more complex and more people started programming, the need to provide an *automatic management* of memory was deemed necessary to relieve programmer's burden. In 1959, researchers from University of Manchester, UK, proposed and produced first working prototype of a virtual memory system as part of Atlas system [50]. They introduced the key concept behind virtual memory – distinction between the "address" and the "memory location". The "address" would later more widely

Figure 2-1. Abstract view of Virtual Memory

be known as virtual address, while "memory location" can be a physical or real address in the main memory or it could be a storage location as depicted in Figure 2-1. This allowed programmers to name information only by its virtual address while the system software (OS) along with the hardware is tasked to dynamically translate virtual addresses to its location in main memory or

storage. The OS enabled automatic movement of data between the memory and storage as needed.

They key concepts and mechanisms of virtual memory were then greatly refined by the Multics project [24]. They enabled two-dimensional virtual address space that allowed ease of sharing, modularity, and protection, while efficiently managing physical memory by allocating memory in fixed sizes (called *pages*). Such a two-dimensional address space required two identifiers to uniquely identify a memory location. The working set model [25] on access locality of programs was then invented by Denning to fill in critical component in virtual memory – how to decide how much of memory to assign to a process and how to decide which information to keep in the main memory and which information in the auxiliary memory.

The rest of this chapter is organized as follows. I will first discuss a few of the important use-cases of virtual memory. I will then delve into intricacies of implementation of virtual memory management. This discussion will revolve around how virtual memory is implemented in x86-64 processors. Since these mechanisms vary considerably across different instruction-set-architectures (ISAs) I will briefly compare and contrast virtual memory management of other relevant ISAs like PowerPC, ARM-64 and UltraSPARC (T2) with that of x86-64's. Finally, I will briefly discuss what aspects of the virtual memory management this thesis addresses.

## 2.3 Virtual Memory Usage

While virtual memory was initially conceived to lessen the burden of the programmer to write their own storage allocation procedures, it has since enabled many use-cases. A few of them are listed below.

- Automatic storage allocation: Virtual memory makes it possible to run a program with memory needs in excess of the installed main memory size. This relieves the programmer from being aware of memory sizes of the system where it will execute. Modern OSes achieve this by moving data in and out between the main memory (e.g., DRAM) and the auxiliary memory (e.g., disk) to provide an illusion of larger memory than one actually available. This mechanism is commonly referred to as *swapping*.

- *Protection:* Virtual memory enables efficient fine-grain (e.g., 4KB granularity) protection of memory. The virtual-memory hardware can enforce access restriction to parts of memory by processes. This is useful for avoiding unwanted overwrite of read-only information (e.g., code). It also enables many widely used optimization like copy-on-write whereby a memory location(s) can be shared among multiple processes until at least one of the processes tries to write memory location. Modern systems, like x86-64, also enable "no-execute" protection to disallow execution of certain memory allocation to enhance security against malicious code snippets.

- *Demand paging*: Virtual memory allows bringing in information (data, code, etc.) from auxiliary memory (storage) to main memory only when they are first referenced. Demand

paging enables fast startup for processes by not requiring pre-loading of all the information that the process would require during its execution.

- *Relocation:* Virtual memory enables ease in software development by allowing the same virtual address in different programs to refer to different physical memory location during execution. This allows the software tool chains (e.g., compiler, linker) generate code using only virtual addresses without worrying about where the referred information is located and thus, be agnostic of a system's memory configuration. This in turn, enables programs to be built from separately compiled, reusable and sharable modules.

- *Metadata collection:* Most current virtual memory hardware enables efficiently storing small amount of metadata with virtual memory allocation units (e.g., per-page dirty and reference bits). This enables usage information collection. For example, these hardware-managed metadata are often useful for many OS procedures like page-frame-reclamation or even in garbage collection of many high level languages.

- *Sharing:* Virtual memory enables efficient sharing of code and data among multiple processes by mapping virtual addresses of generated by different processes to map on to same physical memory location. This is especially useful in sharing libraries across multiple processes.

# 2.4 Virtual Memory Internals

In this section, I discuss the mechanisms to translate software-generated virtual addresses to physical addresses – a key component of virtual memory subsystem.

The OS and the hardware coordinate to accomplish this address-translation process. There are broadly two techniques of address translation that were ever employed – paging and segmentation. Paging or page-based virtual memory translates a linear virtual address to a physical address. The address translation process is essentially hidden from user programs except from its performance implications. Page-based virtual memory translates the virtual addresses in one or few ISA-defined granularities (e.g., 4KB). On the other hand, segmentation allows mapping between the address spaces at variable (often arbitrary) granularity. Segmentation often exposes two a dimensional virtual address space to users where an address is identified by a segment identifier and an offset within the segment. One advantage of paging over segmentation is that paging can help mitigate external fragmentation. External fragmentation can occur if memory is allocated and de-allocated in various sizes leaving physical memory scattered in small holes that is unusable to satisfy later memory requests. Paging mitigates this by allocating and de-allocating memory in one or a few fixed sizes called page size. Segmentation on the other hand allows ease of sharing semantically related memory locations (segments) among multiple processes. In this section, I will primarily focus on paging since it is the primary address translation mechanism supported across almost all modern architectures. Further, current systems that allow segmentation, do so on top of paging.

#### 2.4.1 Paging

While almost every commercial ISAs today implements paging, in this subsection I will discuss intricacies paging as implemented in x86-64 ISA. The hardware mechanism that is

responsible for translating software generated virtual addresses to physical address is called memory management unit or MMU. Below, I discuss various aspects of MMU.

#### 2.4.1.1 Address Spaces

While x86-64 can theoretically support up to 64-bit long linear virtual address all current implementations support up to 48 bits [40]. The address bits between 63<sup>th</sup> and 48<sup>th</sup> are sign extended. Thus current generation of x86-64 processors can refer up to 256TB of virtual addresses. Most commercial operating systems, such as Linux, Windows, export separate virtual address spaces for each process. Linux, for example, allows 128TB of virtual address space for each user process while allows another 128TB for the kernel.

The size of the physical address space determines the maximum size of the main memory that can be installed in a given system. Currently, x86-64 ISA supports up to 52 bits of physical address but unlike virtual address, the physical address size is a micro-architectural (rather than architectural) property and varies across processor models. A more typical 40-46 bit physical addresses can support up to 64TB installed physical memory capacity. Note that there is only one physical address space for a system, while each process in a system can have its own virtual address space.

## 2.4.1.2 Translating Virtual Addresses

The primary function of the virtual memory subsystem is to translate an address in a virtual address space to an address in the physical address space. In the following subsection, I will describe the key components and mechanism of this address translation process.

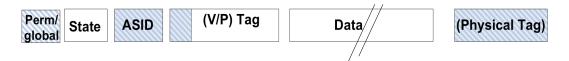

Page table: The page table is the per-process in-memory data-structure that holds the translation information from a linear virtual address space to physical address space. The page table stores the translation information at the granularity of ISA-defined page sizes. The default page size in x86-64 is 4KB, while a couple of larger page sizes are supported (discussed later in the section). The virtual address is divided in to two parts – virtual page number (VPN) and page offset. The page offset identifies the byte address within a page. For example, with 4KB page size the lower 12 bits of the virtual address. The rest of higher address bits constitute the virtual page number. The physical memory is similarly divided into physical page frames at the page-size grain and is identified by page frame number. The page offset remains unaltered between a virtual address and its corresponding physical address. Thus the page table translates a virtual page number to a page frame number. An entry of page table or page table entry (PTE) contain information such as whether the page is in memory, corresponding page frame number or location on the auxiliary memory (valid/present bit), access rights to the page (read, read-write etc.), whether the page belongs to supervisor mode (OS), reference and dirty bit. The size of each PTE in x86-64 is 8 bytes. In x86-64, the page table structure itself is accessed using physical address only.

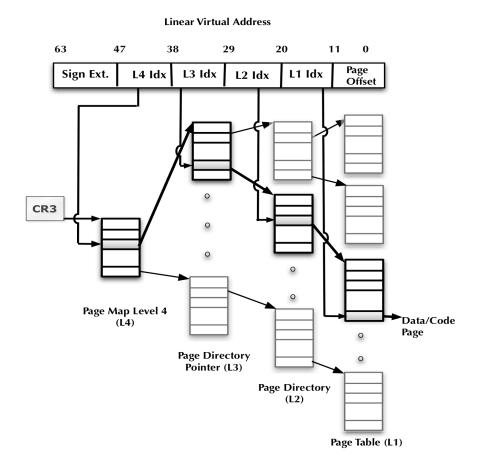

The x86-64 ISA defines the page-table data structure as a four-level radix tree with fan out of 512 at each level. Such a hierarchical page table structure allows space-efficient representation of large potentially sparse virtual address space. The last level of the page table contains PTE that contains the physical frame number.

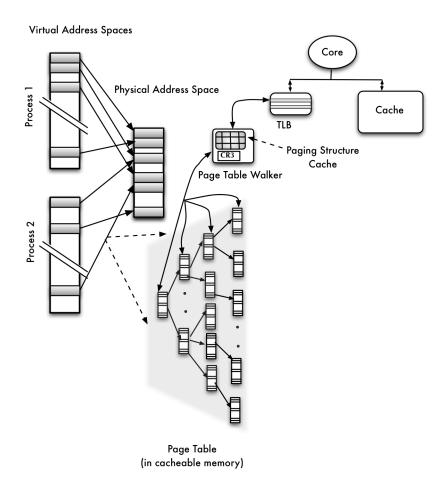

Figure 2-2. Page table walk in x86-64 with 4KB page size.

**Page Table Walk:** In Figure 2-2, I depict the structure of four-level page table for a process in x86-64. The figure also depicts how the page table is searched to find the desired PTE corresponding to a given linear virtual address. This process is called a page table walk. The size of each node in the tree structure is 4KB and the size of each entry in the node is 8-bytes wide. Thus, at each node of the page table there can be up to 512 entries (i.e., fan out of 512). I number the address bits such that the most significant bit is the 63<sup>th</sup> bit of the virtual address and 0<sup>th</sup> bit is the lowest significant bit.

In x86-64, a hardware page-table-walker walks the in-memory page table. First, the pagetable-walker needs to know the location of root of the page-table in the memory. In x86-64, a register named CR3 holds the physical page frame number (40 bits) of the root of the page table data structure of the currently running process [40]. The OS updates the value of CR3 when switching process contexts, as the location of the page table is part of a process's context. The least significant 12 bits of the virtual address constituting the page offset for 4KB pages remain unaltered across the virtual and physical address. The remaining higher-order 36-bits are divided in to four 9-bit indices used to select entries from four levels of the page table as shown in Figure 2-2. The four levels of page tables are named Page Map Level 4 (PML4 or L4), Page Directory Pointer (PDP or L3), Page Directory (PD or L2) and Page Table (PT or L1). In the first step, the value of CR3 register is used to locate the 4KB-aligned starting physical address of the PML4 of the page table. As depicted in the Figure 2-2, 9 bits from bit position 39<sup>th</sup> to 47<sup>th</sup> are extracted from the virtual address and appended to the value of CR3 (40 bits of physical address). This yields 49-bit physical address of the appropriate L4 entry. The L4 entry could contain the physical frame number of the page containing the corresponding L3 node. The process is repeated by extracting the L3 index field from virtual address and appending it to the physical page frame number obtained from the L4 node to locate the correct L3 entry. This recursive process continues until either a selected entry is invalid or the desired PTE at the L1 node is found. The PTE at L1 contains the desired physical page frame number corresponding to the given virtual page number. The page offset can then be appended to form the full physical address of the given virtual address. Such a page-table "walk" procedure can require up to four memory references to find the physical page frame number for a given virtual page number. As

the address space grows, more levels would need to be added, further increasing the number of memory references for a page table walk. A full 64-bit virtual address space could require up to six levels. However, often off-chip memory accesses are avoided as the page table entries could be cached along with normal data blocks in on-chip processor caches (e.g., L1, L2 and/or L3 caches).

Page fault: The page table can be sparsely populated. At any level if there are no valid entry corresponding to the given virtual address index, the sub-tree beneath that index is not instantiated. This yields significant memory space savings for a sparsely allocated virtual address space. An exception is raised to the OS if a valid entry is not found at any of the levels of the page table during the walk. Such a hardware exception is called a *page-fault*. The x86-64 hardware provides the linear virtual address that caused the page fault, called the faulting address, in the control register called CR2. The operating system then takes appropriate actions and may install mapping for the faulting address. OS can also raise exceptions to application if it deems necessary, e.g., a segmentation fault is raised if an unmapped address is accessed. Page-faults could also be triggered access rights violation (e.g., a write access to a read-only address) or if the desired page has been swapped out to the auxiliary memory (disk). While generating page-fault exception the hardware also provides related information such as whether the faulting address is instruction or data, whether the fault is due to access rights violation or due to invalid mapping information.

### 2.4.1.3 Making Address Translation Faster

TLB: Software accesses memory using virtual addresses that need to be translated to physical addresses. However, the aforementioned address translation process is too slow to be carried out on each memory access. To speed up this process, translation lookaside buffer or TLB was introduced. A TLB is a hardware cache of recently used address translation entries to avoid long-latency page-walk on every memory access. Each TLB entry contains a virtual page number and its corresponding physical page frame number. A TLB entry also contains related metadata information like access rights, super-user bits etc. On each memory access the TLB is accessed with the virtual page number. If it hits in the TLB then the physical page frame number is immediately available. No page-table-walk is necessary. However, in case of a TLB miss the hardware page-table walker looks up the page-table which could take up to four memory accesses as described in the previous sub-section.

Large Pages: The TLB structure needs to be fast and energy efficient as it is looked up on every memory access. This makes it hard to increase the number of TLB entries. To translate larger amount of memory without requiring more TLB entries, hardware designers introduced larger page sizes that helps increasing *TLB reach* (number of TLB entries × page size). Larger TLB reach can potentially lower the number of TLB misses. Currently, x86-64 supports two larger page sizes – 2MB and 1GB beyond the default 4KB page size. A single TLB entry for larger page sizes can translate 2MB or 1GB of contiguous virtual address to the corresponding amount of physical address. Thus, compared to the base page size, larger page sizes can increase the TLB reach with same number of TLB entries. Furthermore, larger page sizes shorten the

page walk procedure described in Figure 2-2. For example, an entry in the L2 node (page directory) could directly point to physical frame number of a 2MB page. Thus an address mapped using 2MB pages needs up to 3 memory references to find the corresponding physical page frame number. Similarly, page walk could stop at a L3 node (page directory pointer) for a 1GB page, requiring only up to two memory accesses. In summary, large pages can potentially lower the number of TLB misses as well as reduce the number of memory references needed for a page walk.

I observe that each page size in x86-64 is 512 times of its nearest size. This is an artifact of the x86-64's page table organization as radix tree with fan-out of 512. Radix-tree nodes at each level of the tree represent different a page size – L1 nodes represent 4KB pages, L2 nodes represents 2MB pages and L3 nodes represent 1GB pages. Going by this trend, it can be assumed that in future next larger page size could be 512GB.

A typical per-core TLB hierarchy with multiple page sizes in recent Intel's recent Ivy Bridge processors has two levels of TLBs. There are separate L1 TLBs for instruction and data. The L1 instruction TLB holds 128 entries for 4KB pages in an 8-way set-associative structure, while there are 8 entries for 2MB pages. The L1-data TLB has three sub-TLBs – 64 entry 4-way set-associative TLB for 4KB pages, 32 entry 4-way set-associative TLB for 2MB pages and 4-entry fully associative TLB for 1GB pages. The second level (L2) TLB can hold translations for both instruction and data. The L2-TLB can hold 512 4KB page translation and is a 4-way set-associative structure. There is no L2-TLB for larger page sizes. A miss in L1-TLB that hits in L2-TLB can incur a delay of 7 processor cycles [39].

Paging structure caches (PSC): A TLB miss triggers a long-latency hardware page table walk. To reduce this cost, the hardware designers have introduced a cache for holding only page table information, called a page-structure cache (Intel terminology). The key observation is that the accesses to upper levels of page table demonstrate significant temporal locality. For example, page table walks to two consecutive virtual address pages will likely to have same three upper level entries since indices selecting these entries are extracted from higher order bits of virtual address that rarely change. If the higher-level page table entries could be cached then the later page walks could be serviced faster, requiring less number of memory accesses. Thus the x86-64 vendors have developed caches to store recently used upper level page table entries [3,6,41]. However, their designs differ significantly. In this subsection, I primarily discuss Intel's designs of translation caches and briefly contrast it with AMD's design.

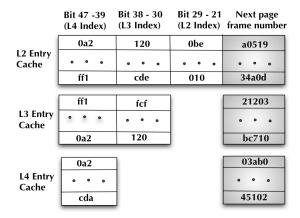

Like TLBs, PSCs are accessed using virtual addresses. However, while the TLBs are indexed and/or tagged by complete virtual page number, the PSCs are looked up using only a partial prefix of the virtual page number. More specifically, virtual address prefixes for different levels of the page table is used for accessing PSCs. For example, there can be a PSC entry for the L4 index (bits 39 to 47) of a virtual address (refer to Figure 2-3). Such an entry would provide the physical page frame number containing the corresponding node in the next level of the page table (here L3 node). Similarly, a PSC entry for bits 30 to 47 (L4 index appended by L3 index) of a virtual address would contain physical frame number containing the corresponding L2 node of the page table. An entry for bits 21 to 47 (L4 index appended by L3 index appended by L2 index) would contain physical frame number of desired PTE. I observe that for a given virtual

Figure 2-3. Paging-structure caches. The virtual address prefixes are un-shaded. The physical page frame number of next level in the page table is in shade.

page number there could be up to three prefixes that could match in the translation cache. Intel's page-structure caches employ a split design where different levels of page table entries corresponding to three different prefix lengths of the virtual address are cached in separate caches to avoid interference. Such a split design could be helpful since different level of page table entries demonstrate very different access locality. Figure 2-3 shows a typical page-structure cache configuration as found in Intel's recent processors. The number in the un-shaded boxes are prefixes of virtual addresses while the numbers in shaded represents physical frame number. The physical frame number represents the address of the page containing the desired PTE for a L2 entry, while it is the page frame number for node containing desired L2 node and L3 node for L3 and L4 entry, respectively.

On a TLB miss, the hardware page table walker firsts looks up the translation cache with the virtual page number of the missing address. The lookup can produce up to three hits, one each for three sub caches of three levels of the page table. The page table walker then selects an entry with longest prefix match. A hit in the sub-cache for L2 page table entries can reduce the number memory access on TLB miss to one, instead of four as originally required. Hits for L3 and L4 entry would require two and three memory references, respectively.

Different from Intel's design, AMD's chips implement a simpler design called page-walk cache for caching higher-level page table information. The entries are cached in the page-walk cache with their physical addresses, unlike partial prefix of virtual address for Intel's page-structure caches. AMD's page-walk cache can be deemed simply as a specialized data cache that can hold only page table entries. In the ideal case, all three upper level page table entries could be cached and three sequential lookups of the page walk cache can provide with the physical page frame number of the node containing the desired PTE. Thereafter a single memory reference provides the desired address translation. Further, unlike Intel's split design, AMD's page walk caches employ a unified design where all entries from all three upper levels of page-table compete for a place in the cache.

#### 2.4.1.4 Putting it altogether

In this section, I discuss how various components of x86-64's page based virtual management work together to translate a linear virtual address generated by the software to a physical address.

Figure 2-4 depicts various components of x86-64's virtual memory management and their interactions. The paged virtual memory management component in x86-64 is responsible for translating a software-generated 48-bit wide virtual address (VA) to 52-bit wide physical address (PA). In the following I describe the steps in that address translation process as it is done in most Intel's current processors.

Figure 2-4. Schematic diagram of key components of virtual memory management. (Not to scale)

**TLB:** The virtual page number is first searched in the TLB hierarchy. A hit in the TLB yields the desired physical page frame number along with the access rights. If the access rights are sufficient for a given access then the page offset is appended to the physical page frame number to obtain the desired physical address.

**Paging-structure Cache (PSC):** On a miss in TLB hierarchy, the PSC accompanying the hardware page table walker is looked up using prefixes of the virtual page number. As described in Section 2.4.1.3, page-structure caches can help skipping one or more levels of the

four levels of hierarchical page table. On a hit in the paging structure cache it could require one to three memory references for the partial page walk to find the desired PTE.

**Page walk:** On a miss in the PSC a complete page walk of in-memory page table data-structure is initiated. The CR3 register provides the physical address of the root of the page table for the given process. The hardware page-table-walker then walks the four-level radix tree structure of the page table that could take up to four off-chip memory accesses. The page table entries reside in normal cacheable memory and thus hardware page walker first accesses the on-chip cache hierarchy before accessing main memory.

**Page fault:** If the hardware page-table-walker finds no valid entry in the page table corresponding to the given virtual address or if entry lacks sufficient access rights, it raises page-fault exception to the OS. On a page-fault the OS can create the missing PTE or raise exception to user program.

#### 2.4.2 Segmentation

While previous section discussed the intricacies of address translation with paging, in this section I discuss segmentation.

Segmentation exports the virtual address space as a set of variable-sized sections or segments. Different segments usually represent distinct natural divisions of program like stack region, code region, data region, etc., and thus visible to the programmer or application. Segmentation usually exports a two-dimensional address space as opposed to linear address space provided by paging. A segment identifier identifies each segment. Thus a virtual address

in segmented address space is a pair  $\langle s, o \rangle$ , where s is the segment identifier or segment selector and o is the offset value within the segment. The offset value starts with value 0 and is bounded by the size of the segment minus one. The segment information is stored in the segment table where each entry contains segment selector, base, limit, protection information and a valid bit. To translate a segmented address the segment table is accessed with the segment identifier to find the physical base address and the limit value. If the segment offset (o) of the given virtual address is within the limit of the selected segment and the protection information allows the requested operation then the offset value (o) is added to the base value of the segment to produce a linear address. The content of the segment table are often cached in a few ISA-defined hardware segment registers to fasten the look up of the segment table.

Modern system that implements segments (e.g., PowerPC and x86), do so on top of paging. Thus the linear address generated by segmentation is further translated to the physical address via paging hardware. However, some very early system like Burrough's B5000 [96] did not use paging and used only segmentation.

Segmentation is useful in sharing of a semantically related memory region among multiple processes. It also helps by allowing each segment to relocated and grown or shrunk independently of other segments. However, due to variability in the segment size, a pure segmented architecture (without paging) can lead to external fragmentation whereby physical memory can be scattered in small unusable holes. Thus most commercial systems lay out segmentation on top of paging. In the following I briefly describe x86's segmentation and its fate in x86-64 architecture.

## 2.4.2.5 Segmentation in x86 (32-bits) and x86-64

The 32-bit x86 architecture allows two modes of operation – the real mode and the protected mode. Real mode of operation is used only during early boot process to initialize hardware and allows only a 20-bit address space (limited to 1MB). In the real mode, x86 implements pure segmentation without paging and each segment is always 64KB long.

During normal operation, an x86 system runs in protected mode. The virtual address consists of 16-bit segment selector (or segment identifier) and a 32-bit of segment offset. The segment selector needs to be in one of the hardware segment registers. The x86 ISA exposes six segment registers: CS, SS, DS, ES, FS, GS. During instruction fetch, the CS or code segment register is selected by default, while SS (stack register) is selected for stack reference. DS register is selected by default for data accesses. However, data access can also use ES, FS or GS by explicit referring them in the program binary. The upper 13 bits of the 16-bit long segment selector read from the relevant segment register are called segment number and is used to index into one of the two segment descriptor tables. There is a local descriptor table (LDT) and global descriptor table (GDT), and a bit in the segment selector decides which of these two segment descriptor tables to index into. In general, segments private to a process are kept in the LDT while global segments reside in the GDT. The segment descriptor entries contain the segment's linear base address as well as limit and protection information. Segment information is cached along with the segment selector in the segment registers for fast lookup. The segment base address is then added to the segment offset to create the linear virtual address.

Table 2-1. Comparison of key virtual memory features across different architectures.

|                          | PowerPC<br>(Power 7)                                   | UltraSPARC (T2)                                                      | ARM-64                                                     | x86-64                                                     |

|--------------------------|--------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------|

| Virtual Address<br>Space | 80-bit segmented-<br>address space on<br>top of paging | 64-bits paged-<br>address space.<br>Lower 44 bits used.              | 64-bits paged-<br>address space.<br>Lower 48 bits<br>used. | 64-bits paged-<br>address space.<br>Lower 48 bits<br>used. |

| Page Table               | Inverted hashed page table.                            | OS-defined flexible structure.                                       | Four-level hierarchical.                                   | Four-level hierarchical.                                   |

| TLB Miss<br>Handling     | H/W page table walker.                                 | H/W looks up TSB.<br>On TSB miss S/W<br>handler walks page<br>table. | H/W page table walker.                                     | H/W page table walker.                                     |

| Page Sizes               | 4KB, 64KB,<br>16MB and 16GB.                           | 8KB, 64KB, 4MB, and 256MB.                                           | 4KB and 64KB.                                              | 4KB, 2MB and 1GB.                                          |

The x86-64 essentially uses flat model without much support for segmentation where CS, SS, DS, ES registers are hardwired to zero. FS and GS registers can still have non-zero base addresses and are sometimes used by modern systems for holding some thread-private information. Thus, in today's x86-64 systems paging is the primary address translation mechanism.

## 2.4.3 Virtual Memory for other ISAs

Hitherto, I have discussed the virtual memory mechanisms as in the x86-64 architecture. However, other ISAs like PowerPC, ARM-64 and SPARC have some important differences in the way they handle virtual memory. In this subsection I will provide a brief discussion on how these other ISAs differ from x86-64.

Table 2-1 provides brief contrast of key virtual memory features of various different ISA with those of x86-64. I discuss more details about these features and ISA in the following.

**PowerPC:** 64-bit Power-PC architecture exposes 80-bit wide segmented virtual address space, which like x86, is implemented on top of paging. Each segments in PowerPC (Power7) is 256 MB or 1TB in size [82]. It uses the top 36 bits of a virtual address to index into a segment descriptor table whose entries can be cached in hardware in a segment-lookaside-buffer.

PowerPC implements a hashed inverted page table, which is an eight-way set-associative software cache structure. On a TLB miss the hardware computes a hash of the virtual address to index into the inverted page table. Due to possible conflict in the hash table the OS also maintains the complete page table in memory. PowerPC supports 4KB, 64KB, 16MB and 16GB page sizes.

ARM-64: ARM supports a flat virtual address space without segmentation. It is very similar to x86-64 and provides a 48-bit virtual address space with kernel occupying the upper half and the user processes the lower half. It implements a four-level hierarchical page table similar to x86-64 [4]. ARM supports 4KB and 64KB page sizes in 64-bit mode. Use of 64KB page size limits the depth of hierarchical page table to two instead of four and restricts the virtual address width to 42 bits. Since use of larger page size alters the page table structure and limits address space size, it is likely that ARM-64 is unable to support mix of page sizes for a given process.

UltraSPARC T2: While SPARC supports a 64-bit address space only the lower 44-bits are used for addressing. The physical address space size is generally 41 bits. The UltraSPARC implements a software-defined page table completely under OS control. It also defines a Translation Storage Buffer (TSB) that resides in system memory. It is a virtually indexed, virtually tagged, direct-mapped software cache of the translation entry. On a TLB miss the hardware first searches the TSB. On a TSB miss an exception is raised to OS to fill the TLB. It supports 8KB, 64KB, 4MB, and 256MB page sizes.

#### 2.5 In this Thesis

In this thesis, I focus primarily on two key problems of current virtual memory implementation: 1) excessive energy dissipation due to frequent TLB lookups and 2) performance overhead due to TLB misses. While rest of the thesis will focus around designs that are employed by x86-64 architectures, the above-mentioned two key challenges of virtual memory are universal across different architectures. For example, to the best of my knowledge all current commercial general-purpose processors looks up the TLB on each memory access and the performance overhead due to TLB misses are widely accepted challenge across architectures other than x86-64 [88,103]. Further, I believe that the techniques proposed in this thesis are applicable irrespective of ISA. In the third piece, I focus on the design trade-offs in TLB implementation if multiple page sizes are to be supported. Our proposal could benefit TLB design employed by recent commercially popular Intel chips.

3

# **Reducing Address Translation Latency**

#### 3.1 Introduction

In this chapter I discuss the *direct segments* proposal that strives to eliminate most of the address translation cost for emerging big memory workloads.

The primary cost of address translation in page-based virtual memory stems from indirection: on each access to virtual memory, a processor must translate the virtual address to a physical address. While address translation can be accelerated by TLB hits, misses are costly, taking up to 10s-100s of cycles [9,83].

To reevaluate the address translation cost and the benefits of decades-old page-based virtual memory in today's context, I focus on an important class of emerging *big-memory* workloads. These include memory intensive "big data" workloads such as databases, key-value stores, and graph algorithms as well as high-performance computing (HPC) workloads with large memory requirements.

My experiments reveal that these big-memory workloads incur high virtual memory overheads due to TLB misses. For example, on a test machine with 96GB physical memory,

graph500 [36] spends 51% of execution cycles servicing TLB misses with 4KB pages and 10% of execution cycles with 2 MB large pages. The combination of application trends—large memory footprint and lower reference locality [31,71]—contributes to high TLB miss rates and consequently I expect even higher address translation overheads in future. Moreover, the trends to larger physical memory sizes and byte-addressable access to storage class memory [77,91] increase address mapping pressure.

Despite these costs, I find big-memory workloads seldom use the rich features of page-based virtual memory (e.g., swapping, copy-on-write and per-page protection). These workloads typically allocate most of the memory at startup in large chunks with uniform access permission. Furthermore, latency-critical workloads also often run on servers with physical memory sized to the workload needs and thus rarely swap. For example, databases carefully size their buffer pool according to the installed physical memory. Similarly, key-value stores such as *memcached* request large amounts of memory at startup and then self-manage it for caching. I find that only a small fraction of memory uses per-page protection for mapping files, for executable code. Nevertheless, current designs apply page-based virtual memory for *all* memory regions, incurring its cost on *every* memory access.

In light of the high cost of page-based virtual memory and its significant mismatch to "big-memory" application needs, I propose mapping part of a process's linear virtual address with a *direct segment* rather than pages. A direct segment maps a large range of contiguous virtual memory addresses to contiguous physical memory addresses using small, fixed hardware: *base, limit* and *offset* registers for each core (or hardware context with multithreading). If a

virtual address V is between the base and limit ( $base \le V < limit$ ), it is translated to physical address V + offset without the possibility of a TLB miss. Addresses within the segment must use the uniform access permissions and reside in physical memory. Virtual addresses outside the segment's range are translated through conventional page-based virtual memory using TLB and its supporting mechanisms (e.g., hardware page-table-walker).

The expected use of a direct segment is to map the large amount of virtual memory that big-memory workloads often allocate considering the size of physical memory. The software abstraction for this memory is called a *primary region*, and examples include database buffer pools and in-memory key-value stores.

Virtual memory outside a direct segment uses conventional paging to provide backward compatibility for swapping, copy-on-write, etc. To facilitate this, direct segments begin and end on a base-page-sized boundary (e.g., 4KB), and may dynamically shrink (to zero) or grow (to near physical memory size). While doing so may incur data-movement costs, benefits can still accrue for long-running programs.

Compared to past segmentation designs, direct segments have three important differences. It (a) retains a standard linear virtual address space, (b) is not overlaid on top of paging, and (c) co-exists with paging of other virtual addresses. Compared to large-page designs, direct segments are a one-time fixed-cost solution for any size memory. In contrast, the size of large pages and/or TLB hierarchy must grow with memory sizes and requires substantial architecture, and/or operating system and applications changes. Moreover, being a cache, TLBs

rely on access locality to be effective. In comparison, direct segments can map arbitrarily large memory sizes with a small fixed-size hardware addition.

The primary contributions of this chapter of the dissertation are:

- I analyze memory usage and execution characteristics of big-memory workloads, and show why page-based virtual memory provides little benefit and high cost for much of memory usage.

- I propose *direct-segment* hardware for efficient mapping of application-specified large *primary regions*, while retaining full compatibility with standard paging.

- I demonstrate the correctness, ease-of-use and performance/efficiency benefits of the direct segments proposal.

# 3.2 Big Memory Workload Analysis

I begin with a study of important workloads with big-memory footprints to characterize common usage of virtual memory and identify opportunities for efficient implementations. The study includes the following three aspects:

• *Use of virtual memory*: I study what virtual memory functionalities are used by such big-memory workloads;

Table 3-1. Test machine configuration.

|              | Description                                                                                                               |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------|--|--|

| Processor    | Dual-socket Intel Xeon E5-2430 (Sandy Bridge), 6 cores/socket, 2 threads/core, 2.2 GHz                                    |  |  |

| L1 DTLB      | 4KB pages: 64-entry, 4-way associative;<br>2MB pages: 32-entry 4-way associative;<br>1GB pages: 4-entry fully associative |  |  |

| L1 ITLB      | 4KB pages: 128-entry, 4-way associative;<br>2MB pages: 8-entry, fully associative                                         |  |  |

| L2 TLB (D/I) | 4 KB pages: 512-entry, 4-way associative                                                                                  |  |  |

| Memory       | 96 GB DDR3 1066MHz                                                                                                        |  |  |

| os           | Linux (kernel version 2.6.32)                                                                                             |  |  |

- *Cost of virtual memory*: I measure the overhead of TLB misses with conventional page-based virtual memory;

- *Execution environment*: I study common characteristics of the execution environment of big-memory workloads.

Table 3-1 describes the test machine for the experiments.

Table 3-2 describes the workloads used in the study. These applications represent important classes of emerging workloads, ranging from in-memory key-value stores (memcached), web-scale large relational databases (MySQL), graph analytics (graph500) and supercomputing (NAS parallel benchmark suite). Memcached is used by many popular websites like YouTube, Wikipedia, Flickr, and Craigslist [65]. MySQL is an open-source relational-database running TPCC workload. IDC estimates that relational database market to be worth nearly 34 billion USD in 2011 [42]. graph500 is created by a group of fifty researchers and professionals from the industry and the academic to create representative workloads that accesses

Table 3-2. Workload descriptions.

| graph500         | Generation, compression and breadth-first search of large graphs.<br>http://www.graph500.org/                               |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|

| memcached        | In-memory key-value cache widely used by large websites (e.g., in Facebook).                                                |  |  |

| MySQL            | MySQL with InnoDB storage engine running TPC-C (2000 warehouses).                                                           |  |  |

| NPB/BT<br>NPB/CG | HPC benchmarks from NAS Parallel Benchmark Suite. http:// nas.nasa.gov/publications/npb.html                                |  |  |

| GUPS             | Random access benchmark defined by the High Performance Computing Challenge. http://www.sandia.gov/~sjplimp/algorithms.html |  |  |

large graphs [36]. Graph algorithms, especially those on very large graphs, are gaining importance due to emergence of social media where social connections often represented as graphs. Further, I also studied the *GUPS* micro-benchmark designed by HPC community to stress-test random memory access in high-performance computing settings.

#### 3.2.1 Actual Use of Virtual Memory

**Swapping.** A primary motivation behind the invention of page-based virtual memory was *automatic* management of *scarce* physical memory without programmer intervention [26]. This is achieved by swapping pages in and out between memory and secondary storage to provide the illusion of much more memory than is actually available.

I hypothesize that big-memory workloads do little or no swapping, because performance-critical applications cannot afford to wait for disk I/Os. For example, Google observes that a subsecond latency increase can reduce user traffic by 20% due to user dissatisfaction with higher latency [54]. This drives large websites such as Facebook, Google, Microsoft Bing, and Twitter

to keep their user-facing data (e.g., search indices) in memory [20]. Enterprise databases and inmemory object-caches similarly exploit buffer-pool memory to minimize I/O. These memorybound workloads are therefore either sufficiently provisioned with physical memory for the entire dataset or carefully sized to match the physical memory capacity of the server.

I examine this hypothesis by measuring the amount of swapping in these workloads with the *vmstat* Linux utility. As expected, I observe *no swapping activity*, indicating little value in providing the capability to swap.

**Memory allocation and fragmentation:** Frequent allocation and de-allocation of memory in various sizes can leave holes in physical memory that prevent subsequent memory allocations, called external fragmentation. To mitigate such external fragmentation, paging uses fixed (page-sized) allocation units.

Big-memory workloads, on the other hand, rarely suffer from OS-visible fragmentation because they allocate most memory during startup and then manage that memory internally. For example, databases like *MySQL* allocate buffer-pool memory at startup and then use it as a cache, query execution scratchpad, or as buffers for intermediate results. Similarly, *memcached* allocates space for its in-memory object cache during startup, and sub-allocates the memory for different sized objects.

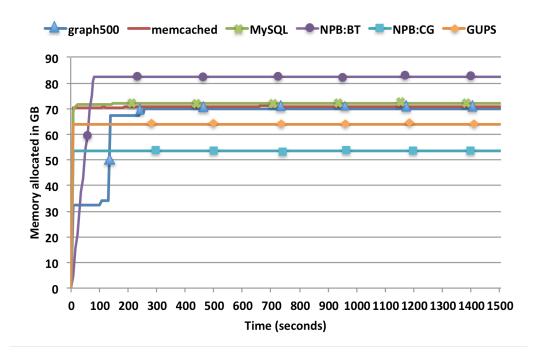

Figure 3-1. Memory allocated over time by workloads.

I corroborate this behavior by tracking the amounts of memory allocated to a workload over its runtime. I use Linux's *pmap* utility [55] to periodically collect total allocated memory size for a given process. Figure 3-1 shows the allocated memory sizes in 5-second intervals over 25 minutes of execution for each workload on the test machine described in Table 3-1.